# Advanced sensors and electronics characterisation

Challenges of HEP for tracking and vertexing in extreme conditions of particles rates and radiation

> L.Demaria , N. Bartosik (INFN Torino), E.Migliore, M. Grippo. F.Luongo (Universita' and INFN Torino)

Context & Principles : challenges and goals achieved

Lab part-1 : front-end ectronics testing / characterization with probe-station

Lab part-2 : pixel module verification using an X-ray machine

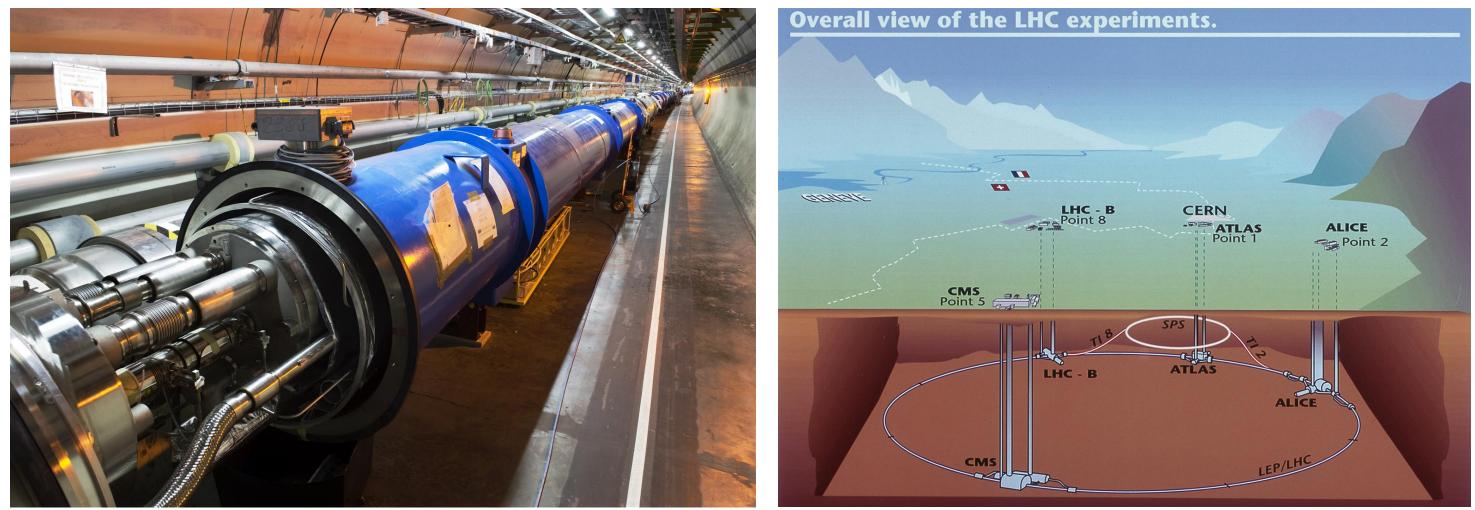

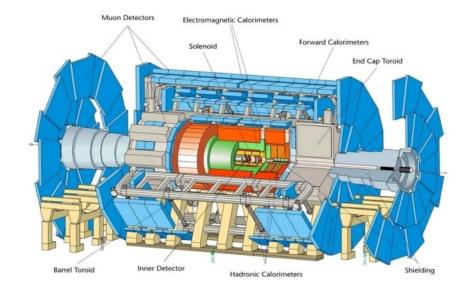

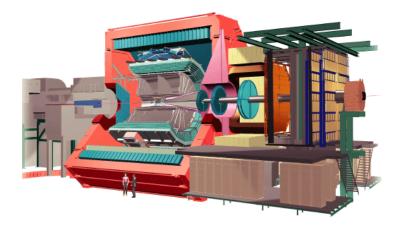

- Biggest and powerful particle accelerator in the world

- pp collider 26 Km of length

- 13 TeV energy

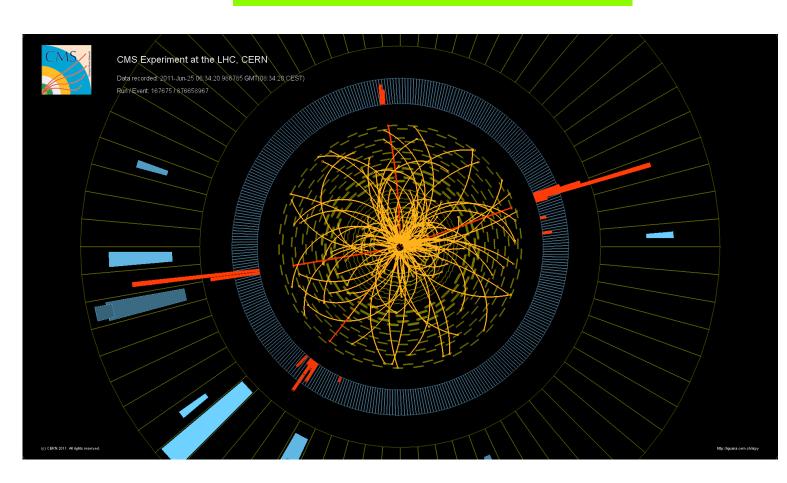

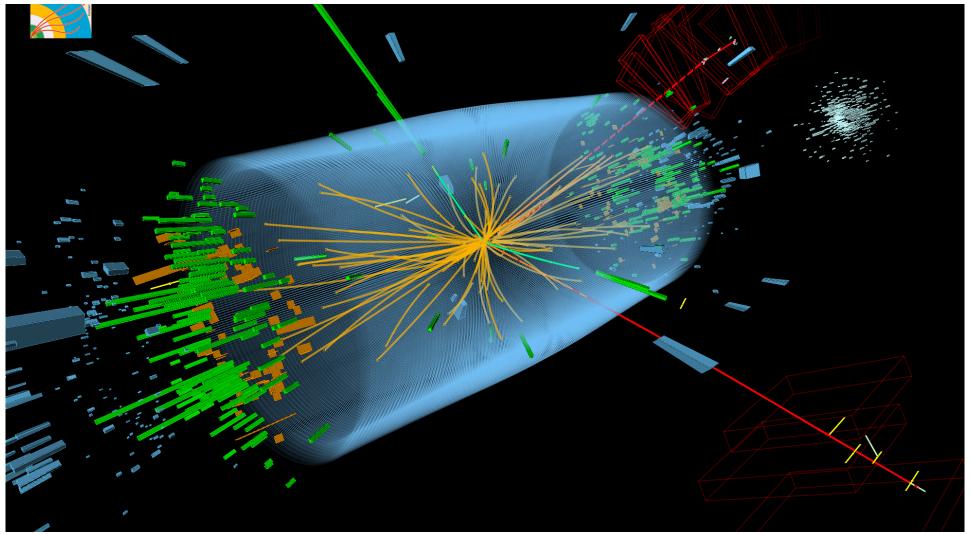

- Large amount of particle collisions

- 2376 bunches each made of 10<sup>11</sup> protons at light velocity

- 25 collisions every 25ns  $\bullet$

- Four large experiments to study particle physics,

- two for new particles, new phenomena

- one b-particle physics

- one specialised on ion-ion collisions (qqg plasma)

## LHC Upgrade to HL\_LHC

#### NOW @ LHC

- Experiments: taking data at higher L1-Trigger rate

- Read-out data increase > **x3** particles, **x7** trigger

- ALL THIS to make precision study to Higgs sector and search for new phenomena

#### After year 2028

## • <u>HL\_LHC accelerator</u>: new frontier for particle

pp-collisions at >3 times LHC; 200 pp collisions at the same time !

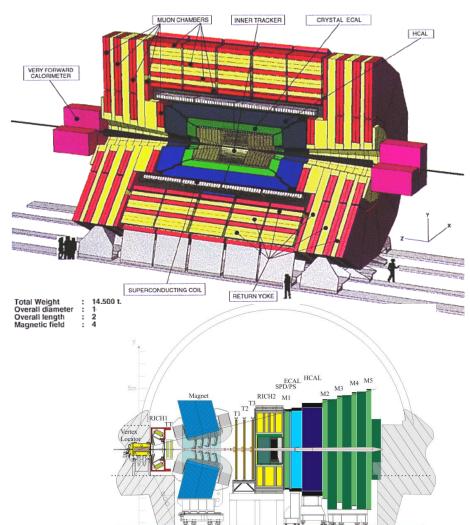

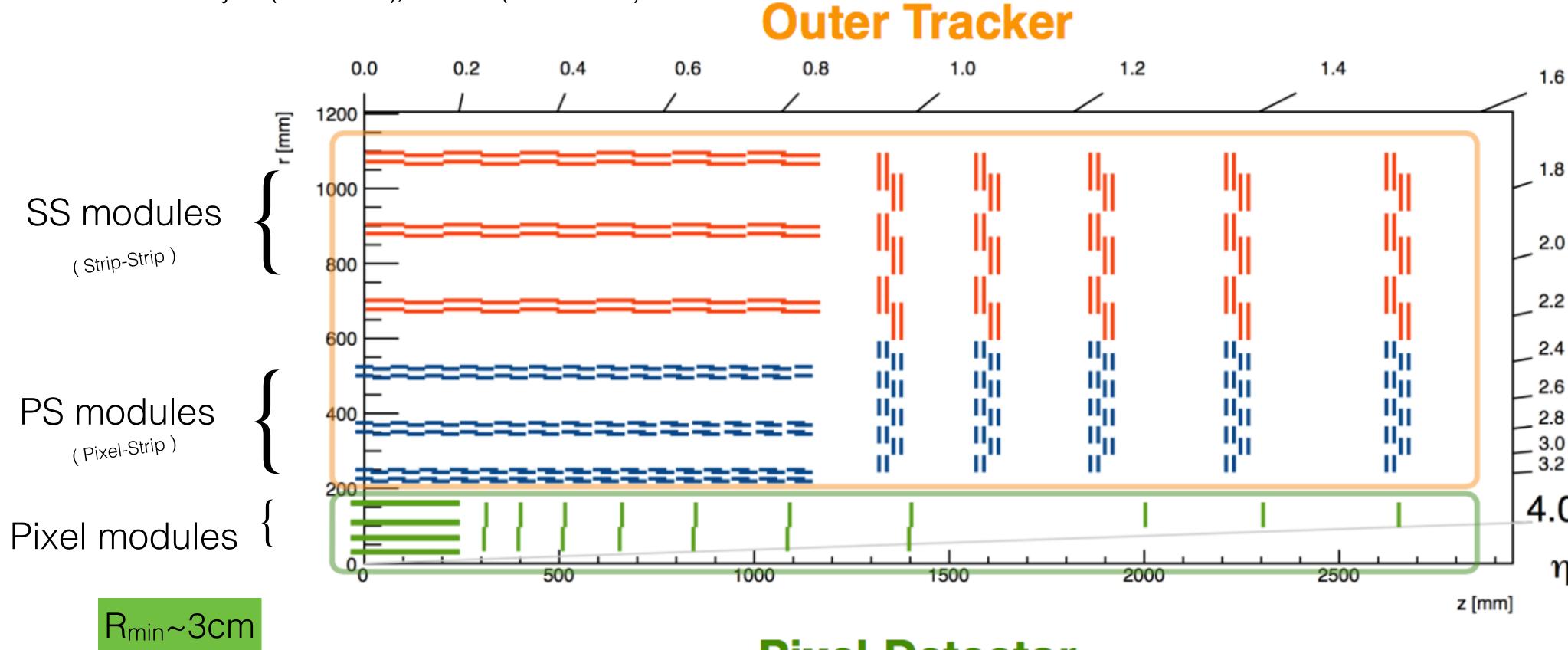

### Tracker Detector for HL\_LHC

- OUTER TRACKER : momentum resolution, tracking trigger (up to  $|\eta|$  =2,4)

- 6 'double-sensor' in barrel (10 single now); 5 double sensors disks (9 now)

- **PIXEL DETECTOR** : tracking seeding, vertex reconstruction, tracking extension

- 4 barrel layers (as Phase-1); 10 disks (3 in Phase-1)

#### **Pixel Detector**

1.6

1.8

2.0

2.4 2.6 2.8 3.0

\_ <sup>3.2</sup> 4.0

η

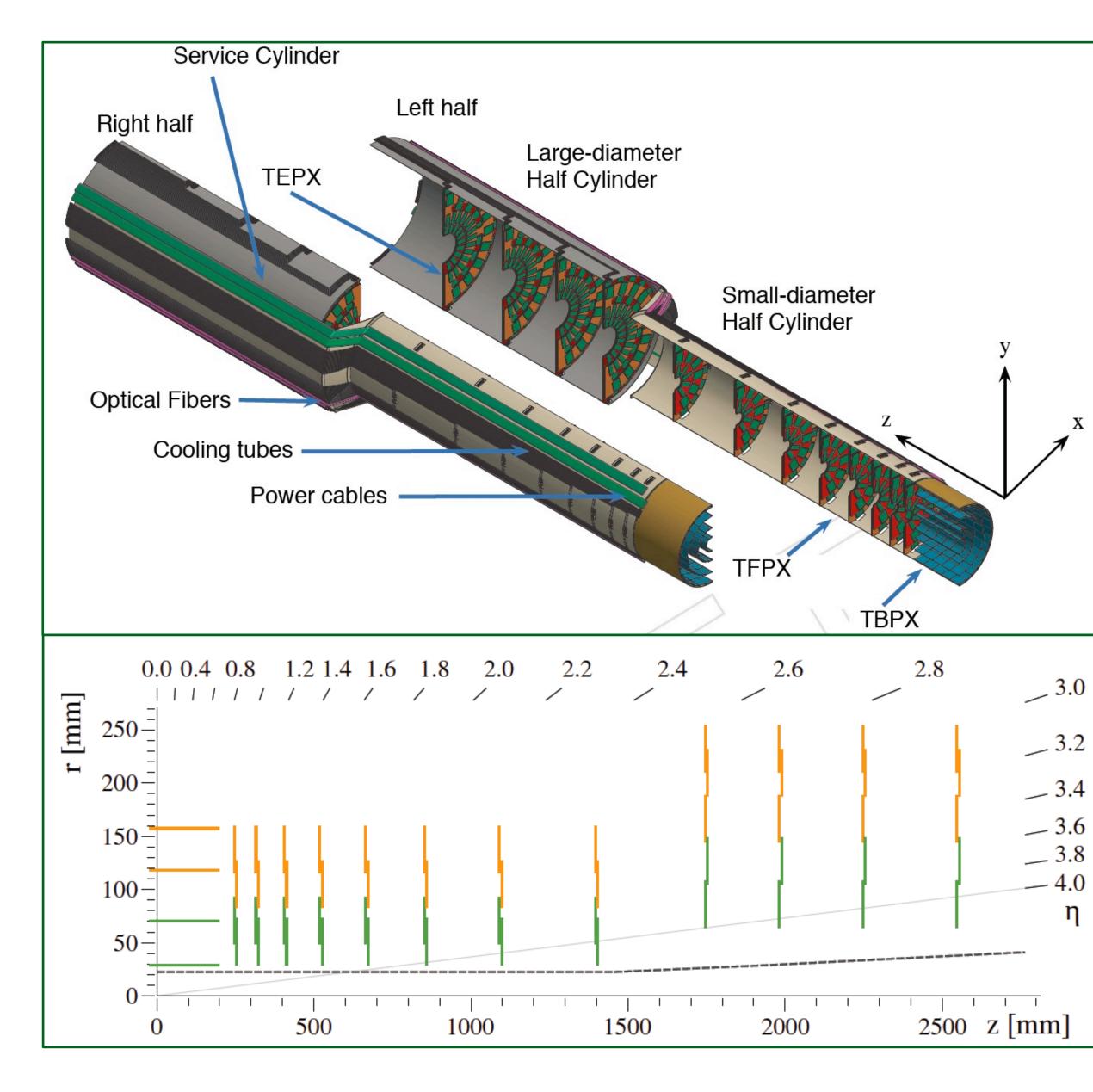

### **Pixel Detector**

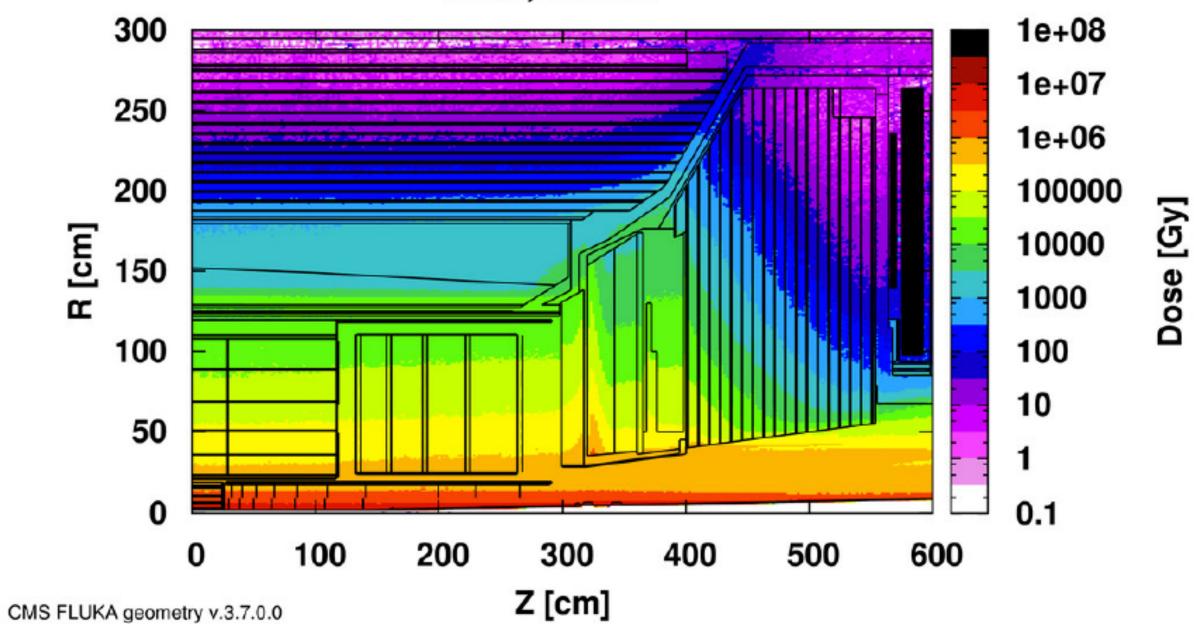

Dose, 3000 fb<sup>-1</sup>

The most demanding layers are the inner ones, at  $\sim$ 3 and 7 cm:

- particle flux

- radiation dose

to mantain same pixel occupation a higher granularity is required (x5). LHC area is  $\sim 13000 \text{um}^2$  therefore pixel cell should be reduced at  $\sim 2650 \text{ um}^2$

#### **Pixel Detector at HL\_LHC : ReadOut Electronics specs**

#### **Requirements from HL\_LHC experiments**

Small pixels: 50x50um<sup>2</sup> Large chips: 2cm x 2cm (~1 billion transistors) Hit rates: 2 GHz/cm<sup>2</sup> Signal Digitisation : 4-5 bit Radiation: 1Grad, 10<sup>16</sup> n/cm<sup>2</sup> (unprecedented)

up to 1MHz with 12.5us latency Trigger: (~100x buffering and readout) Low power - Low mass systems

Data readout : up to 4-5 Gbs/s TRIGGER Latency up to 12.5us (x3) ==> deeper storage buffer

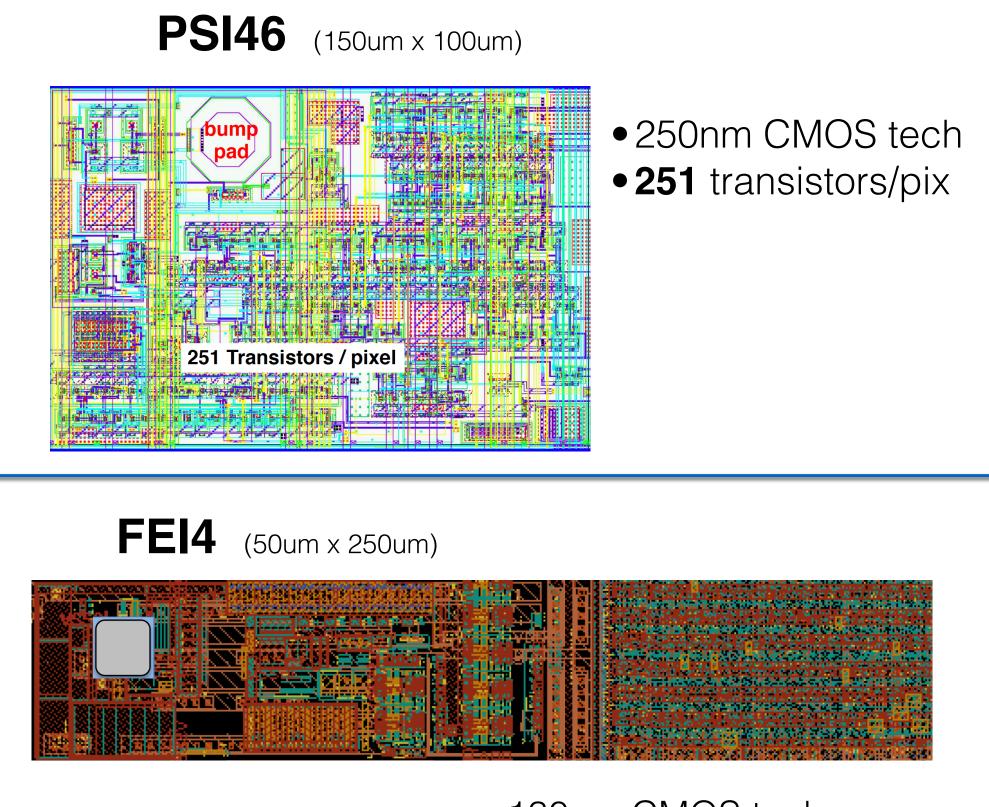

### **Pixel ReadOut chip: State of the Art**

| PARAMETER or<br>FEATURE | 1st generation<br>LHC phase 0       | 2nd generation<br>LHC Phase 1       | <b>3rd generation<br/>LHC Phase 2</b> |

|-------------------------|-------------------------------------|-------------------------------------|---------------------------------------|

| CMOS technology         | 250nm                               | 250nm / 130nm                       | 65nm                                  |

| Max Particle Flux       | ~50 MHz/cm <sup>2</sup>             | ~200 MHz/cm <sup>2</sup>            | $\sim$ 750 MHz/cm <sup>2</sup>        |

| Max Pixel Flux          | 200 MHz/cm <sup>2</sup>             | 600 MHz/cm <sup>2</sup>             | <sup>3</sup> GHz/cm <sup>2</sup>      |

| Rad. Hardness           | 1.5 MGy                             | 3.5 MGy                             | 10 MGy                                |

| Pixel Dimension         | $100 \text{x} 150 \ \mu \text{m}^2$ | $100 \text{x} 150 \ \mu \text{m}^2$ | $25 \times 100 \ \mu m^2$             |

|                         | $50x400 \ \mu m^2$                  | $50x250 \mu m^2$                    | $50 \times 50$ $\mu m^2$              |

| Signal Threshold        | 2500-3000 e <sup>-</sup>            | 1500-2000 e <sup>-</sup>            | < 1000 e                              |

| L1 Trigger Latency      | 2-3 µs                              | <b>4-6 μs</b>                       | 10-20 μs                              |

| L1 Trigger Rates        | 100 KHz                             | ~100 KHz                            | 200-1000 kHz                          |

| ASIC side               | $\sim 1 \text{ cm}^2$               | $\sim 4 \text{ cm}^2$               | $1-4 \text{ cm}^2$                    |

| Hit memory per          | 0.1 Mb                              | 1 Mb                                | >16 Mb                                |

| chip                    |                                     |                                     |                                       |

| Chip output             | ~40 Mb/s                            | ~320 Mb/s                           | ~3 Gb/s                               |

| bandwidth               |                                     |                                     |                                       |

| Power Budget            | $\sim 0.3 \text{ W/cm}^2$           | $\sim 0.3 \text{ W/cm}^2$           | $<0.6 \text{ W/cm}^2$                 |

7

CMS

ATLAS

#### Increasing granularity from Present to HL\_LHC

#### **PRESENT DETECTORS for pp@LHC**

- 130nm CMOS techn

- ~2500 transistors/pix

- ~0,5 trans/um<sup>2</sup>

innovation allow to decrease of a factor ~5 the pixel size either improving performance (threshold, speed, data rates...)

65nm CMOS technology allows to design a smaller pixel capable to sustain extreme particle fluxes and long latencies

(50um x 50um)

- 65nm CMOS tech

- ~2500 transistors/pix

- ~2 trans/um<sup>2</sup>

50% of area to digital

CMS õ S A for

**12mm<sup>2</sup>**

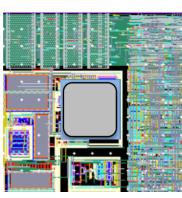

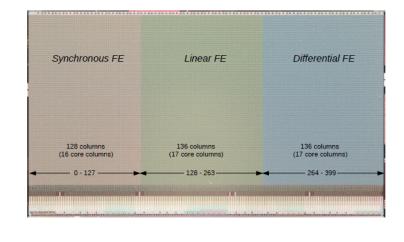

#### New generation pixel readout chip in 65nm CMOS technology developed by RD53 collaboration

- INFN CHIPIX65 project (dimostratore: 2016) 64x64 pixel matrix lacksquare

- RD53 Collaboration: RD53A large size demonstrator: (August-2017) 400x192 pixel  $\bullet$ matrix

- RD53 Collaboration: prototype and final version of Atlas and CMS chips ~400x400 pixel matrix

**2**cm<sup>2</sup>

**<u>RD53 Collaboration</u>** joint effort from ATLAS and CMS Institutes to develop readout chips for the HL-LHC pixel detectors 24 institutes, started in 2013 -**MAJOR** contribution from INFN

**RD53B-ATLAS** (ItkPix1) • March **2020**

~4cm<sup>2</sup>

**RD53B-CMS** (CROCv1) • June **2021**

**RD53C-ATLAS** (ItkPix2) • March **2023**  **RD53C-CMS** (CROCv2) • fall **2023**

| 1 |      |      |           |   |

|---|------|------|-----------|---|

|   |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           | - |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 1 |      |      |           |   |

| 4 |      |      |           |   |

| ٩ |      |      |           |   |

| ٩ |      |      |           |   |

| ٩ |      |      |           |   |

| 4 |      |      |           |   |

| 4 |      |      |           |   |

| 4 |      |      |           |   |

| 4 |      |      |           |   |

| 4 |      |      |           |   |

| 4 |      |      |           |   |

| 4 |      |      |           |   |

| 4 |      |      |           |   |

| 1 |      |      |           |   |

| I |      |      |           |   |

| d |      |      |           |   |

| d |      |      |           |   |

|   |      |      |           |   |

|   |      |      |           |   |

|   | 1 10 |      | 1.0       | 1 |

|   |      | 1000 | <br>11-94 | 1 |

|   |      |      |           |   |

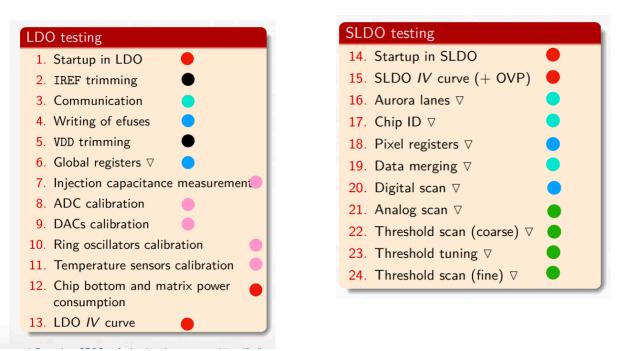

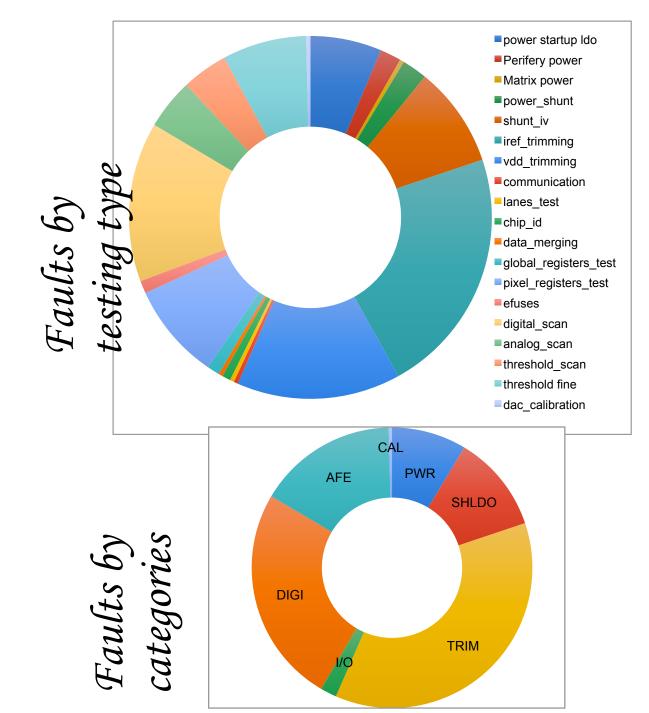

## Laboratory part one

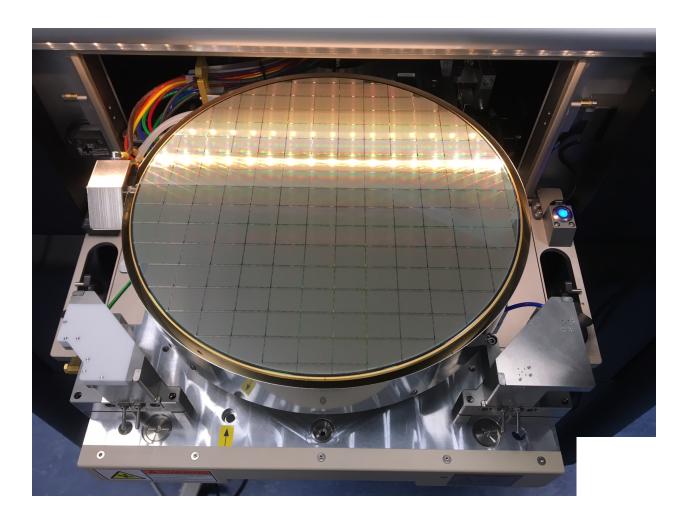

- Fresh from the Fab ! see how ASIC arrives from industry. 12" wafer to be tested and then sent for processing and bump deposition - You will be using a C-ROC wafer

- You will enter a clean room: learn how to wear and behave...

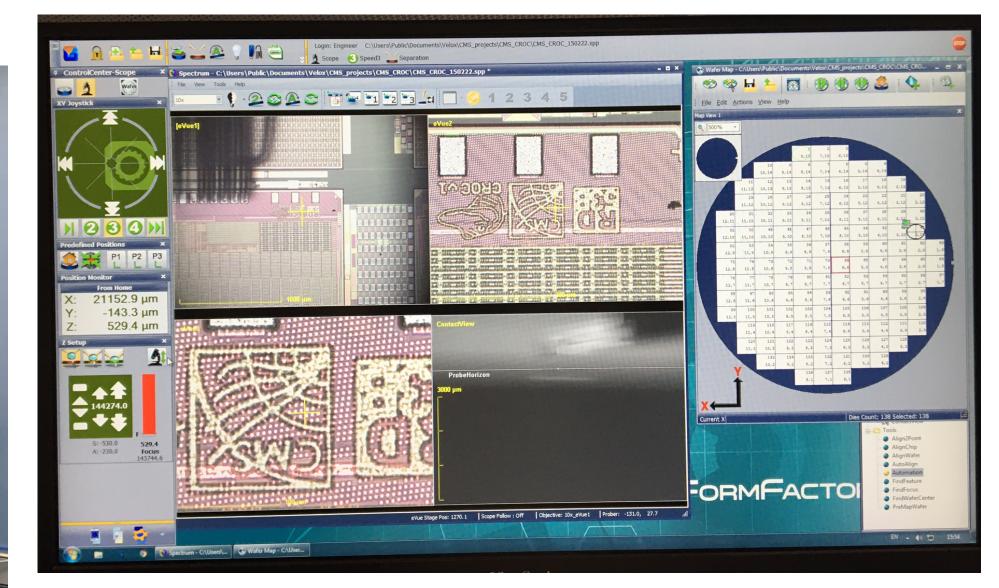

- Look to a Pixel Readout Chip from a Probestation and navigate precisely on a wafer from chip to chip !

- How to do wafer level testing: you will be testing a real chip

- You will perform the analysis to do Quality assurance and decide if the chip is good or not, looking how you properly calibrated the chip

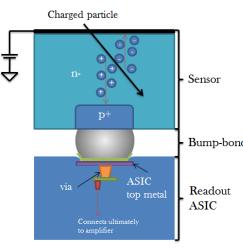

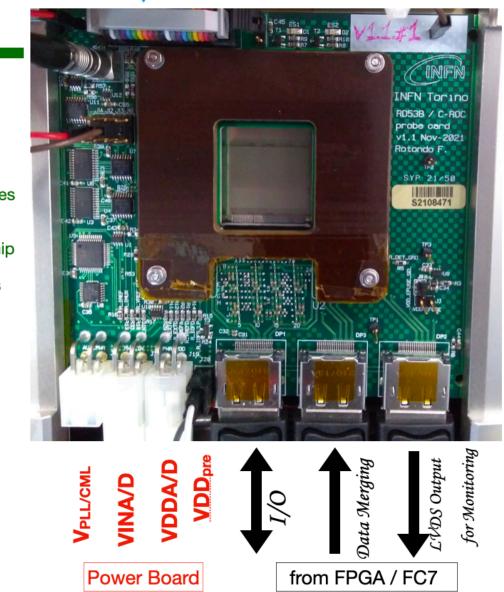

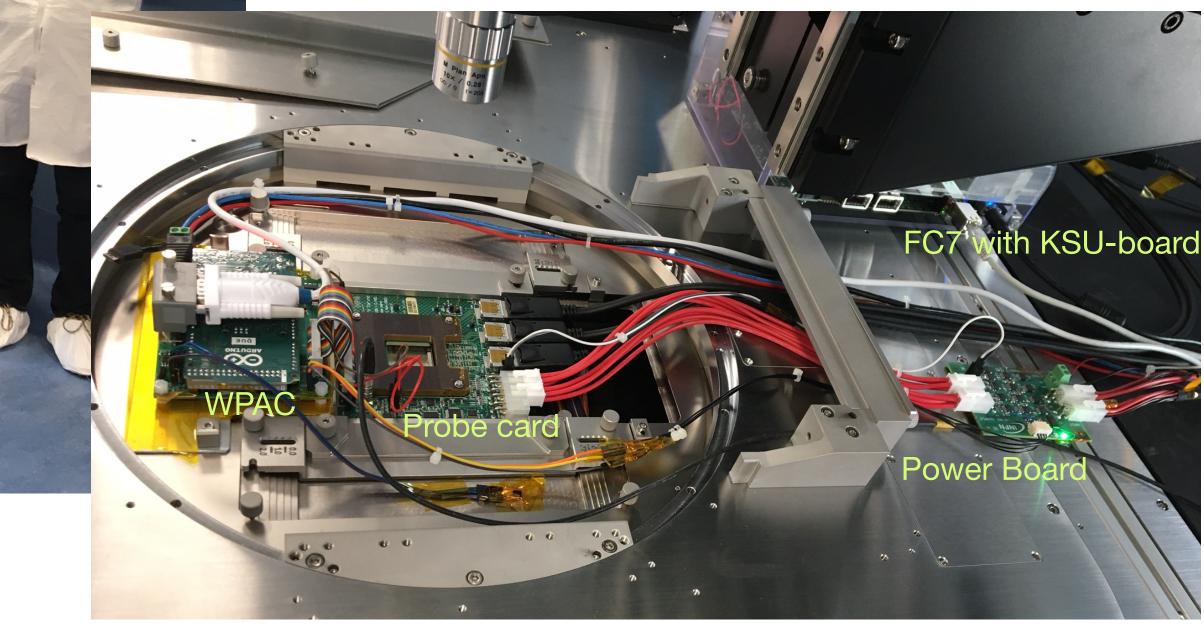

connection to the 184 chip pads via needles: a probe-card allow to power, make I/O, monitor the chip under test (DUT)

probes: 100um pitch

Hybrid technology: chip on wafer has to be processed for UBM and bump deposition

Analog Multiplexer c probe card to of many voltag nonitored by CROC VMUX and sensina ch

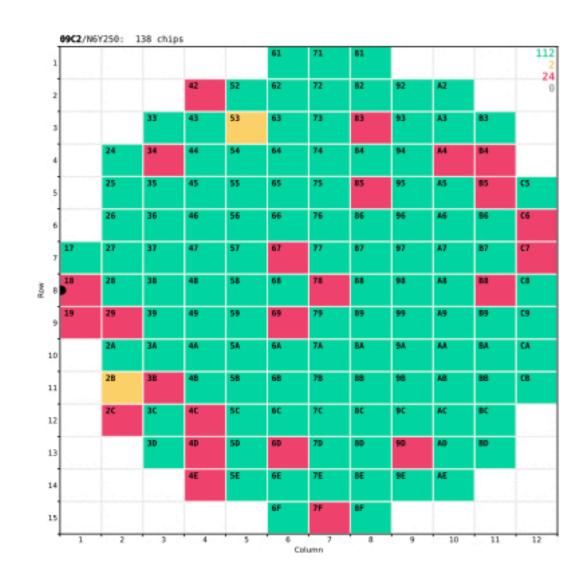

## Wafer Probing setup@Torino

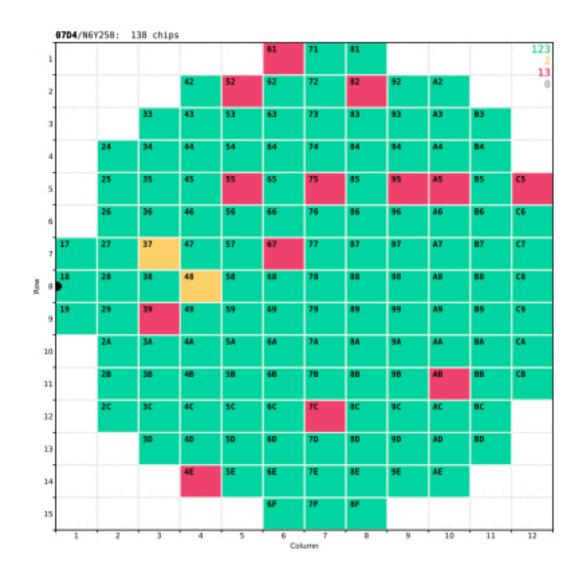

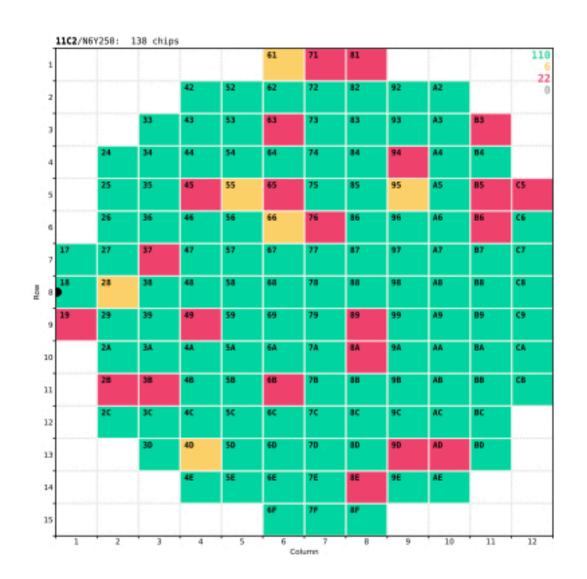

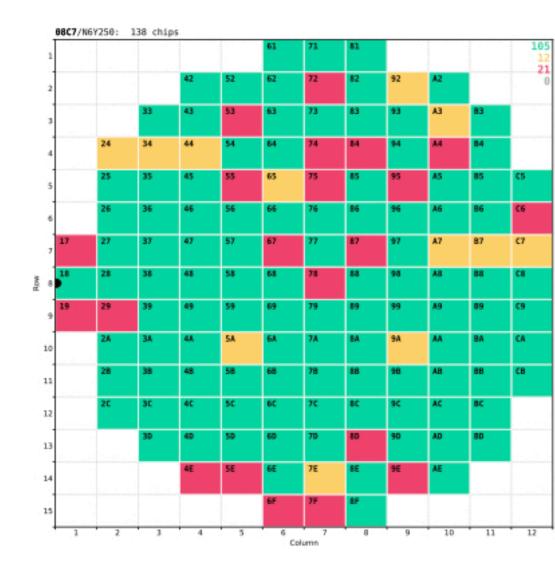

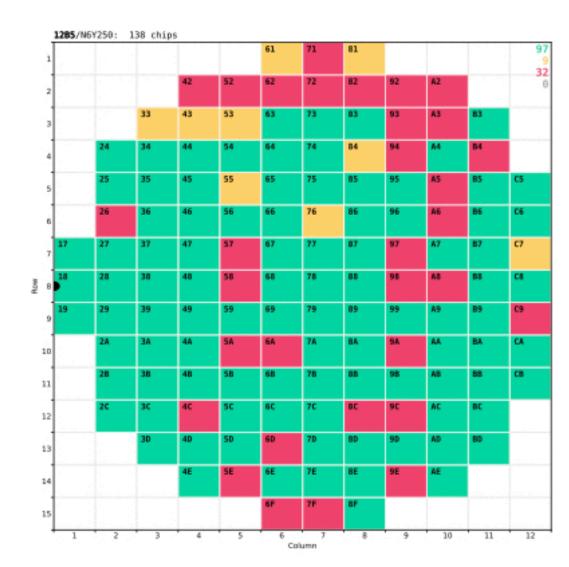

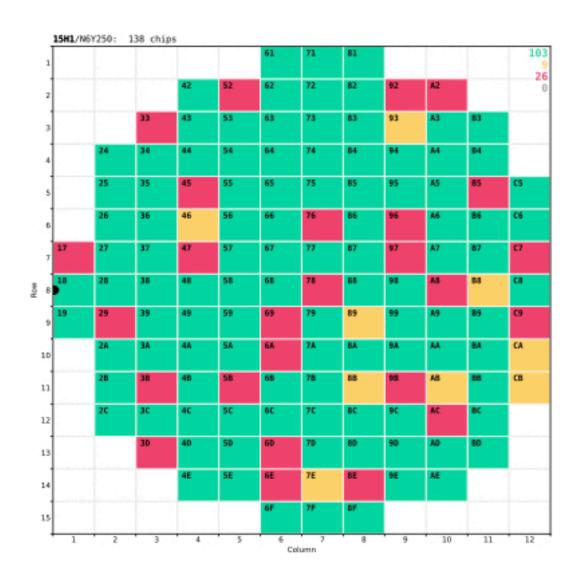

• A probe-station allow to safely travel through all the 138 chips and test them

11

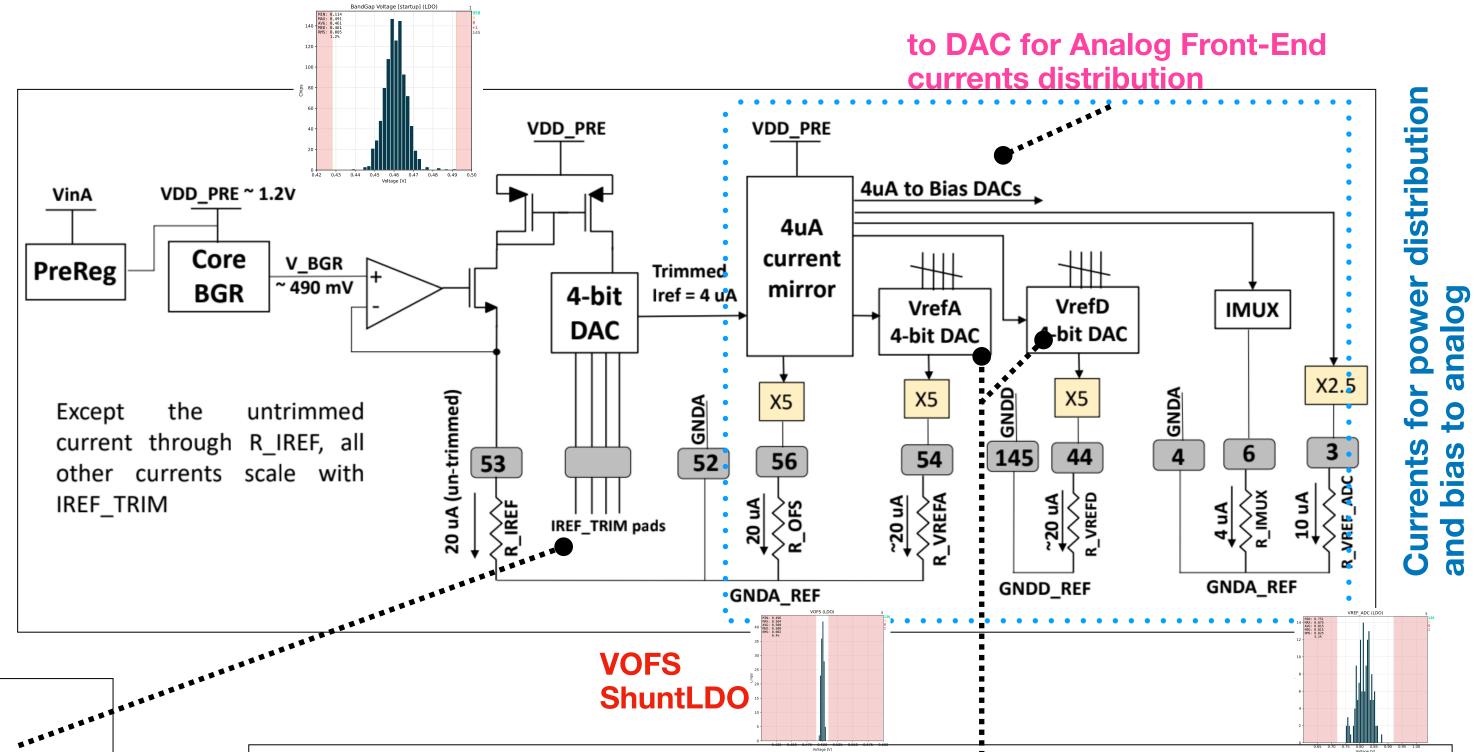

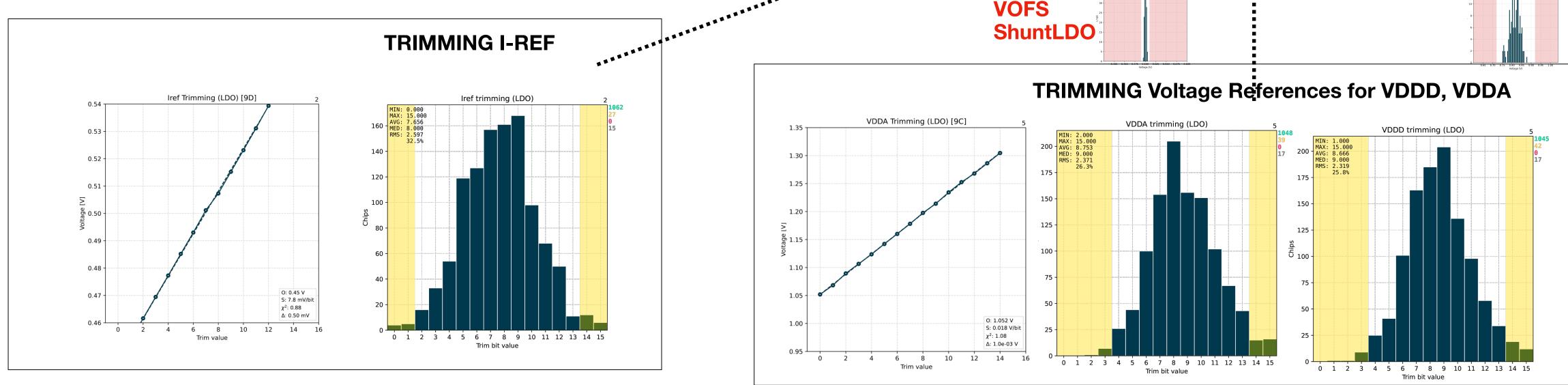

## **C-ROC Trimming(s)**

Starting from a preregulator and a BandGap, in order to get calibrated Voltage and currents distribution a double trimming is needed

1. Trimming of current reference (from ext-pad)

1.defines chip wire-bonding at module construction

2. Trimming of VDDD, VDDA (from configuration) registers)

12

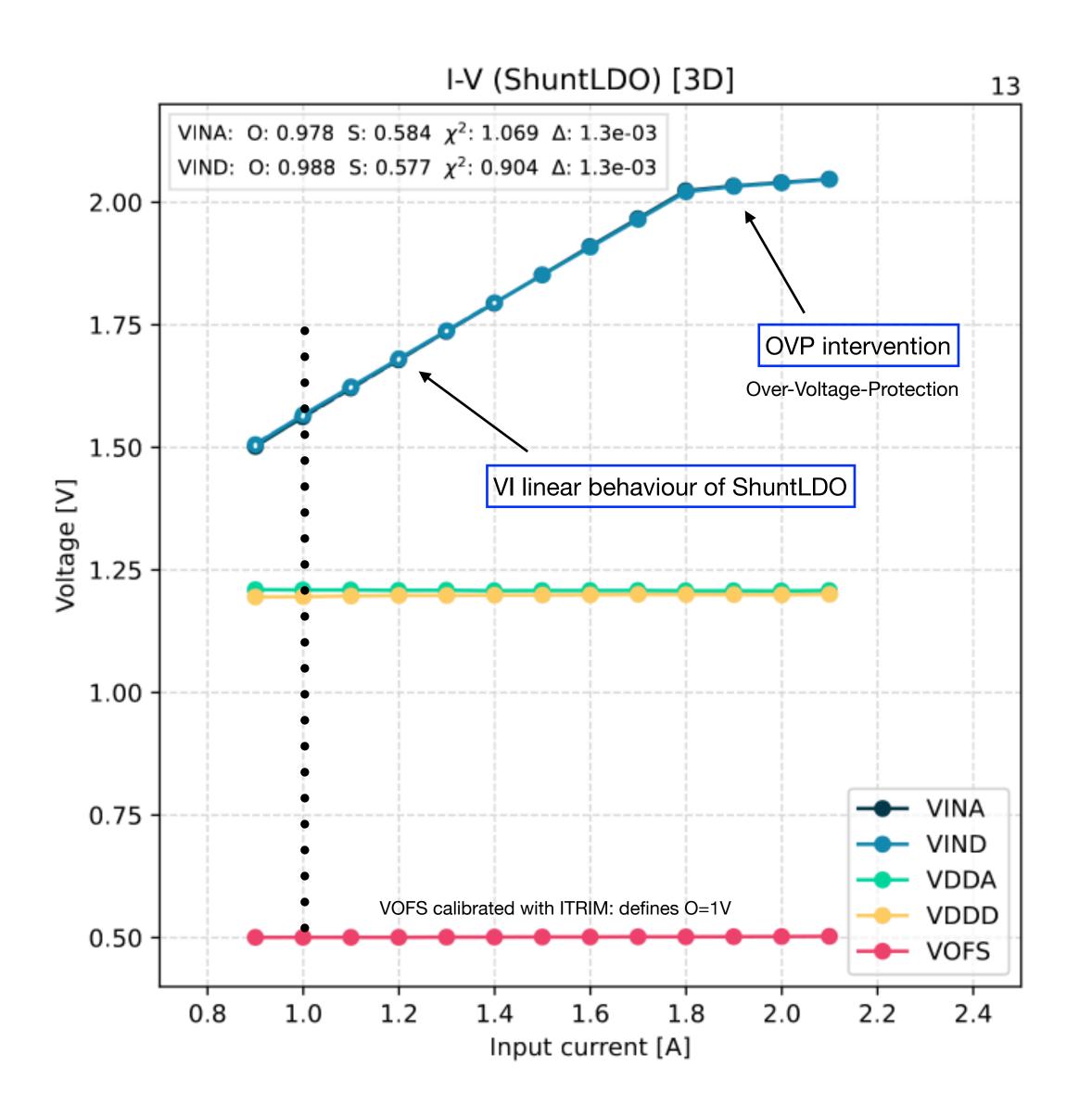

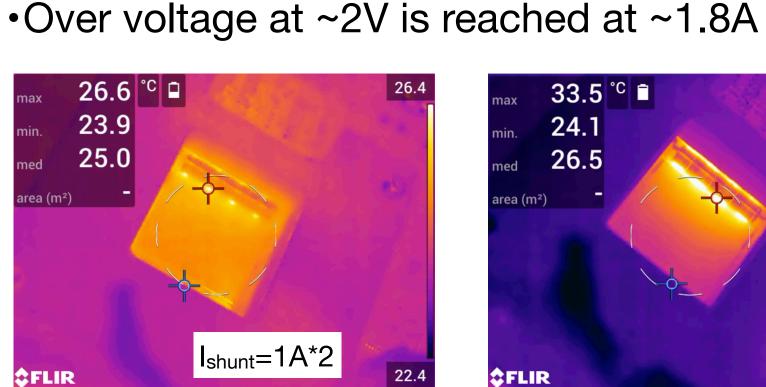

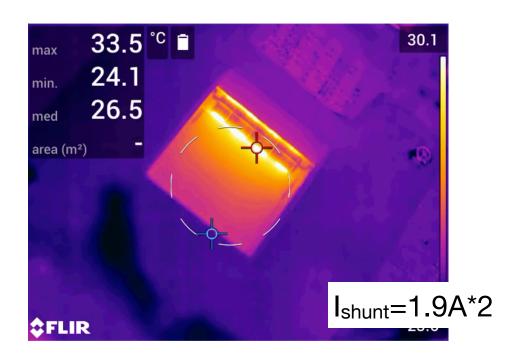

## The power regulator ShuntLDO IV

Fundamental for serial powering of modules: fixed current provide power to CROC, statisfies its consumption request regardless to current variation - and remaining current goes to a shunt resistor

•NB: the current is x-axis is for a single power domain, analog and digital are independent here. This allow to characterise each ShuntLDO

Chip is configured to operation values, therefore 800mA goes to ACB+Matrix(ana) and 668mA goes to DCB+Matrix(dig)

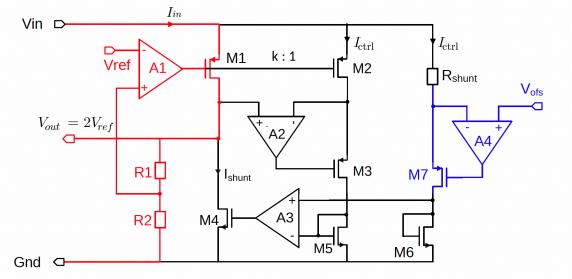

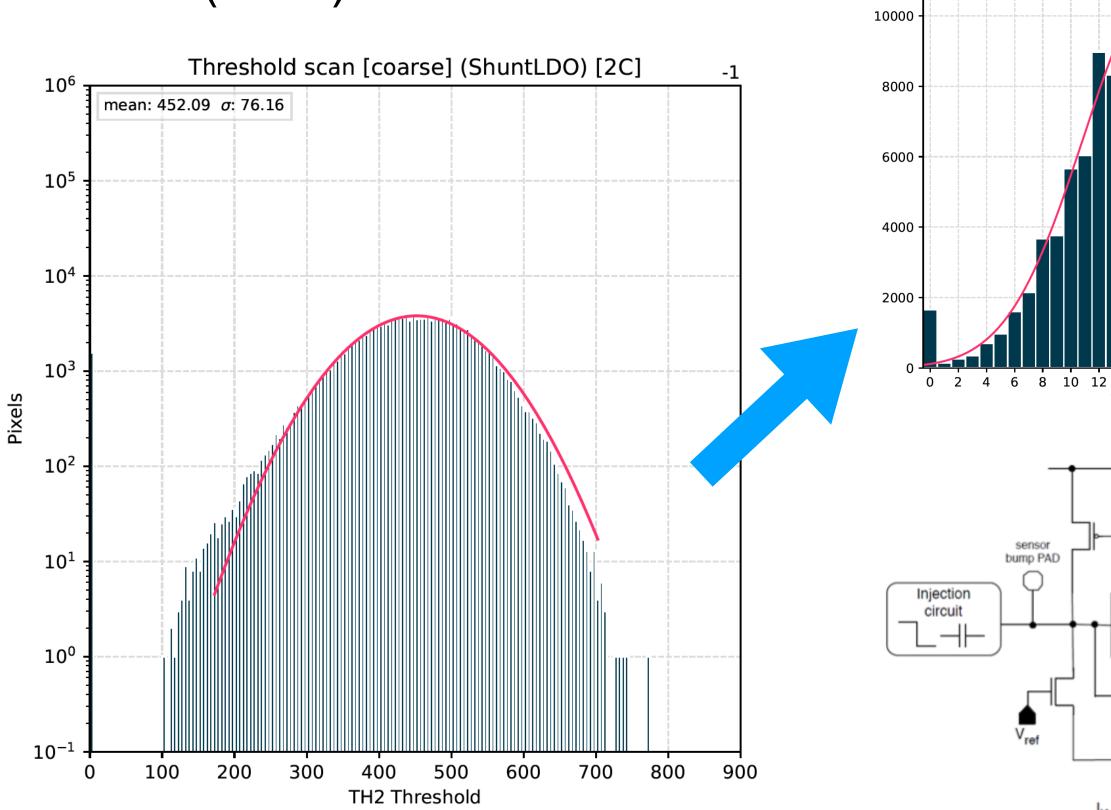

## Threshold tuning of analog front-end

made ...

mean: 16.76 σ: 5.39

12000

From a threshold dispersion between different pixels of 400e- (RMS) ....

#### ...a per-pixel calibration (5-bits) is

#### threshold among Threshold tuning [TDAC] (ShuntLDO) [2C] 145152 pixels with 50e- RMS ! Threshold scan [fine] (ShuntLDO) [2C] $10^{6}$ mean: 448.69 *σ*: 10.02 10<sup>5</sup> 104 $10^{3}$ 8 10 12 14 16 18 20 22 24 26 28 3 ixels 10<sup>2</sup> threshold $10^{1}$ tuning DAC V<sub>out,csa</sub> Vout,comp 10<sup>0</sup> $10^{-1}$ 100 200 300 400 500 600 700 800 900 0 TH2 Threshold

... obtaining the same

## Laboratory part two

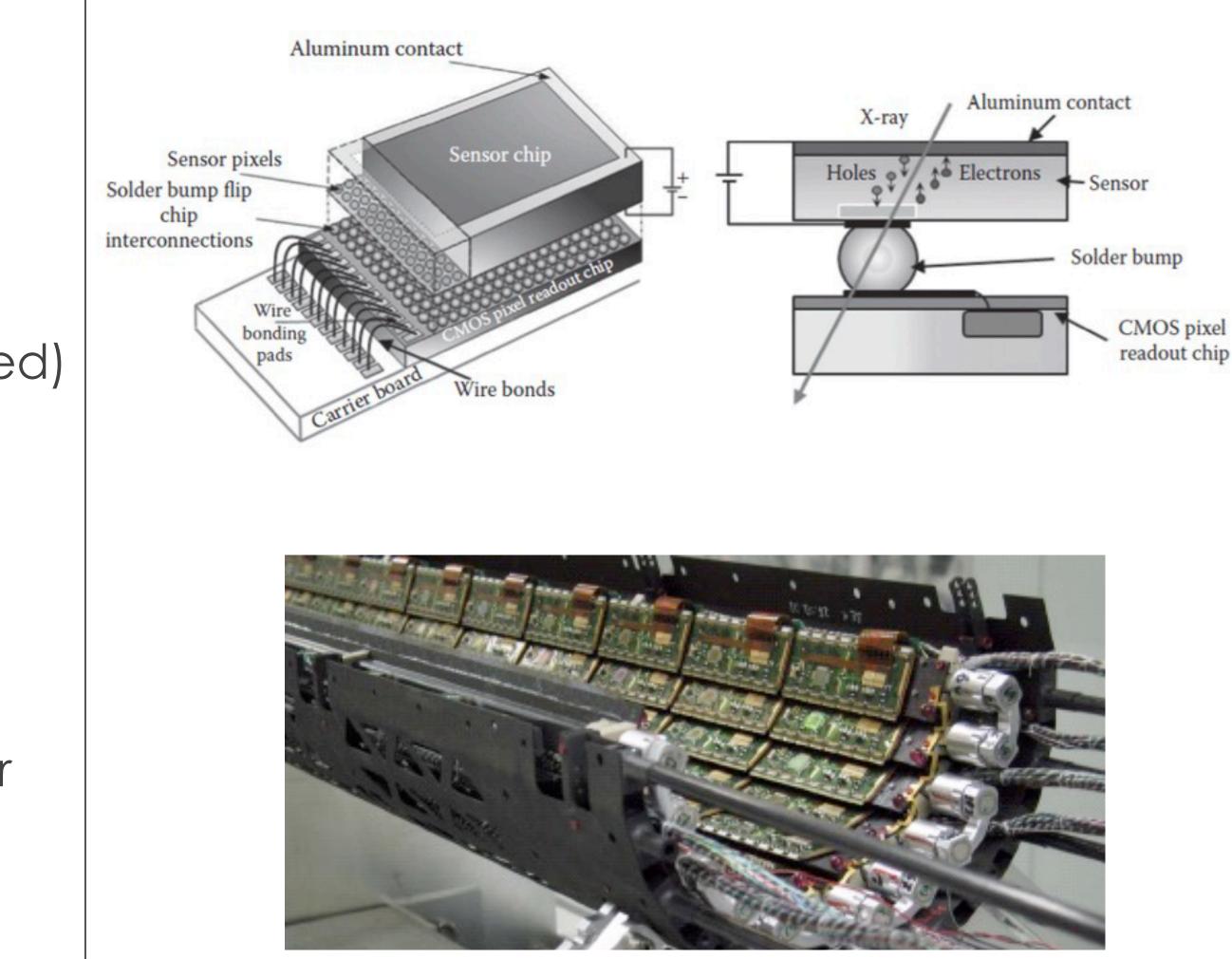

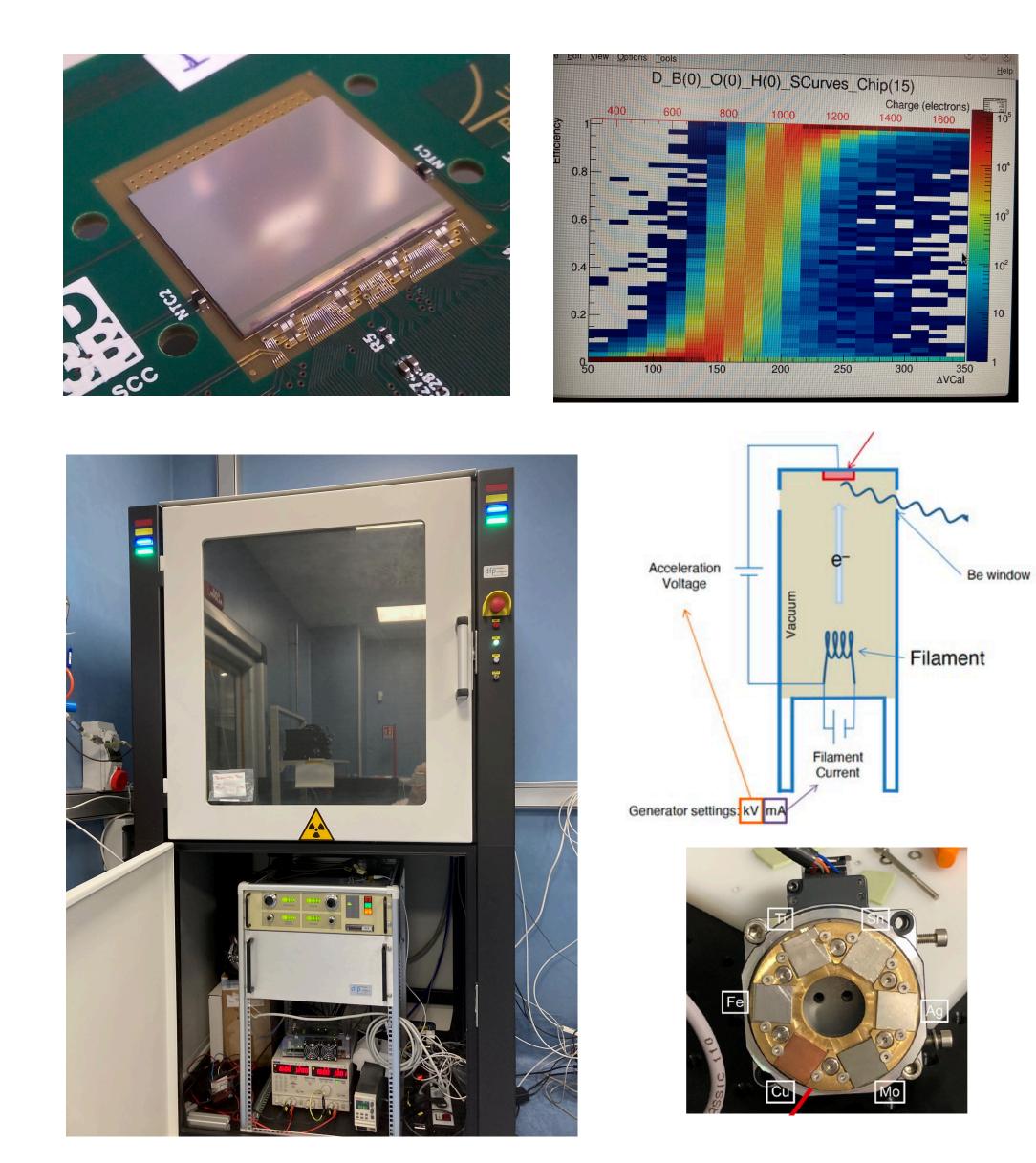

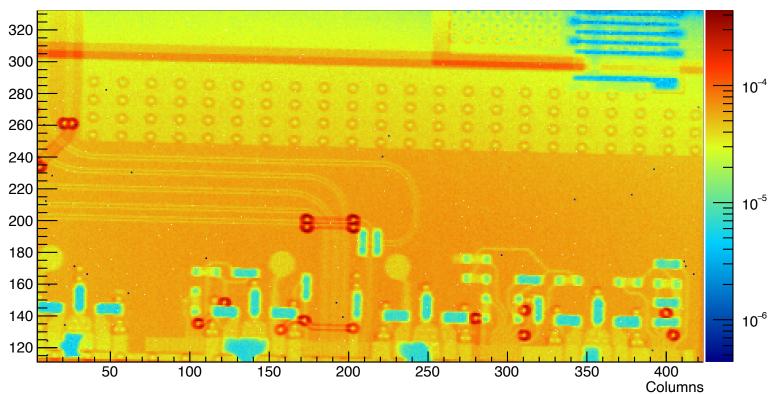

- You will use a Pixel detector with a C-ROC bump-bonded to a planar silicon sensor (cell of 50x50 um2)

- You will cross-check the performance: low silicon current, low threshold, of 1000 electrons; low noise; looking to the S-curve obtained with an calibration injection ==> root files with 1D/ 2D histograms

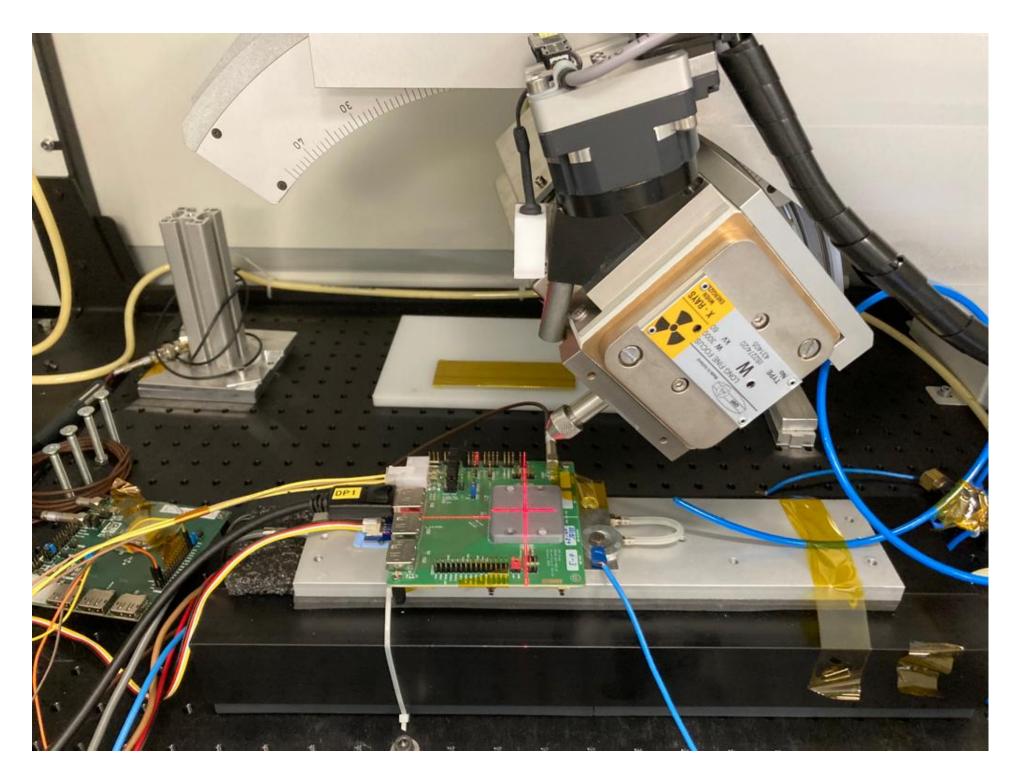

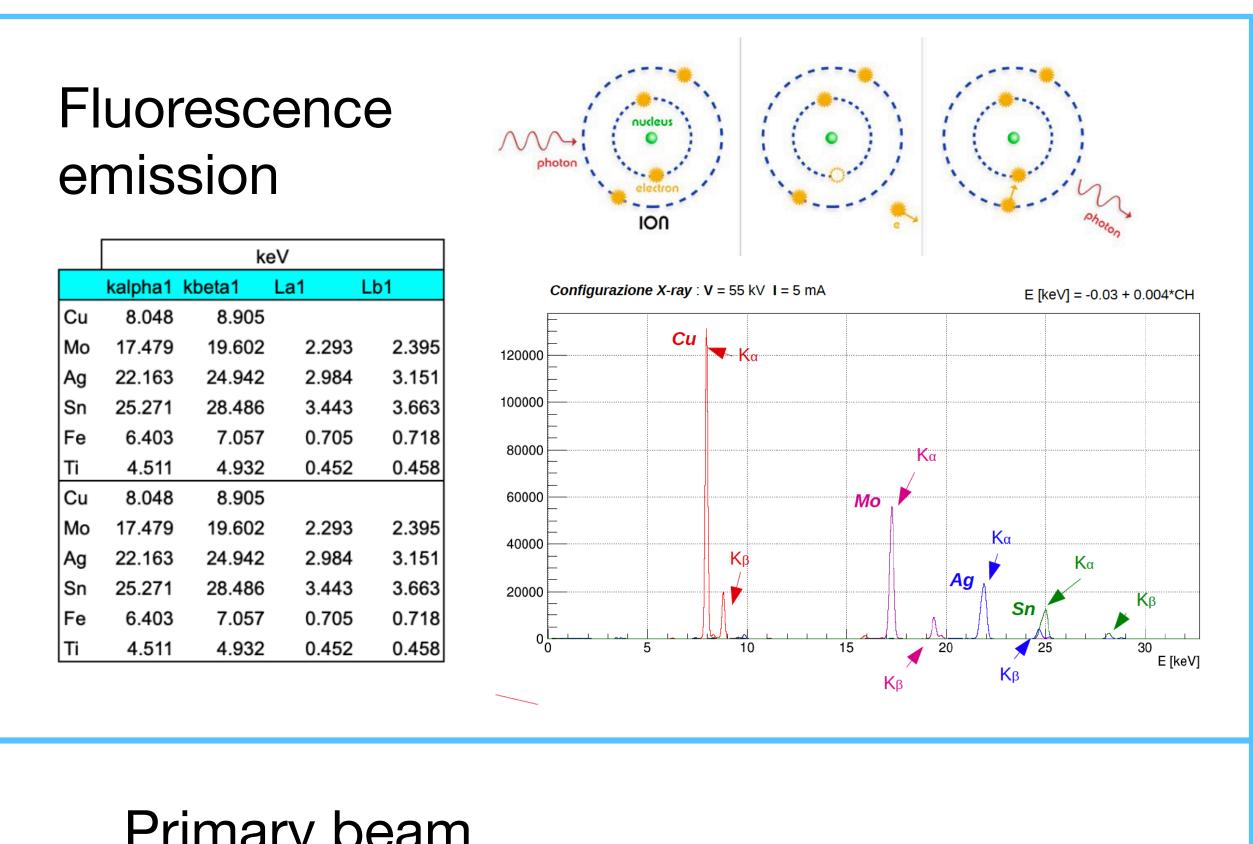

- With the help of an expert, you will send real external signal using an x-ray machine (fully screened, validated by radioprotection):

- check of good connection / efficiency of CROC + sensor

- measurement of energy sent by fluorecence light obtained by x-ray to 5 different targets (Ag, Fe, Cu, Mo, Sn)

- eventually you will be using the detector to make a real xray of a part of the CMS Pixel detector (hybrid)

## Testing pixel detector with an X-ray machine

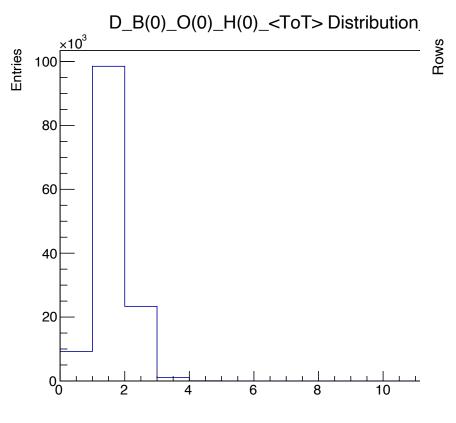

$D_B(0)_O(0)_H(0)_Pixel Alive_Chip(15)$

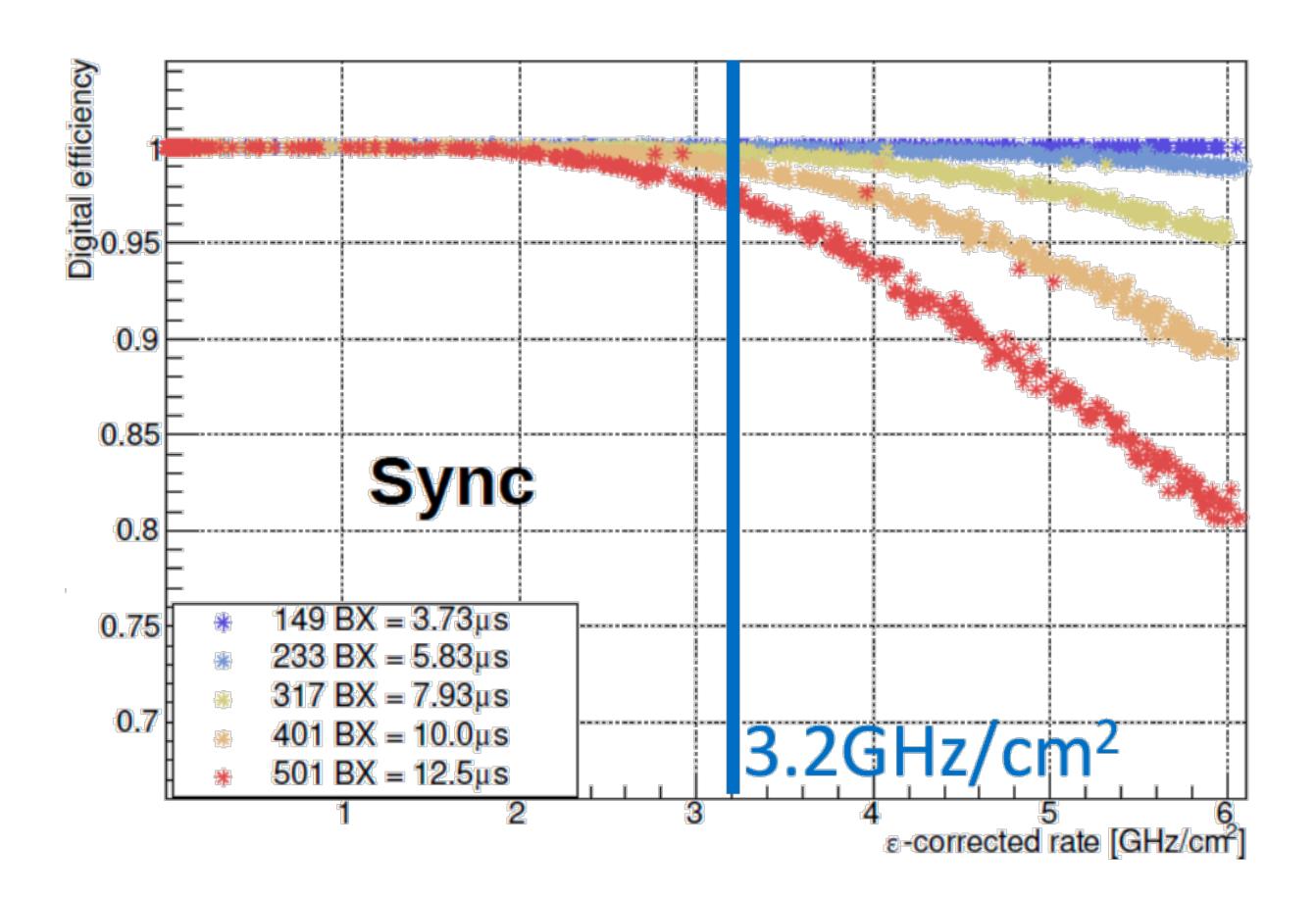

Primary beam up to 50kV, 50 mA

• high single pixel rate, to test for HL\_LHC fluxes (>3 GHz/cm<sup>2</sup>)

5  $\sim$ -----Bremsstrahlung (Deceleration radiation)

## Backup

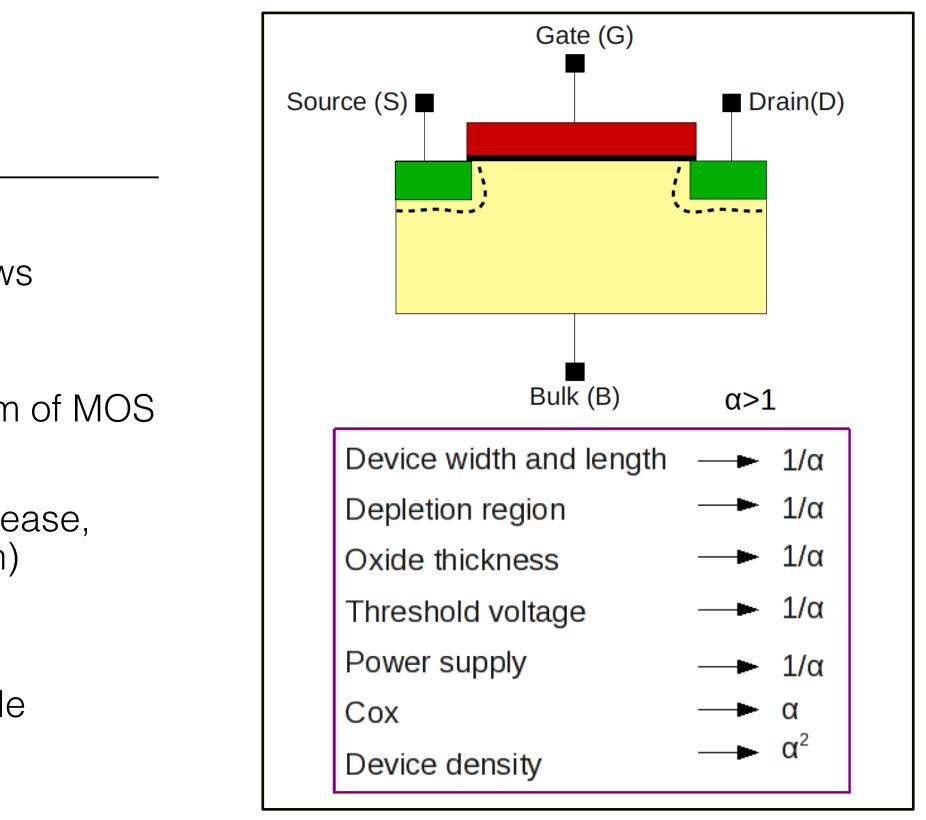

# Advantage of technology scaling

### Lot of digital logic in the pixel-matrix, organised in pixel regions: enough space ? Is power going to explode ?

Moving to more scaled technology - from **130nm to 65nm** (relative scaling alpha=2), digital follows:

#### - Logic density: x4

- both W and L are reduced

#### - <u>Power : ~1/2 - 1/4</u>

- related to clocked operations, therefore follows

**P** = freq C V<sup>2</sup> (charge/disch. cap)

where C is the capacitance to be driven, sum of MOS gate capacitance and metal routing.

C\_gate decreases: W,L decrease; Cox increase, Metal routing capacitance decreases (width)

#### - <u>Speed: ~2</u>

- faster electronics, higher frequency reachable