## **SNRI2023 Lab 1** CMOS Cryogenic Readout Electronics

## Scuola Nazionale dei Rivelatori Innovativi 2023

Torino 2023-10-09

Istituto Nazionale di Fisica Nucleare

Manuel Rolo Fabio Cossio Sofia Blua

# **Context and Definitions**

#### "Deep Cryogenic" electronics for Quantum technologies

- Towards the development of novel quantum sensor technologies through the consolidation and scaling up of existing and emerging technologies;

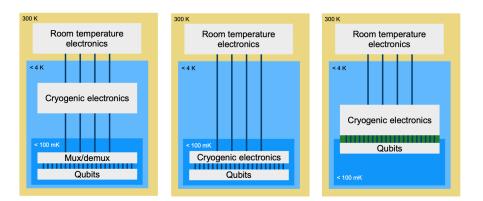

- provide advanced enabling infrastructures and key capabilities for the development of cryogenic electronics in order to solve "the wiring bottleneck" on quantum computers;

- cryogenic CMOS operating <4K and down to the mK pave the way for scalability into the million qubit realm.

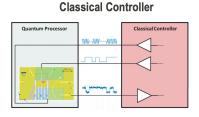

- Electronics to control and read-out the quantum processor mostly operated at room temperature (RT)

- Does not scale with the number of qubits

CMOS Integrated Controller

More scalable approach by moving the control and read-out electronics closer to the qubits and operate it at cryogenic temperature (around 4 K)

C. Degenhardt, "Cryogenic QUBIT Control – The Tyranny of numbers, self-heating and everything"

<sup>□</sup> E. Charbon, ESSCIRC 2019.

□ B. Patra, et al., JSSC, vol. 53, no. 1, 2018

# **Context and Definitions**

### "Mild cryogenic" electronics for Liquid Detectors

- Rare-event search on astroparticles: neutrino physics and direct dark matter detection using liquid scintillators e.g. Liquid Xenon (LXe) and Liquid Argon (LAr);

- Single and dual-phase detectors employing (solid-state) photon sensors require front-end readout electronics operating at 165K (LXe) or 88K (LAr).

| Type           | Photon detector                           | Area $(m^2)$                                                                                                                                                                           |

|----------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LXe            | SiPMs (FBK [Ch2-18], Hamamatsu [Ch2-19]), | 5                                                                                                                                                                                      |

|                | digital 3D-SiPM                           |                                                                                                                                                                                        |

| $\mathbf{LXe}$ | PMTs, SiPMs or Hybrids                    | 8                                                                                                                                                                                      |

|                | (SIGHT, ABALONE)                          |                                                                                                                                                                                        |

| LSci           | FBK SiPMs                                 | 10                                                                                                                                                                                     |

| $\mathbf{LAr}$ | SiPMs (FBK NUV-HD triple-dopant)          | 30                                                                                                                                                                                     |

| LAr            | SiPM is baseline option                   | 200                                                                                                                                                                                    |

| $\mathbf{LAr}$ | Light guide or $trap + SiPM$              | 10-1000                                                                                                                                                                                |

|                | LXe<br>LXe<br>LSci<br>LAr<br>LAr          | LXeSiPMs (FBK [Ch2-18], Hamamatsu [Ch2-19]),<br>digital 3D-SiPMLXePMTs, SiPMs or Hybrids<br>(SIGHT, ABALONE)LSciFBK SiPMsLArSiPMs (FBK NUV-HD triple-dopant)LArSiPM is baseline option |

Need to commit to strong R&D programs for the development and deployment of new readout schemes suitable for future large-scale neutrino and dark matter detectors;

#### today's solutions are not scalable.

Future larger scale experiments will call for innovative cold integrated readout electronics implementing digital signal processing within the photosensor detection module.

"R&D on the 5-year horizon for greater integration include (...) dedicated ASIC design; 3D-vertical integration R&D; and development of lower-power, larger-area and lower-radioactivity photodetection modules."

# **CMOS Cryogenic Electronics**

### Challenges for circuit design and operation

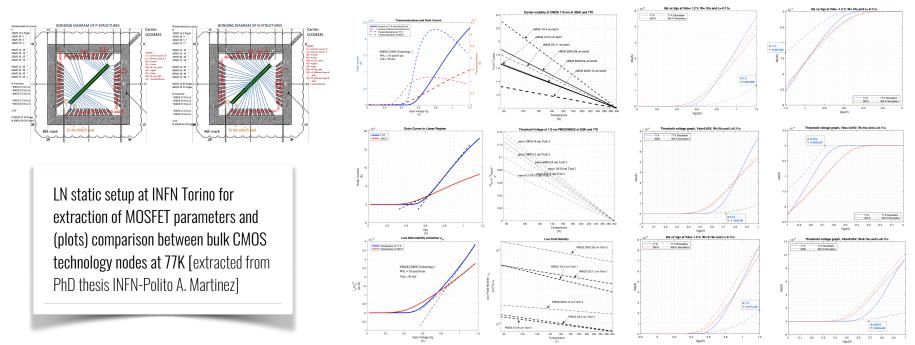

- CMOS Process Design Kits typically valid down to 233K (-40°C), although models scale relatively well down to 77K. This was verified with VDSM bulk and FDSOI technology nodes.

- Cold CMOS PDKs are fundamental for the development of complex mixed-signal ASICs allowing for innovative detector architecture and concepts, data transfer, readout and control.

- If no Cold PDK is available, design test structures and extract MOSFET parameters to guide the circuit design:

### An ASIC for SiPM readout at Cryogenic Temperature

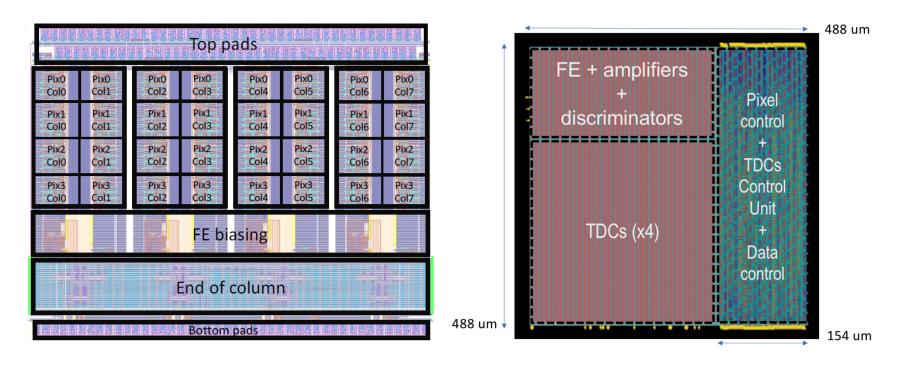

- 32-pixel matrix mixed signal ASIC (CMOS 110nm) developed by INFN, VFE optimised for **operation at 77K**

- the chip performs amplification, signal conditioning and event digitisation, and features fully digital I/O

- Single-photon time tagging mode or time and charge measurement

- 4 LVDS TX data links, SPI configuration, operation at 160/320 MHz (TDC binning 100 or 50 ps, respectively)

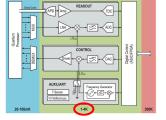

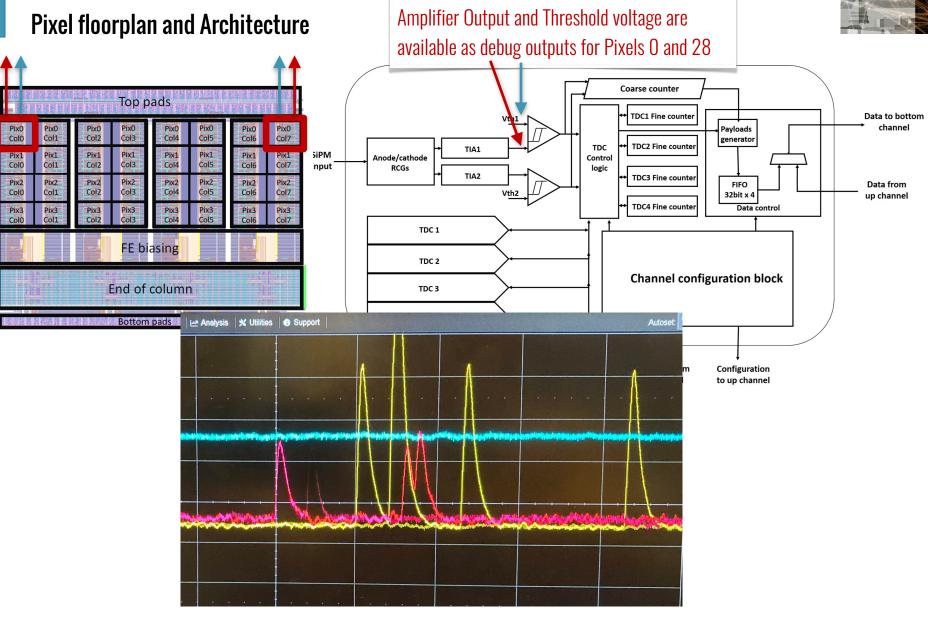

#### **Pixel floorplan and Architecture**

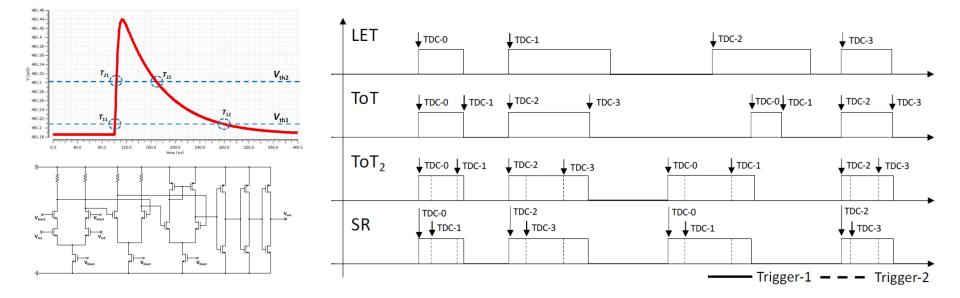

- dual-polarity RCG-based preamplifier: high bandwidth and low input-impedance (10-20  $\Omega$ )

- 2 independent post-amp branches and 4 gain settings

- Dual leading edge discriminators with independent (and per pixel) threshold settings (6-bit DAC)

- Pixel control logic handles quad-TDC operation, pixel configuration and data transmission

SNRI 2023

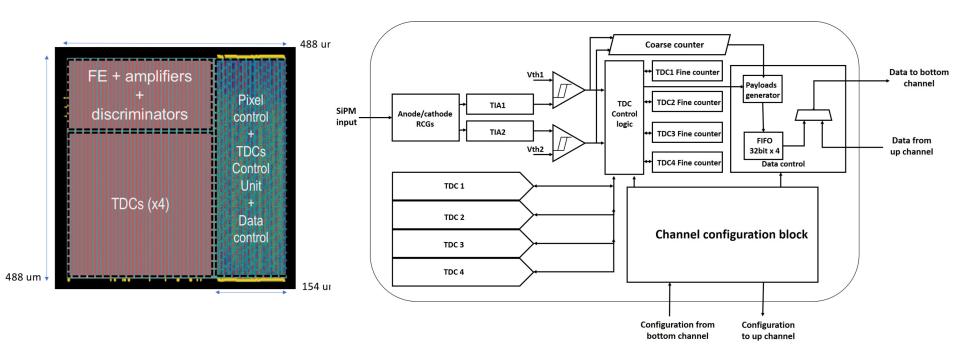

### Time-to-Digital Converters

**SNRI 2023**

- A coarse time stamp is extracted from the system clock running up to 320 MHz

- A Low-power Analogue interpolation TDC measures phase between event trigger (TO) and clock (T1)

#### **Pixel Operation Modes**

- LET leading edge threshold measurement, high-rate time-stamp architecture

- **TOT** Time-over-Threshold (selectable branch for falling edge measurement)

- SR slew-rate measurement for signal shape characterisation

- Pixel can be disabled, in normal (trigger less) acquisition mode or can be triggered by a test-pulse,

- either generated by the on-chip calibration circuitry or propagated from the DAQ,

- either injecting a configurable charge to the front-end or triggering asynchronously the pixel logic for characterisation and calibration of the TDCs

#### **Pixel Operation Modes**

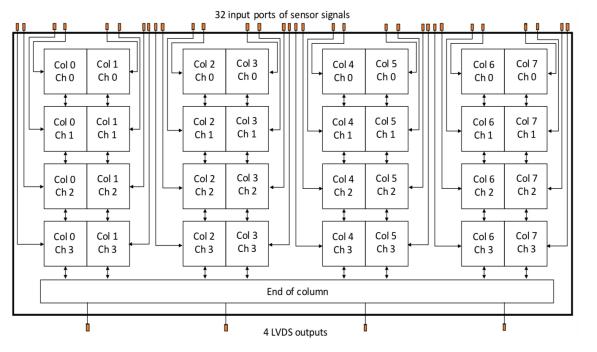

- 32-pixel matrix (4×8 array) mixed-signal ASIC

- SPI-based chip configuration

| Column ID<br>3 bits |          | Channel ID    | TDO                  | 2 bits    |           | nter Fine            | Fine counter<br>9 bits |  |

|---------------------|----------|---------------|----------------------|-----------|-----------|----------------------|------------------------|--|

|                     |          | 3 bits        | 2 b                  |           |           | 9                    |                        |  |

| Status wo           | rd       |               |                      |           |           |                      |                        |  |

| Column              | Pixel ID | Lost<br>event | Lost e.w.<br>counter | Lost e.w. | Lost e.w. | Lost e.w.<br>counter | SEU                    |  |

| Column<br>ID        |          |               |                      |           |           |                      | SEU<br>counter         |  |

- 64-bit (32-bit on time tagging mode) event and status data is generated on-pixel and propagated down the column

- End of Column collects digitised data from pixels and transmits it off-chip using (up to) 4 LVDS Tx links

- End of Column provides also configuration (and analogue bias) to the pixel "matrix"

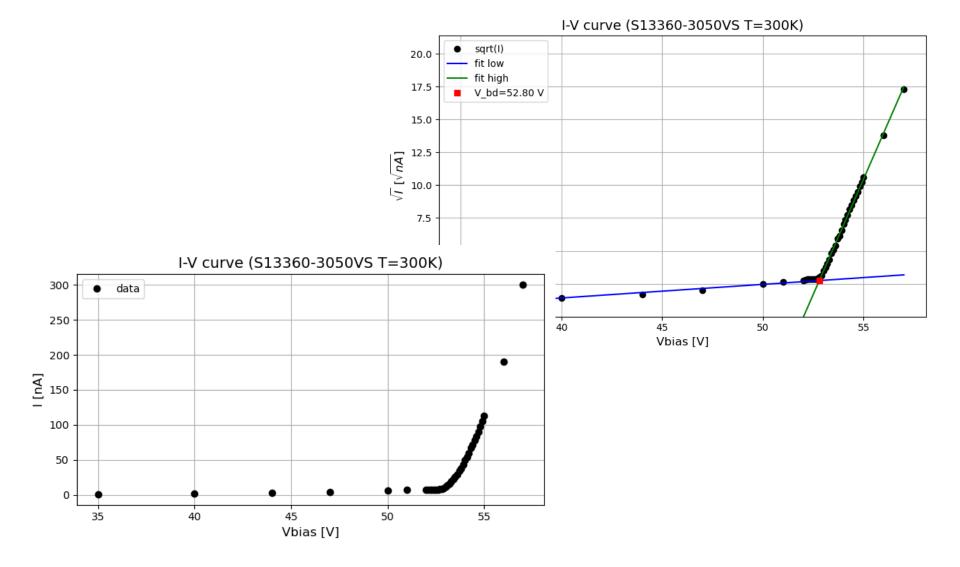

SiPM: extraction of Breakdown Voltage at 300K

13

**"** SNRI 2023

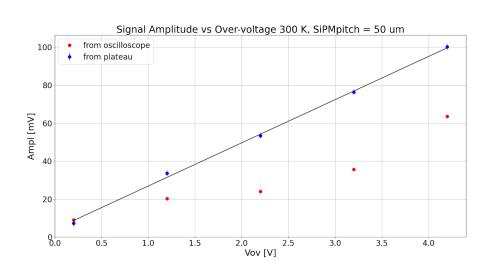

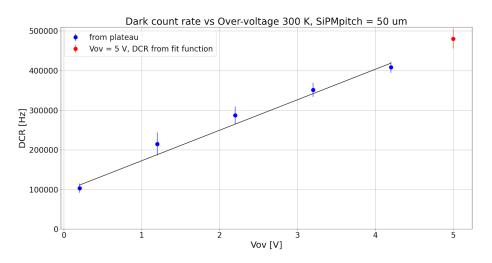

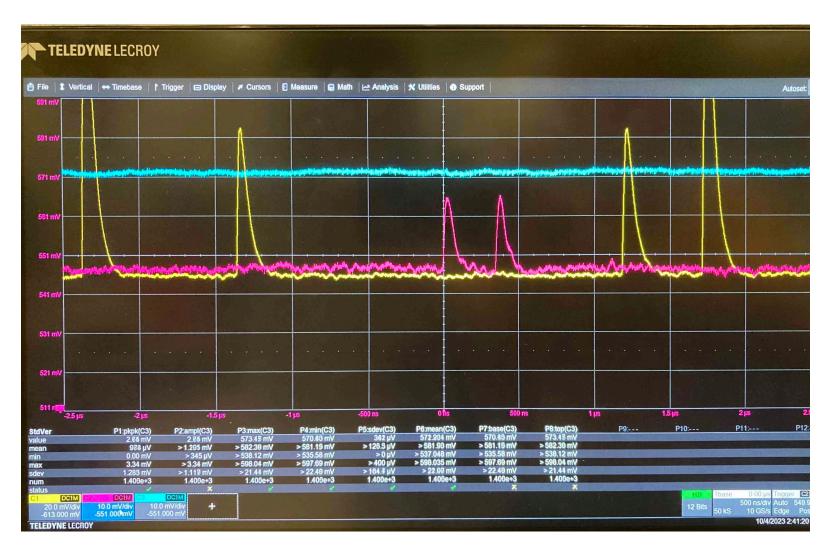

#### Dark Count Rate (DCR) and signal amplitude studies at 300K

14

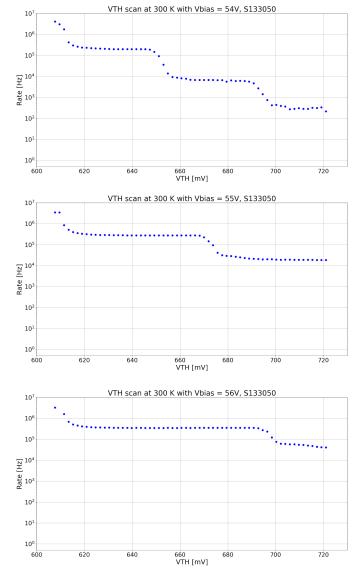

Studies of signal amplitude and threshold scans during cool-down

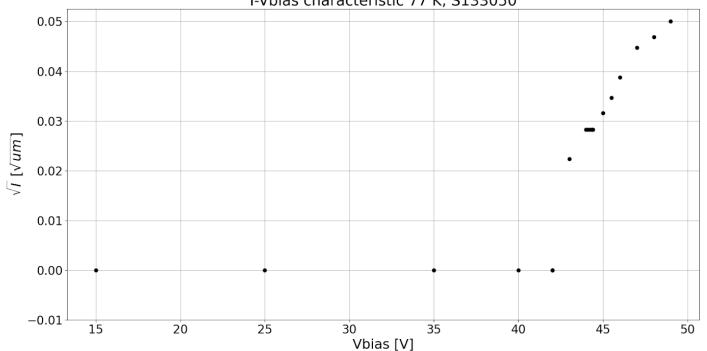

### SiPM: extraction of Breakdown Voltage at 77K

I-Vbias characteristic 77 K, S133050

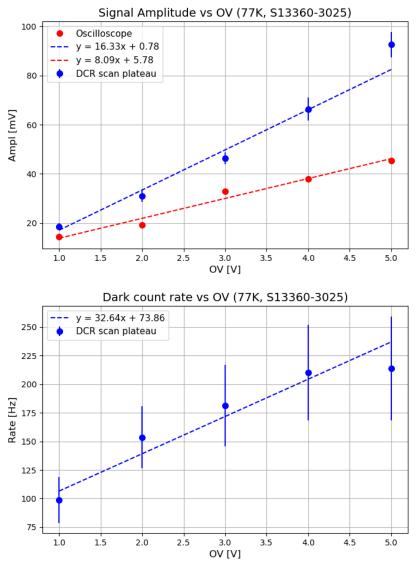

#### Dark Count Rate (DCR) and signal amplitude studies at 77K

Rate [Hz] 104 103 10<sup>2</sup> 10<sup>1</sup> 10<sup>0</sup> VTH [mV] VTH scan at 77 K with Vbias = 46V  $10^{6}$ Rate [Hz] 10, 10, 10<sup>1</sup> 10<sup>0</sup> VTH [mV] VTH scan at 77 K with Vbias = 47V Rate [Hz] 10<sup>1</sup> 10<sup>0</sup> VTH [mV]

VTH scan at 77 K with Vbias = 45V

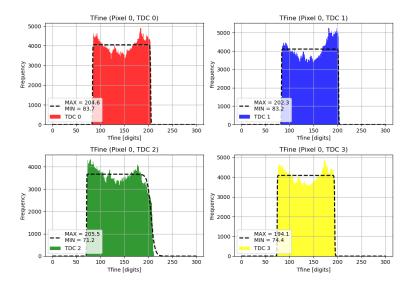

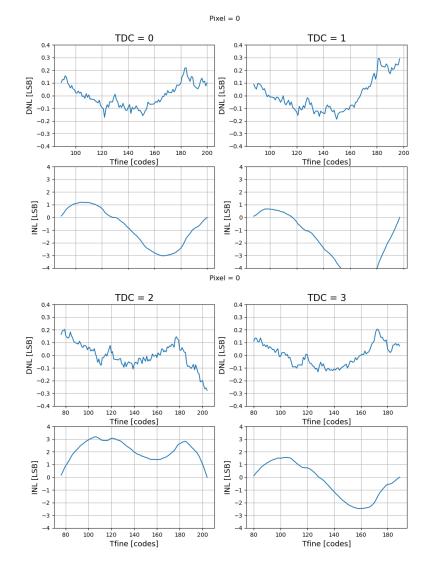

### **Characterisation of Time-to-Digital Converters**

SNRI 2023

• Quantisation error (RT vs. LN)

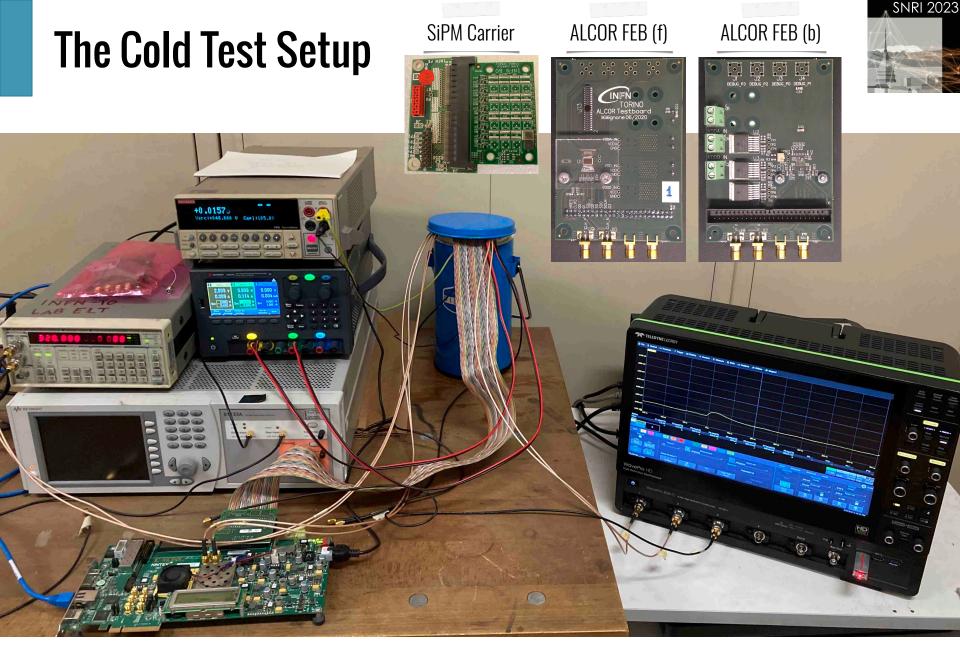

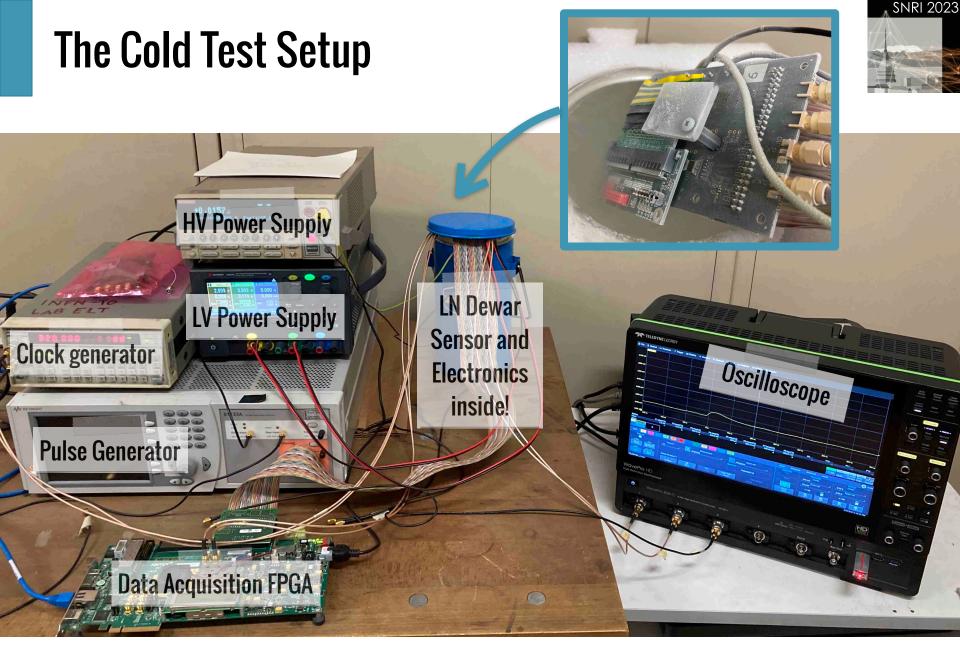

# The Cold Test Setup

on the definition of "Hands-On Laboratory"...

- Test setup uses Liquid Nitrogen (77K)

- Handling of the electronics and cabling during test with LN (cool-down and warm-up) will be sorted out by the Laboratory Lecturer

- Keep a safe distance from the dewar during re-fill operations

# Lab Support Material

what's inside