## HERD – SCD meeting

Mechanics status

02/06/2023

E. Mancini, L. Mussolin, G. Ambrosi

Brief agenda

- Square silicon side size reduced

- Fan-out electronics, new envelope

- Front-end electronics and cabling clearance

- SCD side, fixations to ground

**NOTE:** purple is used for things added during or after the meeting

## Detector size update

### **Detector specs.**

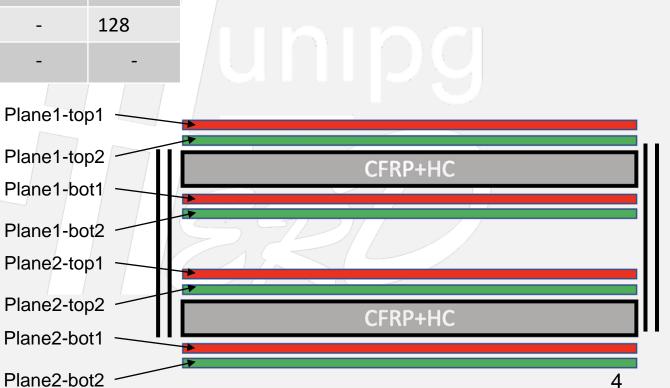

| Top pack         | No. of<br>tiles X* | No. of<br>tiles Y* |

|------------------|--------------------|--------------------|

| Plane1-top1      | -                  | 256                |

| Plane1-top2      | 256                | -                  |

| Plane1-bot1      | 256                | -                  |

| Plane1-bot2      | -                  | 256                |

| Same for plane 2 | -                  | -                  |

| side pack        | No. of<br>tiles X* | No. of<br>tiles Y* |

|------------------|--------------------|--------------------|

| Plane1-top1      | -                  | 128                |

| Plane1-top2      | 128                | -                  |

| Plane1-bot1      | 128                | -                  |

| Plane1-bot2      | -                  | 128                |

| Same for plane 2 | -                  | -                  |

|                  | 1                  | 1 1 1              |

Total number of tiles top: 2048 Total number of tiles per side: 1024 Total number of tiles: 6144

Wrong color coding. The silicon orientation is sym. wrt the plane center

### **Detector specs.**

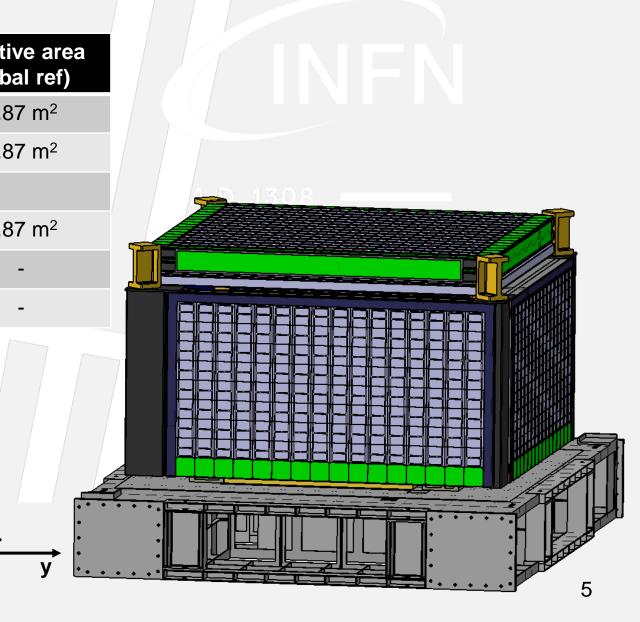

| Plane position (global ref) | Detective area<br>X (global ref) | Detective area<br>Y (global ref) | Detective area<br>Z (global ref) |

|-----------------------------|----------------------------------|----------------------------------|----------------------------------|

| X+                          | -                                | 4.87 m <sup>2</sup>              | 4.87 m <sup>2</sup>              |

| X-                          | -                                | 4.87 m <sup>2</sup>              | 4.87 m <sup>2</sup>              |

| Y+                          | 4.87 m <sup>2</sup>              | -                                |                                  |

| Y-                          | 4.87 m <sup>2</sup>              | -                                | 4.87 m <sup>2</sup>              |

| Z+                          | 9.73 m <sup>2</sup>              | 9.73 m <sup>2</sup>              | -                                |

| Z-                          | -                                | -                                | -                                |

Z

Total number of tiles top: 2048 Total number of tiles per side: 1024 Total number of tiles: 6144 Silicon size: 97.5 x 97.5 mm<sup>2</sup> Total silicon area: 58.41 m<sup>2</sup>

### **Detector specs.**

6

| ERD                                                                                                         |                                                |                                  |                   |                                 |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------|-------------------|---------------------------------|

| Plane position (global ref)                                                                                 | Detective area<br>X (global ref)               | Detective area<br>Y (global ref) | Detect<br>Z (glob | Is this enough for the SCD side |

| X+                                                                                                          | -                                              | 4.87 m <sup>2</sup>              | 4.                | lateral bonds?                  |

| Х-                                                                                                          | -                                              | 4.87 m <sup>2</sup>              | 4.                | .2 mm                           |

| Y+                                                                                                          | 4.87 m <sup>2</sup>                            | -                                |                   |                                 |

| Y-                                                                                                          | 4.87 m <sup>2</sup>                            | -                                | 4.                |                                 |

| Z+                                                                                                          | 9.73 m <sup>2</sup>                            | 9.73 m <sup>2</sup>              |                   | .2 mm                           |

| Z-                                                                                                          | -                                              | -                                |                   |                                 |

| Total number of ti<br>Total number of ti<br>Total number of ti<br>Silicon size: 97.5<br>Total silicon area: | iles per side: 102<br>iles: 6144<br>x 97.5 mm² | 24                               | Z 🔺               |                                 |

| Spacing between<br>Spacing between                                                                          |                                                |                                  |                   |                                 |

×

NOTE: silicon spacing can be reduced on the side but on top it must be equal to the ladders'.

INF

A.D. 1308 UNIPG

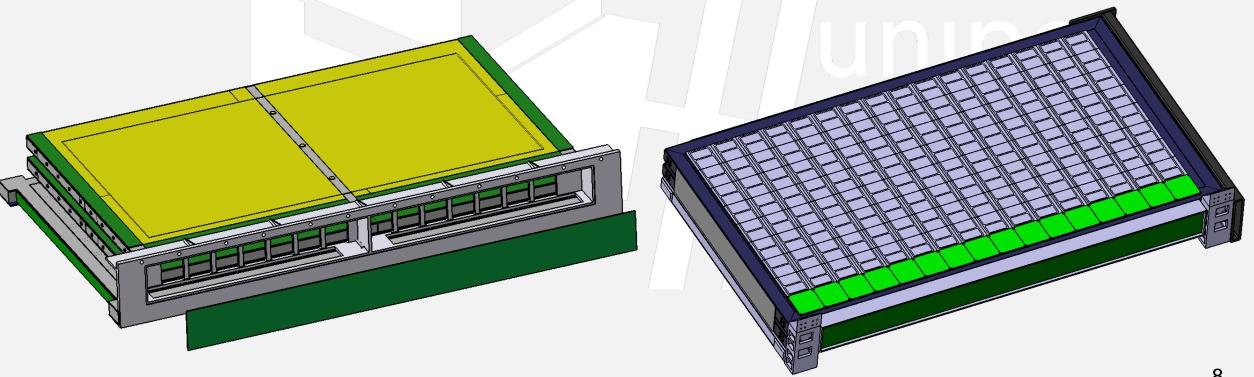

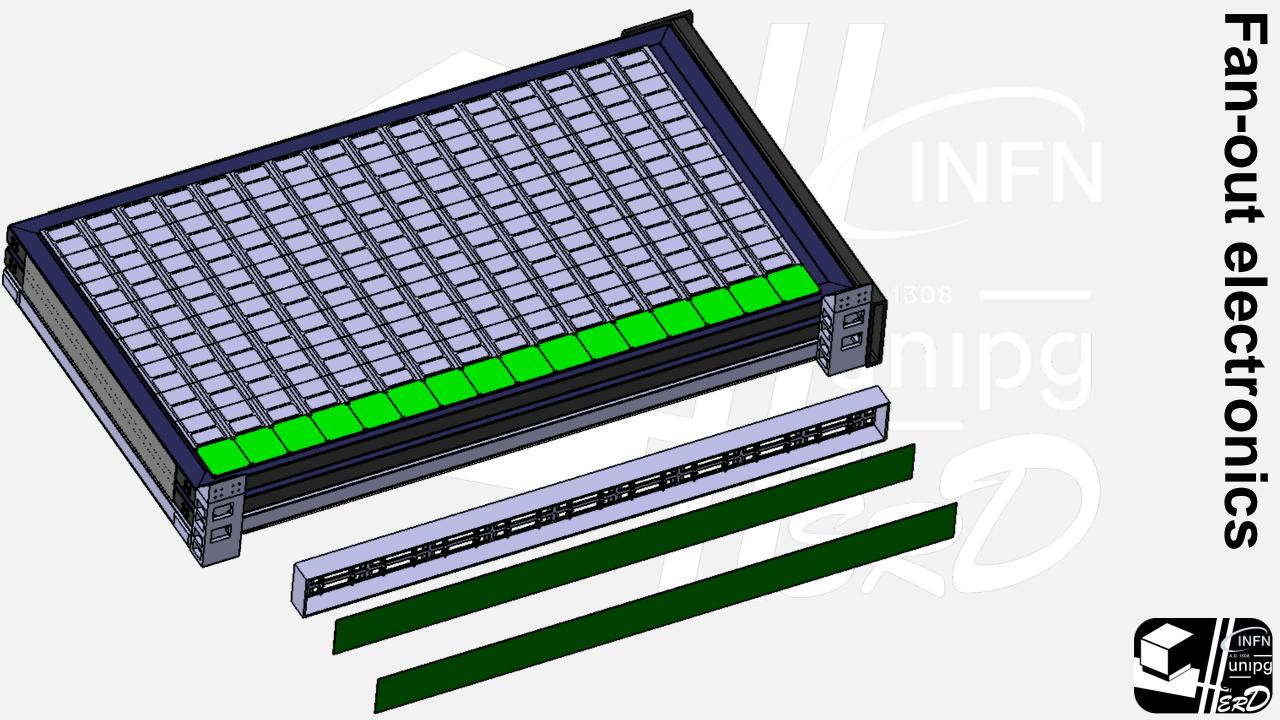

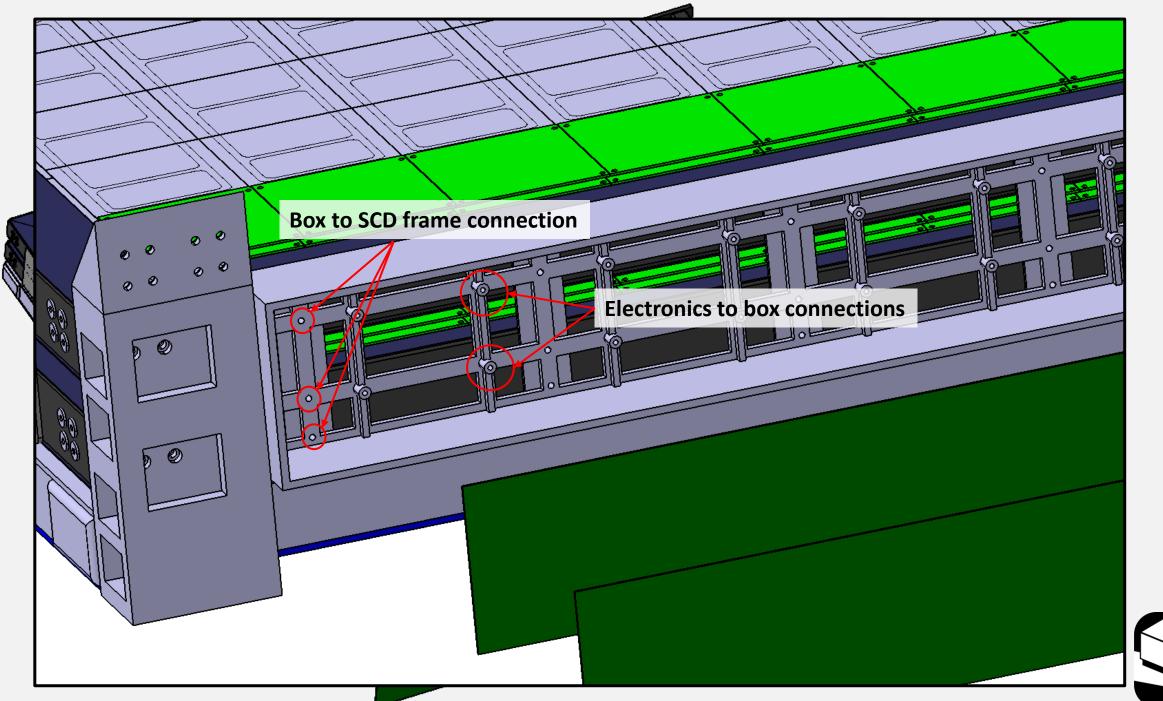

# **Fan-out electronics**

### **Fan-out electronics**

- Old design: 1564x142 mm<sup>2</sup>

- PCB dimensions according to the present design: 1488x108 mm<sup>2</sup>

### **Discussion Gong-Edoardo-Rujie**

#### • Edoardo

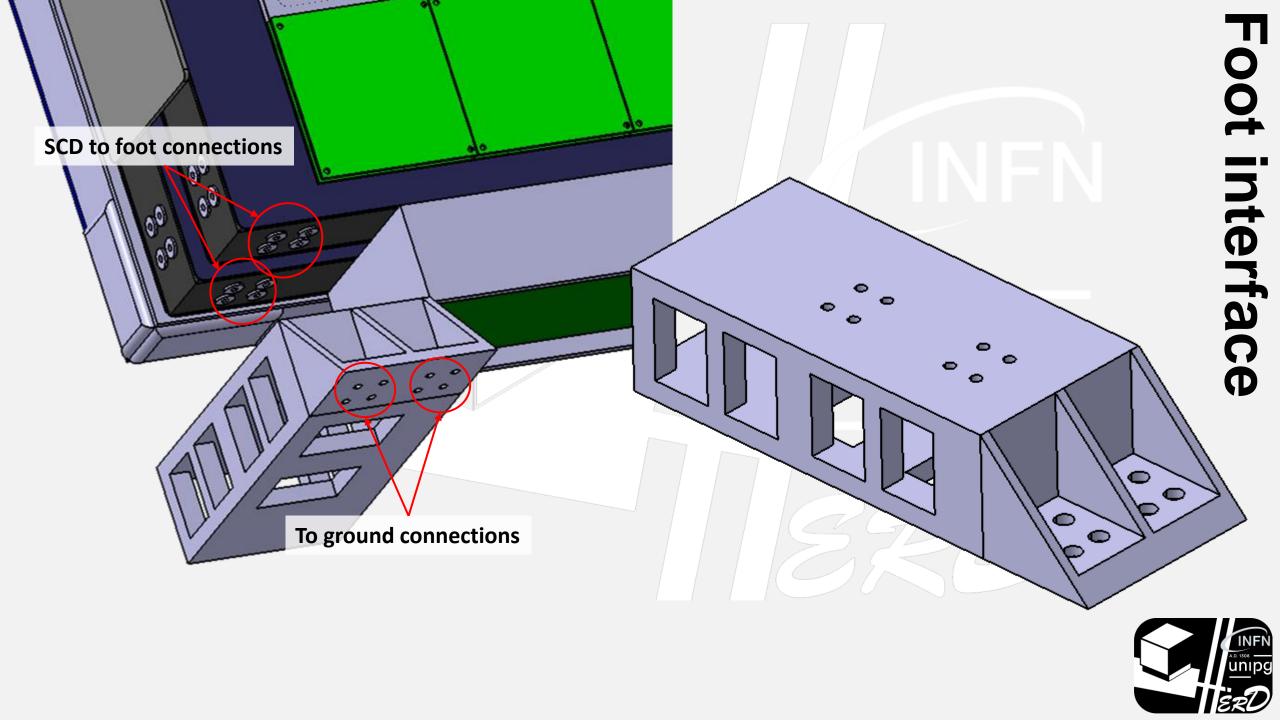

- will try to reduce the feet dimensions so have an electronics size as close as possible to the detector size

- will send the updated CAD version to Rujie for thermal analysis.

- Evaluate also the possibility to use the debris shield as a radiator along with the pipes (Rujie)

- Gong

- will try to develop more than one front-end PCB design so to have the connector or the side and gain some space

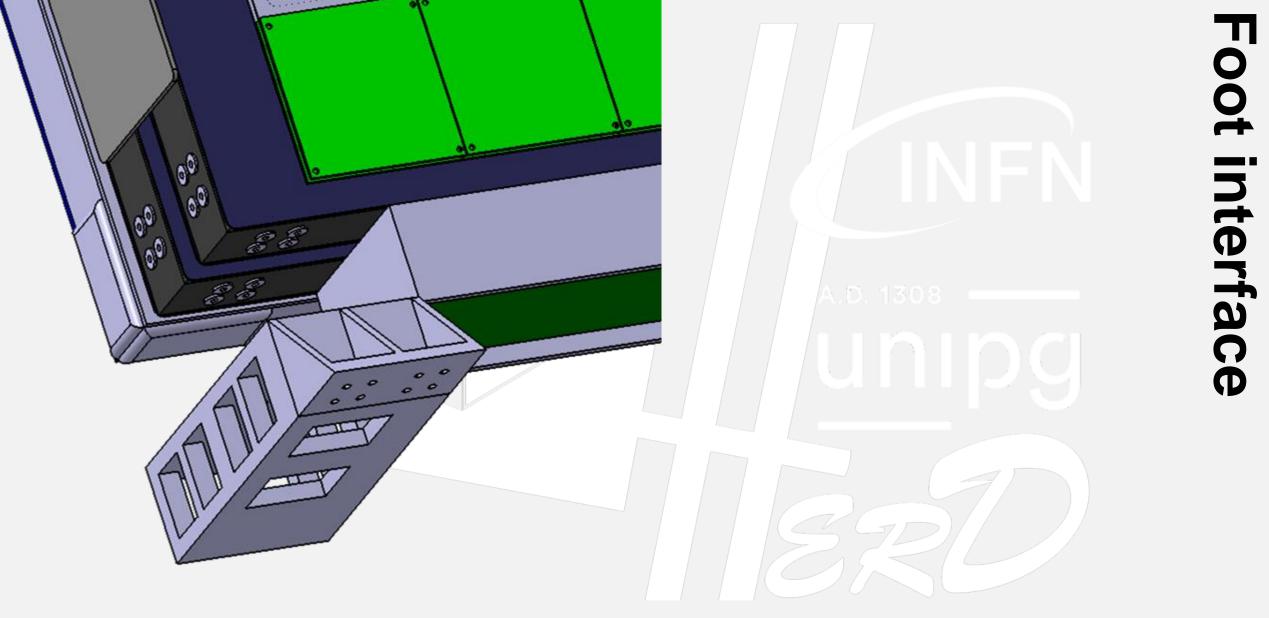

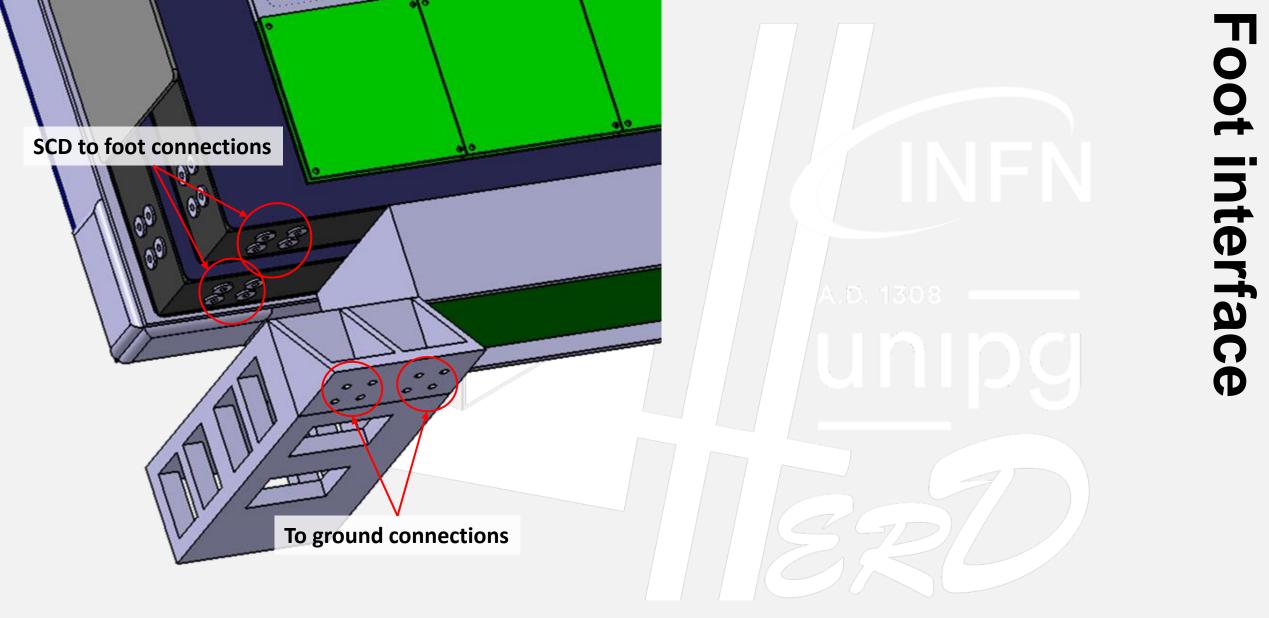

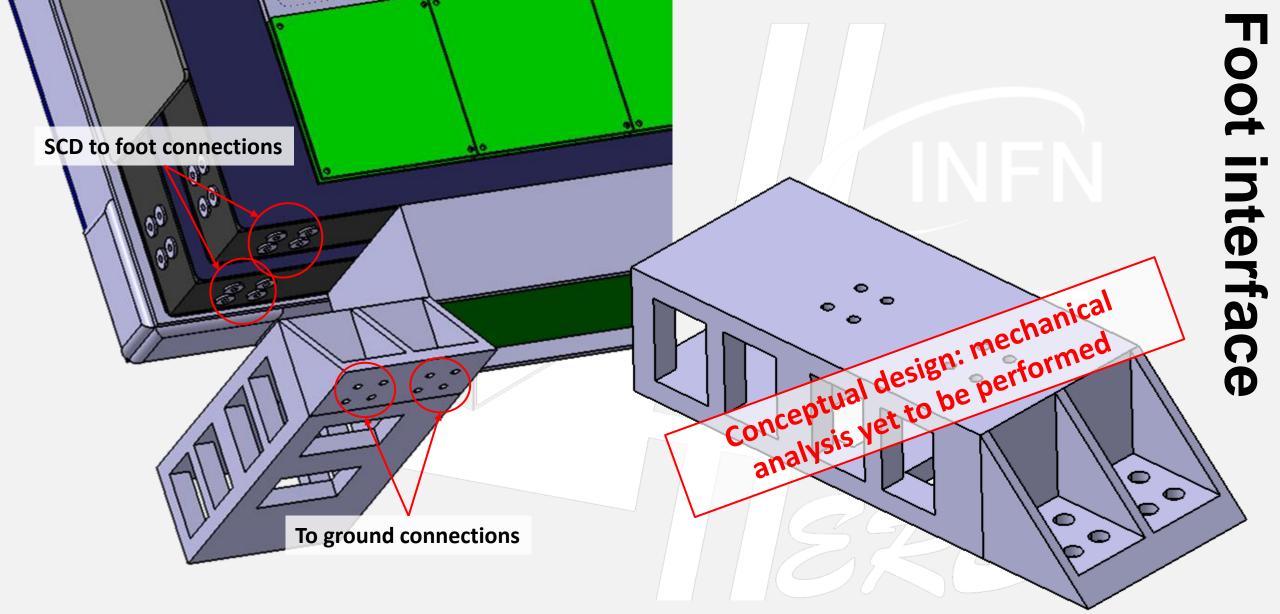

# To ground mech. connection

NOTE: the present design foreseen a feet front fixation. Accessibility consideration could lead to a both sides fixation which is better from a mechanical point of view

## Front-end electronics

### **Front-end electronics**

#### **Questions:**

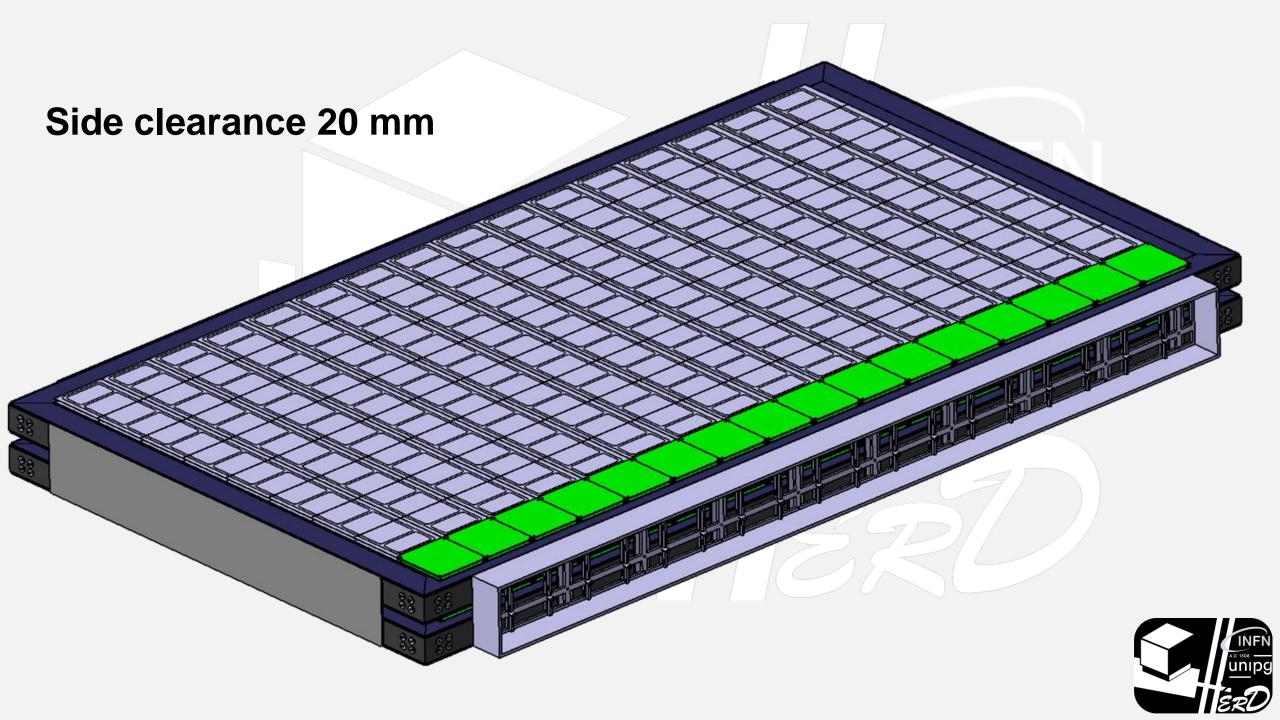

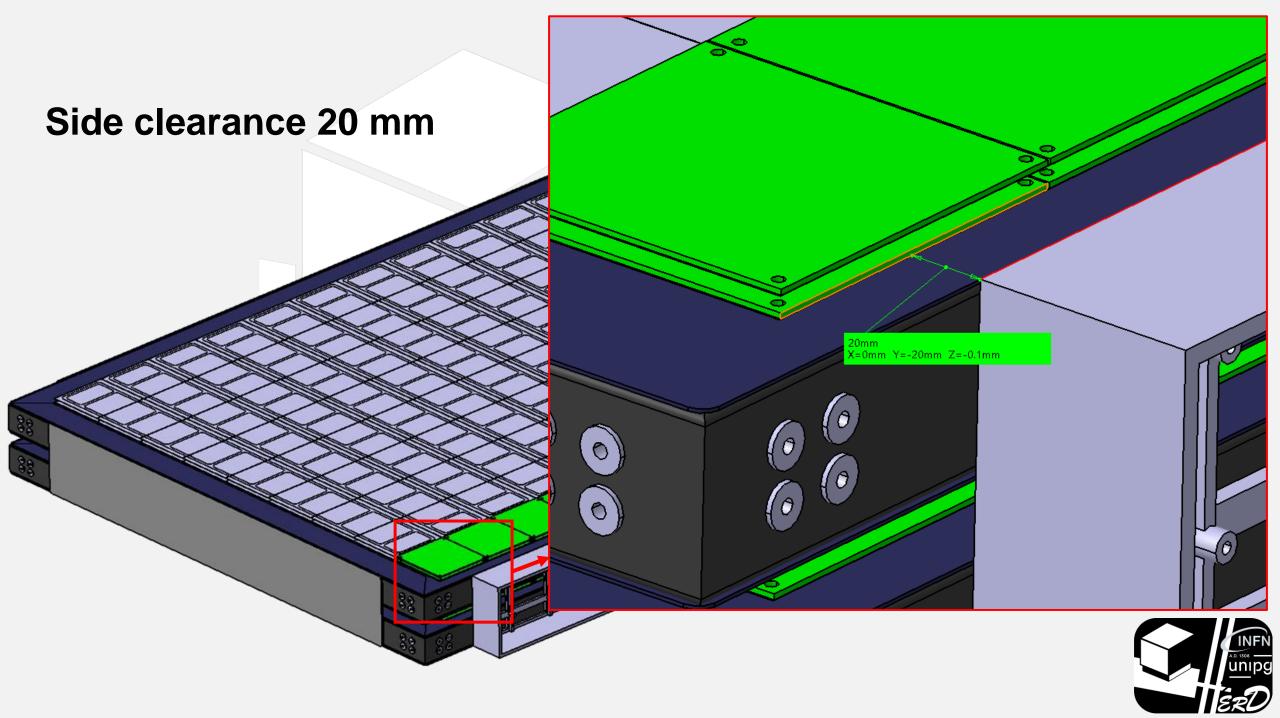

- The top and side SCD have the same front-end electronics dimensions?

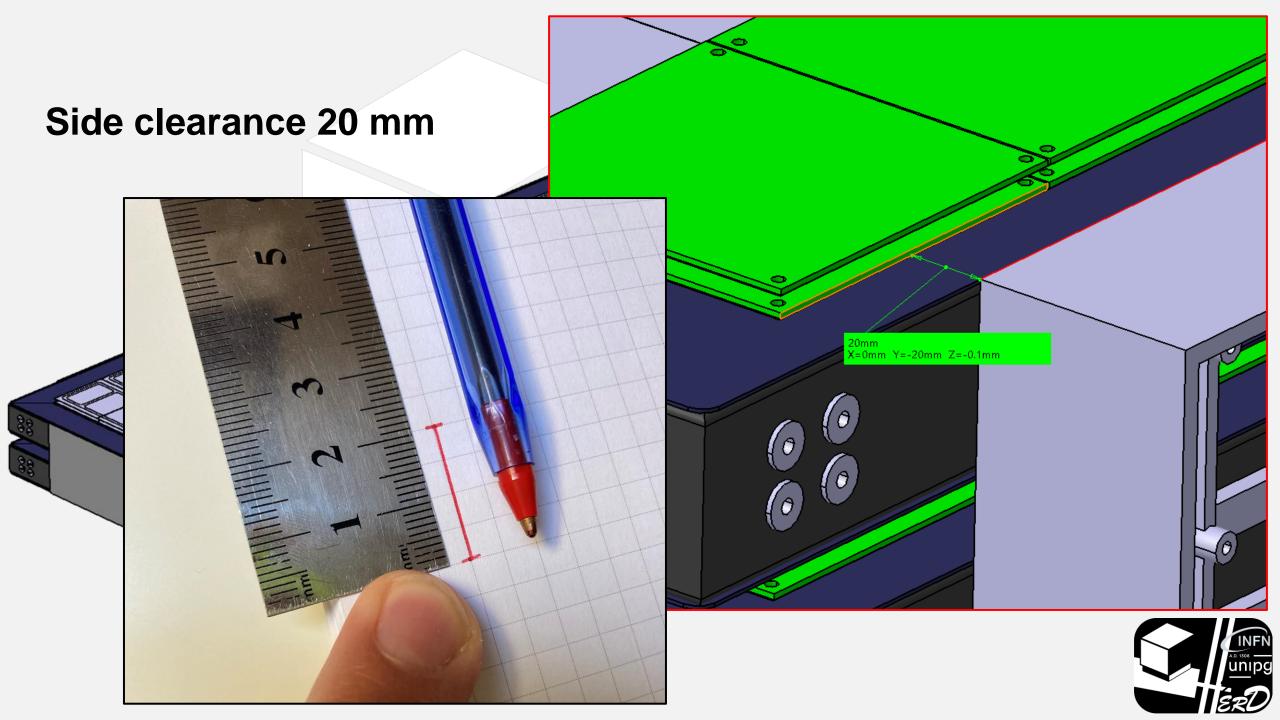

- Is the side clearance (20 mm) acceptable?

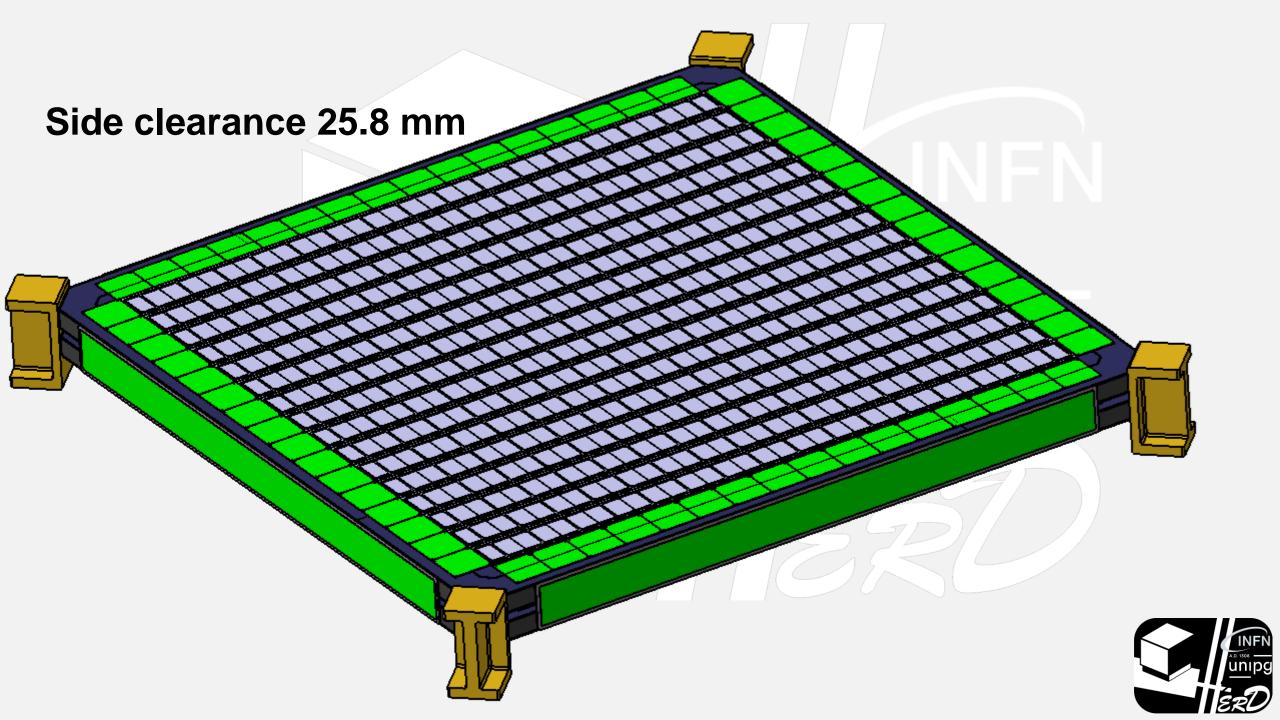

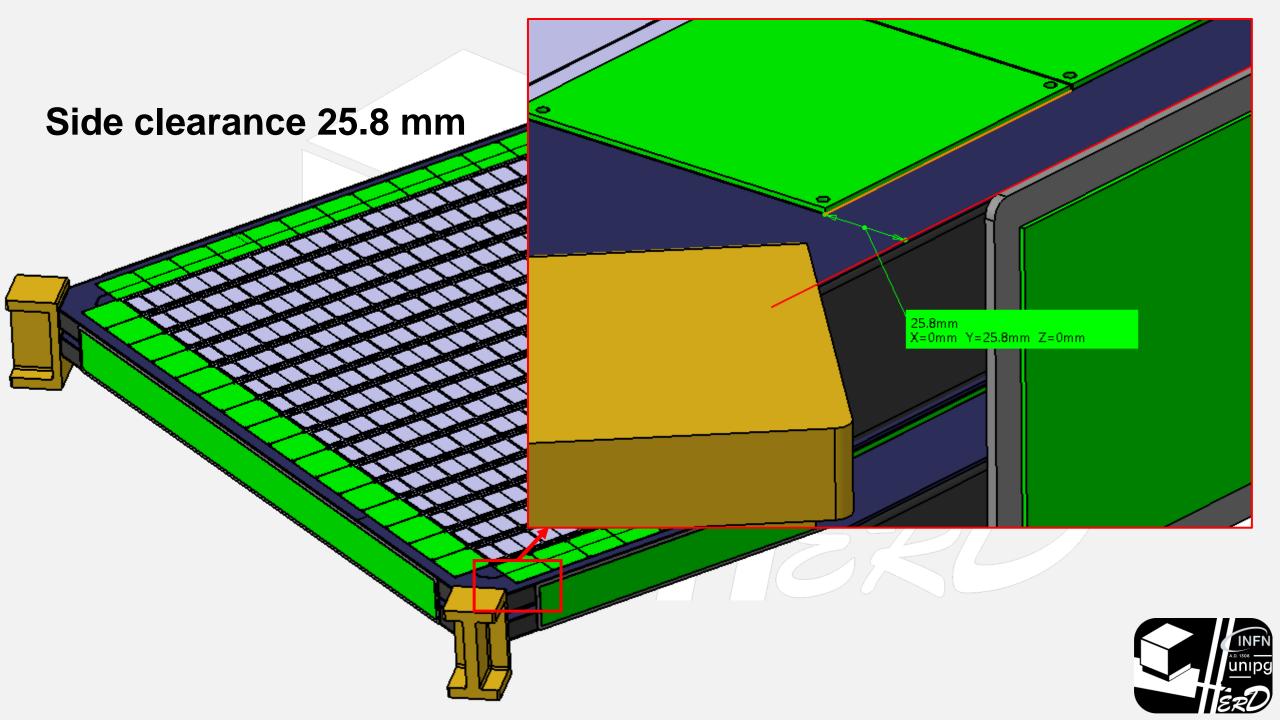

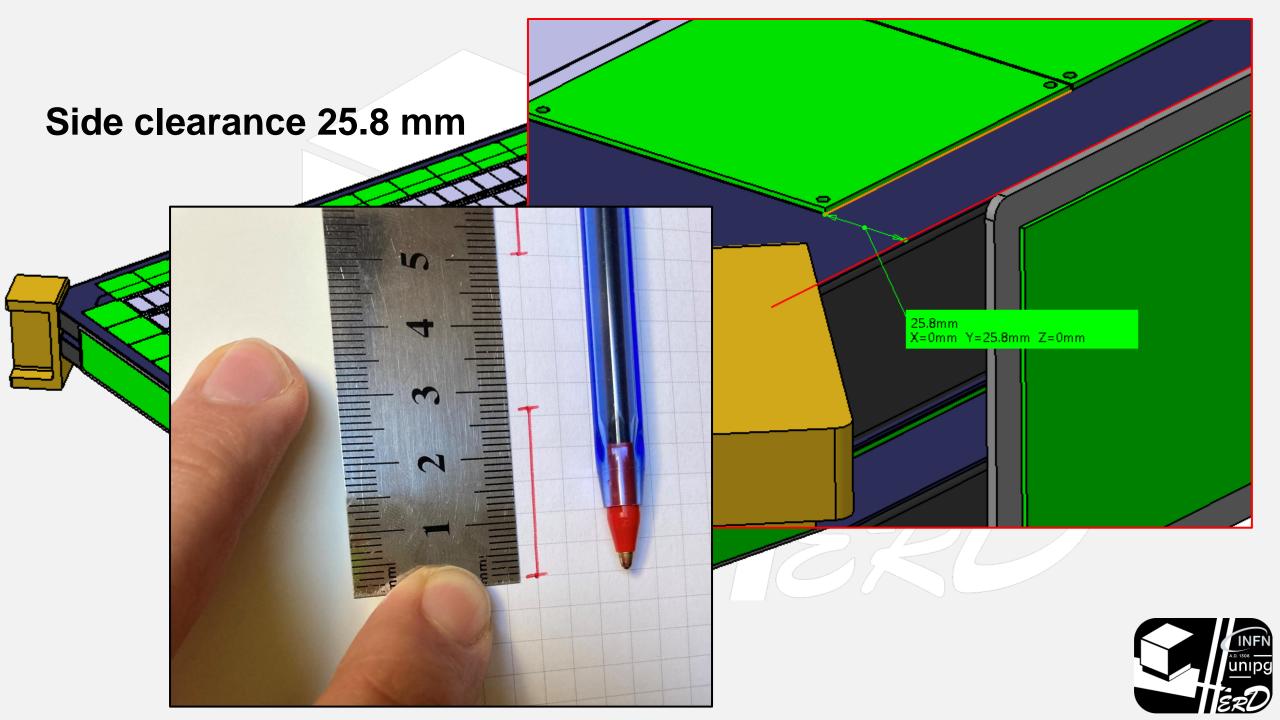

- Is the top clearance (25.8) acceptable?

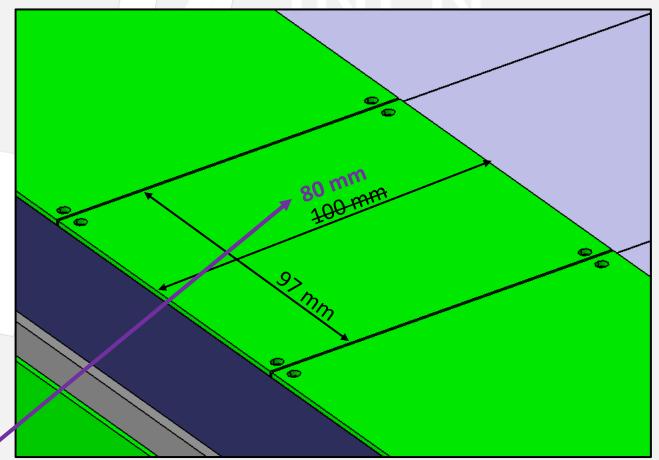

### **Front-end size**

Dimension of the present design:

- 100 mm x 97 mm

- .2 mm spacing between PCB and S

**Dimension 1** (97 mm) constrained by silicon size and ladders' spacing:

- max: 97.5 mm + .2 mm margin\*

- min: detector considerations (microbonds)

**Dimension 2** (100 mm) unconstrained:

- The smaller the better. Every mm gained is added to the routing clearance

- Answer from Gong: yet to be defined. For now, go with 80 mm

\*Accounts for the PCB manufacturing accuracy

**NOTE:** in this design the front-end dimensions are the same for the top and the side

### Thanks for the attention