#### WP 5: R&D Belle II PXD DAQ

Jens Sören Lange (Justus-Liebig-Universität Giessen) Jennifer 2 General Meeting, *Prague, 18.11.2022*

#### WP 5.2

### b) Online data acquisition and remote controls

- new hardware technologies for high bandwidth data transfer

- optical technologies (16.3 Gbps)

- 10 Gbps ethernet

- precise timing distribution in sub-nanosecond regime

- intelligent realtime algorithms for online data reduction

- Belle II background rejection on FPGAs

- HyperK vertexing on trigger level (t <10 ns) on GPUs</li>

- novel programming and DAQ software techniques

- parallelisation on both FPGAs or GPUs

- methods of artificial intelligence for trigger decisions

- integrated dynamic service discovery, monitoring, fault tolerance, dynamic routing and remote control.

### Outline

- What has changed in the past 3 years?

- Results on high bandwidth data transfer (Belle II PXD)

- Results on "AI" algorithms and hardware implementation (Belle II PXD)

### What has changed in the past 3 years?

- Belle II recorded 428 fb $^{-1}$  recorded (comparable to complete BaBar data set)

- PXD DAQ stable, uptime 98.8% (relativ to Belle II DAQ)

- physics results with PXD: lifetime of D<sup>0</sup>, D<sup>+</sup>,  $\Lambda_c^+$ ,  $\Omega_c^0$  measured precisely

- PXD decommissioned, work focused on PXD2 installation (long shutdown)

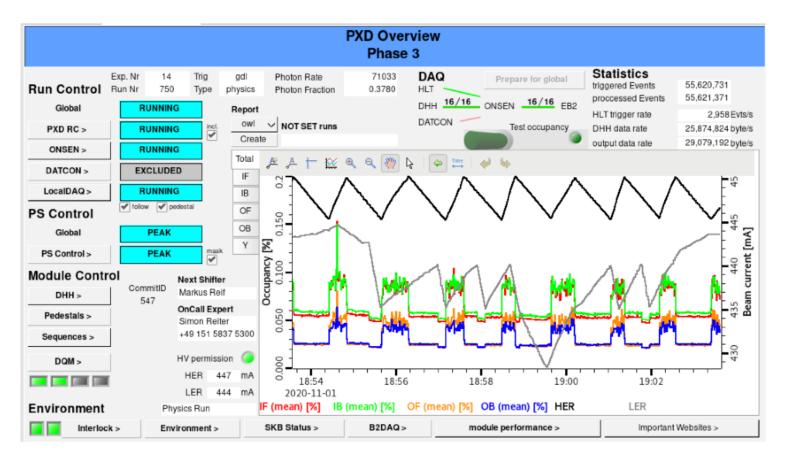

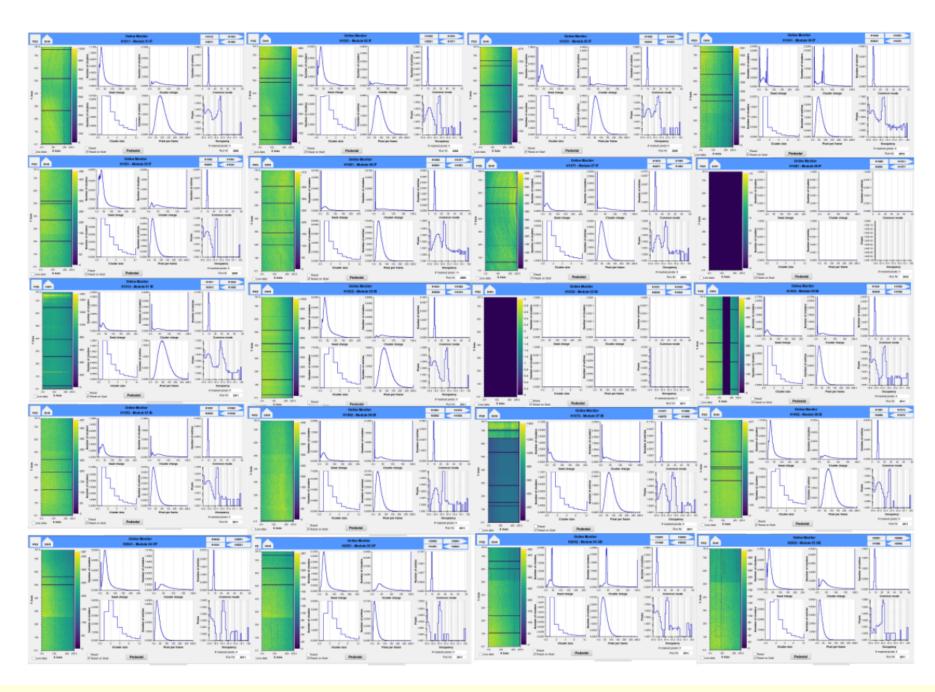

Occupancy

calculated

online on

PXD DAQ

(Onsen system)

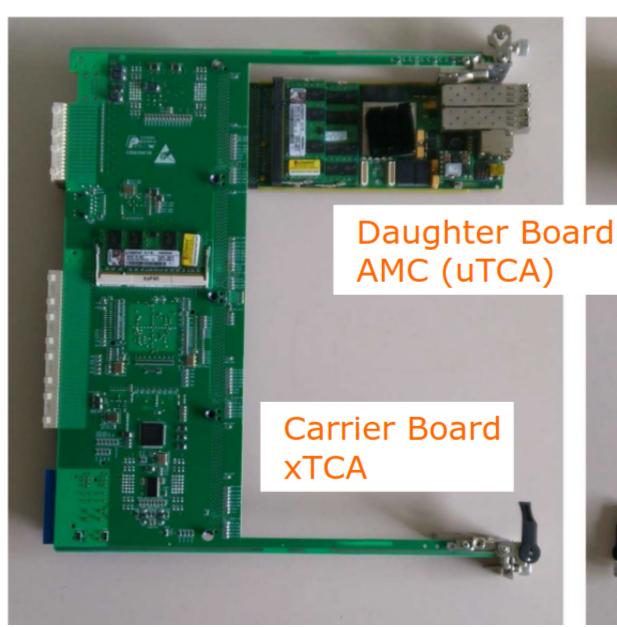

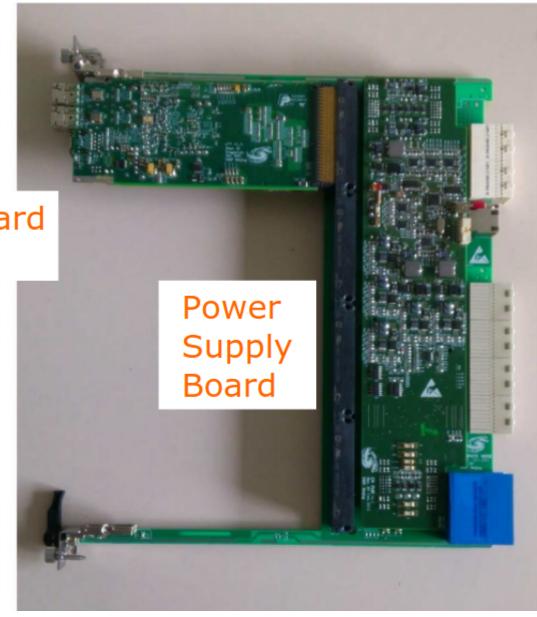

# PXD DAQ, ONSEN system hardware

### PXD online monitor during Belle II physics data taking

# HIGH BANDWIDTH DATA TRANSFER

# Link bandwidth compared

| Wifi (802.11 a/g)               | 20 Mbps                                          |                               |

|---------------------------------|--------------------------------------------------|-------------------------------|

| 4G                              | 20 Mbps (download)                               | mobile phones                 |

| 5G                              | 100-300 Mbps (download)                          | mobile phones                 |

| Gigabit Ethernet                | 1 Gbps                                           | cable (electrical or optical) |

| ONSEN link                      | 6.125 Gbps                                       | optical                       |

| ONSEN link<br>new carrier board | 16.3 Gbps                                        | optical                       |

| complete PXD                    | ~200 Gbps @ 3% occupancy<br>(5 DVD per 1 second) |                               |

| ATCA ADLINK<br>aTCA-3150        | 10 Gbps (uplink)                                 |                               |

| ATCA ADLINK<br>aTCA-3710        | 40 Gbps (uplink)                                 |                               |

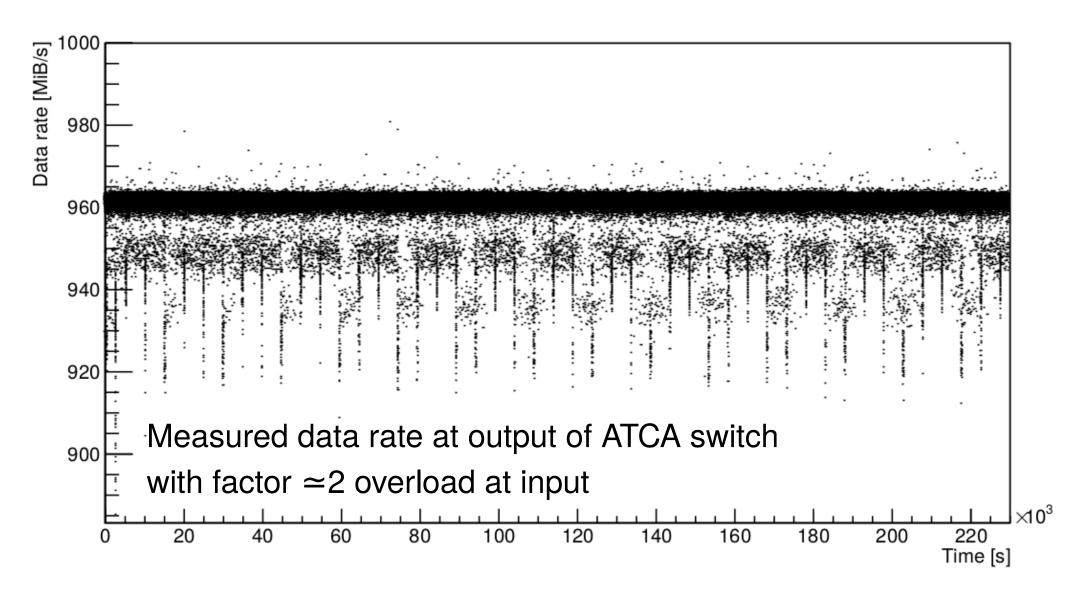

### Test of ATCA switch with 10G uplink

- Output from PXD system to event builder

- Is it possible to reduce 32 cables with 1G

by 1 cable with 10G?

- Does the switch break down?

- Is the buffer large enough?

ATCA ADLINK aTCA-3150 10G Uplink

ATCA ADLINK aTCA-3710 40G Uplink

### Test result of ATCA switch with 10G uplink

Klemens Lautenbach, Ph. D. thesis, [link]

### New ONSEN hardware

- New generation of ONSEN ATCA carrier board

- past: Xilinx Virtex-5 FX 70T

future: Xilinx Kintex Ultrascale 060

- factor 10 more FPGA resources

- factor ~2.5 higher link bandwidth (16.3 Gbps)

- New firmware developed (master thesis Matthäus Krein): link layer protocol changed from Aurora to AXI Stream

# **AI\* METHODS**

\*better terminology:

ML METHODS

(machine learning)

we use Neural Networks (NN)

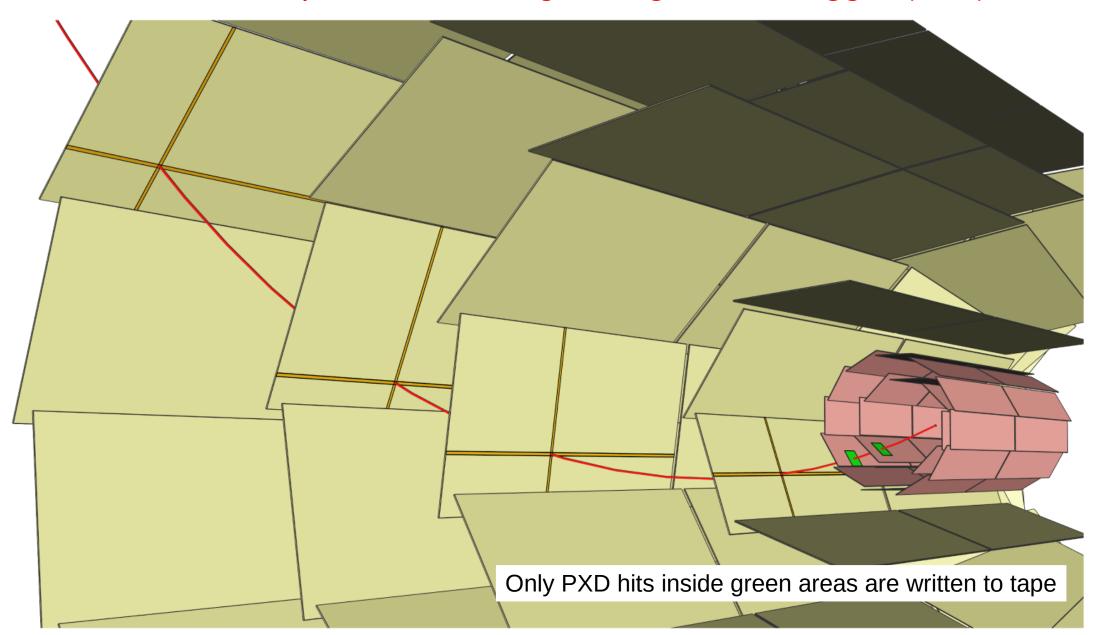

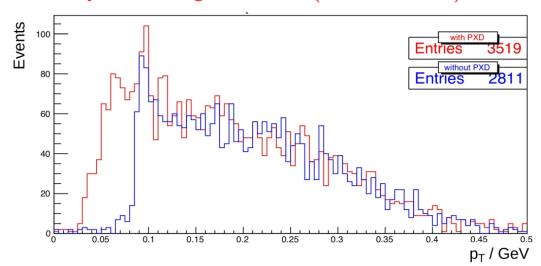

# Region-of-Interest (ROI) Selection based upon track finding on High Level Trigger (HLT)

#### **PXD** clusters

### **Ansatz**

- Problem:

- slow pions have high dE/dx and don't reach outer detectors (SVD, CDC)

- no HLT track

- no region-of-interest (ROI) in ONSEN system

- PXD hits are deleted online (before data reach the tape)

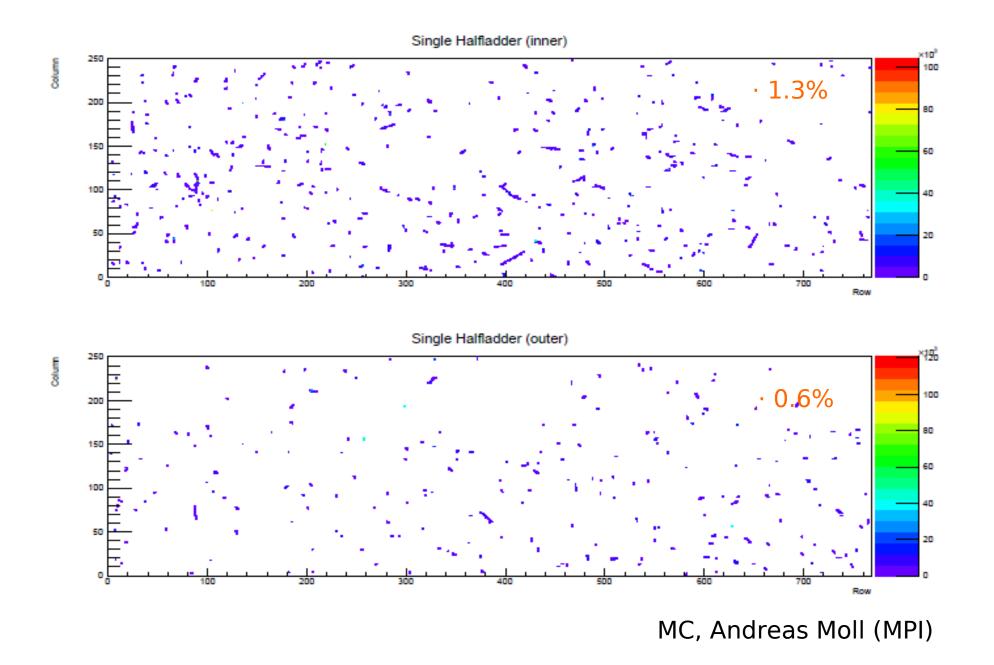

- Giessen ML approach:

- "cluster rescue"

- image processing

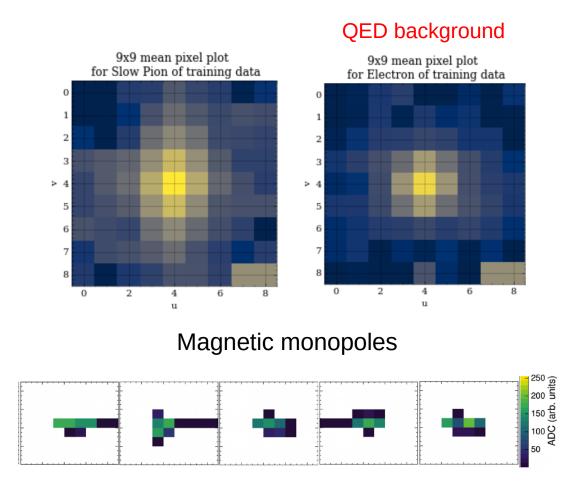

- $9\times9$  pixel images and global (x,y,z) position are input to Neural network (NN), ADC value is greyscale

- Ansatz applies to all highly ionizing particles:

slow pions, antideuterons, magnetic monopoles, ...

Example: slow  $\pi^-$  from  $D^{*-}$  in decay of a charged Z state (exotic hadron)

### 9x9 pixel matrix

Center of the matrix is the seed pixel (= pixel with max. charge)

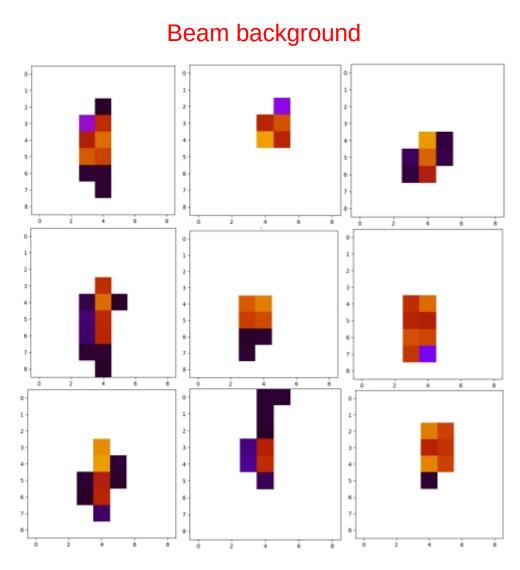

Reminder: Jennifer WP5, "background rejection"

- Beam background

- QED background (electrons)

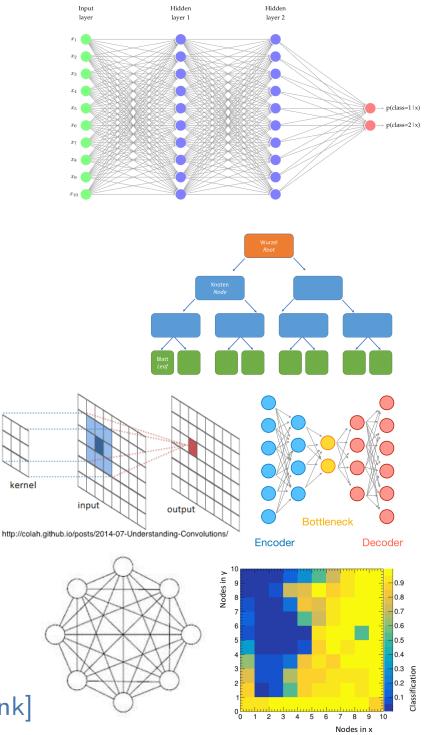

## NN projects, algorithms

| Multilayer perceptron          | Katharina Dort                |  |

|--------------------------------|-------------------------------|--|

| Self-Organizing Map            | Katharina Dort, Stephanie Käs |  |

| Hopfield NN                    | Irina Heinz                   |  |

| n-dim voxels                   | Johannes Bilk, Johannes Budak |  |

| Decision trees                 | Stephanie Käs                 |  |

| Convolutional NN               | Johannes Bilk                 |  |

| Support Vector Machines        | Timo Schellhaas               |  |

| Autoencoder                    | Katharina Dort                |  |

| Statistical methods (PCA, LDA) | Stephanie Käs                 |  |

| Graph NN                       | Martin Beyer                  |  |

- Results: slow pions can be classified with efficiency ≥80% and purity ≥80% (only based upon images of PXD clusters, no particle tracks!)

- Results published for magnetic monopoles

Anomaly detection

K. Dort et al., Eur. Phys. J. C 82 (2022) 7, 587, [link]

### NN projects, hardware implementation

- Tests at Giessen

- GPU (Marvin Peter, Kim Giebenhain), nVidia QUADRO GPU

- FINN Framework (Peter Lehnhardt), Xilinx Zync FPGA

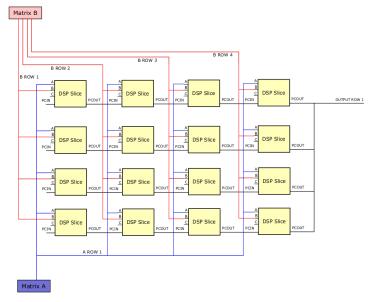

- DSP slices on FPGA (Falk Zorn), Xilinx Virtex FPGA (test of 4x4 matrix multiplication)

- Side remark: Belle II has a Neurotrigger in operation (KIT, TUM, BMBF project)

Figure 3: Schematic for DSP slice arrangement for the first calculation step.

### Plan

- upcoming 5 secondments for Giessen available

- Planning for 2023 started, 1<sup>st</sup> secondment in February

- Tasks will be defined, some preparation required.

| Task                         | Secondment sub-task                | Remark                            |

|------------------------------|------------------------------------|-----------------------------------|

| high bandwidth data transfer | new carrier board                  | requires extra<br>hardware at KEK |

| "AI"                         | focus on beam background rejection |                                   |

| sub-nanosecond timing        | (not needed for PXD)               | not discussed today               |

| parallelisation              | TODO                               | not discussed today               |

- reminder: PXD is decommissioned, work will focus on PXD2 installation

- some synergy with EURIZON project (next generation e+e- colliders):

Jennifer2: DAQ with large events (0.5 MB), high bandwidth

EURIZON: DAQ with small events, but very high trigger rates (400 kHz)

### Conclusion

- New situation: several subtasks related to WP 5.2 have been worked on in the past 3 years, funded by other sources.

- Future focus will be on PXD2

- Secondments can start in spring 2023, sub-tasks to be adapted

- Reminder: WP has only one deliverable

D5.2 (was due by month 36 in past timetable)

"REAL TIME WORKSHOP"

jointly on Belle II (PXD) and Hyper-K DAQ technologies

# **BACKUP**