## 1. Software & Firmware Requirements

Be sure that your Software and Firmware versions are up-to-date in order to use the different trigger settings explained in this document.

#### Minimum requirements:

- Firmware: Build >= v0.4 (later than 2022/06/08).

- Software: Build >= v1.1 (later than 2022/06/08).

### 1.1 Firmware & Software Repositories

- Fw: <u>https://drive.google.com/drive/folders/1dntus9AZZc2OQ27HnMgVEYeuPrHYeTWT?usp=sharing</u>

- Sw: <u>https://drive.google.com/drive/folders/1nuQTUB8zAX0AGc2fjoTY8\_rc0dZ8Yss6?usp=sharing</u>

Look for the latest \*.pof.svf file to permanently program the FPGA flash memory. As for the software, it is compiled for Debian-like distributions (Ubuntu), Red Hat Enterprise Linux distributions (CentOS, Scientific Linux), and Windows 7/10. Look for the binary of your favorite OS.

### 1.2 Checking Firmware & Software versions

- Fw: <beta\_binary> fw -v

- Sw: <beta\_binary> version

### 1.3 Upgrading Firmware

Go to the <u>firmware downloads page</u> and locate the directory *MAXv3.MEZv2.pof.svf* and look for the latest firmware version. Sorting the files by date can be very helpful.

The command to program the firmware is:

• <beta\_binary> fw -f <path\_to\_pof.svf>

# 2. Locating Trigger Signals in BETA test PCB

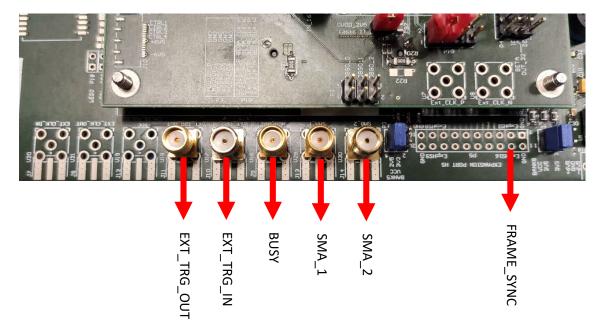

Figure 1:MAX10 Motherboard & BETA Mezzanine

The previous picture shows the SMA connectors and auxiliary debug pins used in the different trigger modes. The IO standard for all this signals is 2.5V CMOS (single-ended).

It is important to remark that FRAME\_SYNC pin is a copy of the differential FRAME\_SYNC signal (the one that goes from the FPGA to all the ASICs), and its purpose is merely for debugging purposes only.

### 2.1 SMA Signals:

- EXT\_TRG\_OUT:

- Direction: OUTPUT

- Purpose: Monitors the FPGA trigger signal. It can be helpful to understand what is the selected trigger we are using inside the FPGA.

- EXT\_TRG\_IN:

- Direction: INPUT

- Purpose: Allows to trigger the board using an external system (laser, ...) as a reference.

- BUSY:

- o Direction: OUTPUT

- Purpose: Tells to an external system that the board is currently processing an event, and therefore no new events can be processed (veto). This signal goes high few ns after the trigger signal and low once the ASIC readout is done.

- SMA\_1 / SMA\_2:

- Direction: OUTPUT

- Purpose: Allows the user to individually monitor the trigger output of an ASIC through the SMA connectors. This can be useful for troubleshooting problems.

## 3. BETA Trigger Modes

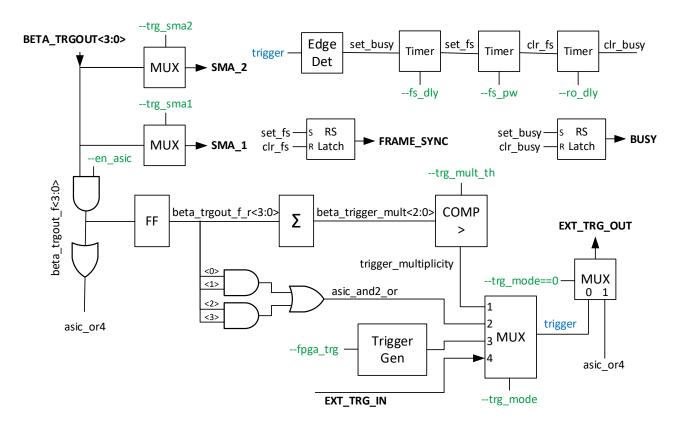

The following picture shows the trigger block diagram implemented on the FPGA. For a better understanding of the block, important signals have been highlighted.

- BOLD\_CAPITAL\_LETTERS: Trigger Block input/outputs. Most of them routed to SMA connectors. BETA\_TRGOUT<3:0> are the Fast-OR Trigger outputs of the 4 BETA ASICs in the board.

- --green\_parameters: Correspond to the name of the command option in the software *config* command. To modify any of these parameters:

- <beta\_bin> config --param\_1 <param\_val> ... --param\_n <param\_val>

For more information, type --help option.

- trigger: The internally selected trigger. This signal can be monitored via EXT\_TRG\_OUT SMA, except when trg\_mode is 0 (in that case the 4 ASICs Trigger OR is output). The rising edge of this trigger signal produces the FRAME\_SYNC and BUSY sequence by means of three timers. These timers can be adjusted by user.

Figure 2: Trigger Block Diagram

## 3.1 Enabling ASICs' Trigger output

For those cases where we want to ignore the trigger output a given ASIC (see Figure 2), either because the ASIC is broken or not mounted in the PCB, there is a command option for this purpose:

```

--en_asic <asic_id> <0/1> [ <asic_id> <0/1> ... <asic_id> <0/1> ]

```

In the following example we enable Trigger outputs from ASIC #0 & ASIC #1, and disable ASIC #2 & ASIC #3:

• <beta\_bin> config [other\_params] -en\_asic 0 1 1 1 2 0 3 0

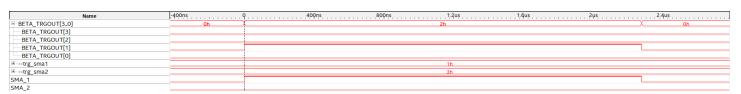

### 3.2 SMA1 & SMA2 Trigger debug

This capability allows the user to monitor a certain ASIC Trigger output. You can select 2 ASIC Trigger outputs independently. Parameters:

--trg\_sma1 < 0..3>

--trg\_sma2 <0..3>

*Figure 3: SMA\_2 connetor showing the output of BETA\_TRGOUT<1>*

Figure 4: SMA\_1 connetor showing the output of BETA\_TRGOUT<1>

### 3.3 Internal Trigger Mode

In this mode, trigger is simply the Fast-OR of the 4 ASICs, and there is no external control. Thus, data conversion will start after the delay time provided by --timer\_hold command option. In order to achieve the best performance, it is important to correctly align this signal with the peak of Chanel Shapers' output. Parameters:

--mode 0

--timer\_hold <time\_in\_ns>

--trg\_mode 0

Figure 5: EXT\_TRG\_OUT SMA showing the Fast-OR between BETA\_TRGOUT<3:0> signals

## 3.4 Multiplicity Trigger Mode (Pseudo-Internal Mode)

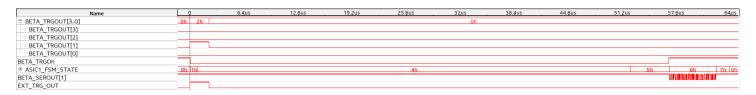

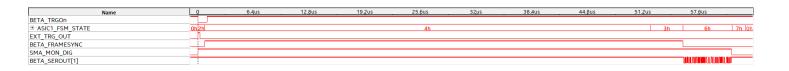

In this mode, trigger rises when the number of simultaneous triggering ASICs is higher than a certain threshold (--trg\_mult\_th). When this occurs, EXT\_TRG\_OUT SMA connector is high and the internal timers start counting to generate FRAME\_SYNC and BUSY signals.

When threshold is set to 0, the behavior is the same as in the Internal Trigger Mode (Section 3.2). However, in this mode ASIC trigger is externally controlled via FRAME\_SYNC.

The delay between trigger rising edge condition and FRAME\_SYNC rising edge is defined by --fs\_dly. The pulse width of FRAME\_SYNC (--fs\_pw) must be larger enough as to give enough time to the ASICs to perform the ADC conversion. The last timer (--ro\_dly) ensures that ASICs have finished data transmission before de asserting BUSY signal. All these values must be provided in nanoseconds. Note: the default values for --fs\_pw and --ro\_dly should work.

Parameters:

--mode 2

--trg\_mode 1

--trg\_mult\_th <0..3>

--fs\_dly <delay\_in\_ns>

| Name                       | 9     | 6.4us | 12.8us | 19.2us | 25.6us | 32,us | 38.4us | 44.8us | 51.2us | 57.6us |    |

|----------------------------|-------|-------|--------|--------|--------|-------|--------|--------|--------|--------|----|

| BETA_TRGOUT[30]            | Oh 2h |       |        |        |        | Qh    |        |        |        |        |    |

| BETA_TRGOUT[3]             |       |       |        |        |        |       |        |        |        |        |    |

| BETA_TRGOUT[2]             |       |       |        |        |        |       |        |        |        |        |    |

| BETA_TRGOUT[1]             |       |       |        |        |        |       |        |        |        |        |    |

| BETA_TRGOUT[0]             |       |       |        |        |        |       |        |        |        |        |    |

| BETA_TRGOn                 |       |       |        |        |        |       |        |        |        |        |    |

| ■ ASIC1_FSM_STATE          | Oh 2h |       |        |        | 4h     |       |        |        | 3h     | 6h     | 7h |

| ■ trg_mult_th              |       |       |        |        |        | 0     |        |        |        |        |    |

| ■ BETA_TRGOUT_MULTIPLICITY | Oh 1h |       |        |        |        | Oh    |        |        |        |        |    |

| EXT_TRG_OUT                |       |       |        |        |        |       |        |        |        |        |    |

| on_trigger                 |       |       |        |        |        |       |        |        |        |        |    |

| set_frame_sync             |       |       |        |        |        |       |        |        |        |        |    |

| clr_frame_sync             |       |       |        |        |        |       |        |        |        |        |    |

| BETA_FRAMESYNC             |       |       |        |        |        |       |        |        |        |        |    |

| set_busy                   |       |       |        |        |        |       |        |        |        |        |    |

| clr_busy                   |       |       |        |        |        |       |        |        |        |        |    |

| SMA_MON_DIG                |       |       |        |        |        |       |        |        |        |        |    |

| BETA_SEROUT[1]             |       |       |        |        |        |       |        |        |        |        |    |

Figure 6: EXT\_TRG\_OUT SMA goes high when the sum of triggering BETA\_TRGOUT<3:0> signals is higher than --trg\_mult\_th. BUSY signal (SMA\_MON\_DIG) goes high after trigger and goes low once the data transmission has finished. FRAME\_SYNC (BETA\_FRAMESYNC) goes high after a certain delay time and goes low sometime after the conversion has finished.

### 3.5 FPGA Trigger Generator Mode

In this mode the FPGA is internally generating the trigger at a certain rate. This rate is provided by --fpga\_trg parameter in kHz units. Parameters:

--mode 2

--trg\_mode 2

--fpga\_trg <0.1...6500>

--fs\_dly <delay\_in\_ns>

### 3.6 Exernal Trigger Mode (SMA EXT\_TRG\_IN)

In this mode, trigger occurs when EXT\_TRG\_IN SMA input goes high. FRAME\_SYNC and BUSY timers works as described in Section 3.3. EXT\_TRG\_OUT SMA will output the same signal with a certain latency (hundreds of picoseconds).

--mode 2

--trg\_mode 3

--fs\_dly <delay\_in\_ns>

| Name            | Q     | 6.4us | 12.8us | 19.2us | 25.6us | 32us | 38.4us | 44.8us | 51.2us | 57.6us |       |

|-----------------|-------|-------|--------|--------|--------|------|--------|--------|--------|--------|-------|

| BETA_TRGOn      |       |       |        |        |        |      |        |        |        |        |       |

| ASIC1_FSM_STATE | Oh 2h |       |        |        | 4h     |      |        |        | 3h     | 6h     | 7h Oh |

| EXT_TRG_IN      | _1    |       |        |        |        |      |        |        |        |        |       |

| EXT_TRG_OUT     |       |       |        |        |        |      |        |        |        |        |       |

| BETA_FRAMESYNC  |       |       |        |        |        |      |        |        |        |        |       |

| SMA_MON_DIG     |       |       |        |        |        |      |        |        |        |        |       |

| BETA_SEROUT[1]  |       |       |        |        |        |      |        |        |        |        |       |