Quest for a replacement of the Intel/ALTERA ArriaVGX dev. kit

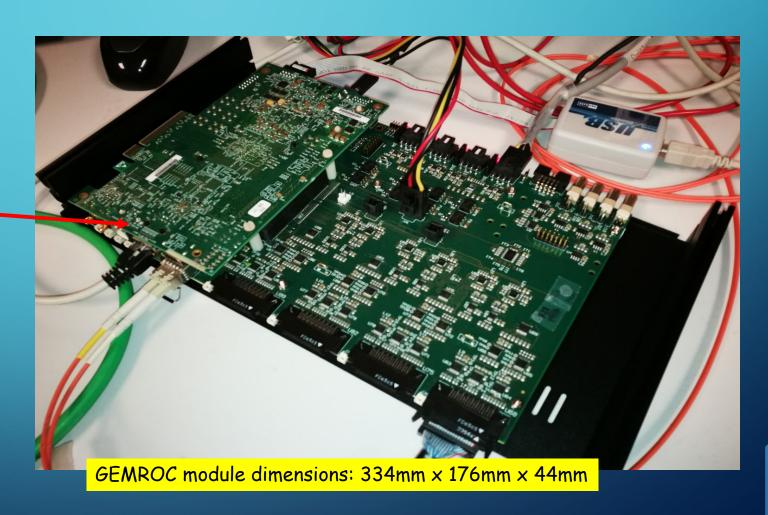

GEMROC: Off-detector readout card for BES-III CGEM-IT detector

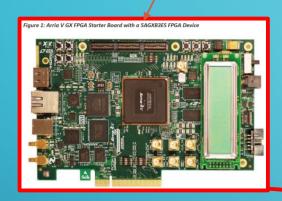

GEMROC = GEMROC\_InterFace Card (A.C.R.) + ArriaV GX development kit

(DK-START-5AGXB3N) (development kit production discontinued in 2020)

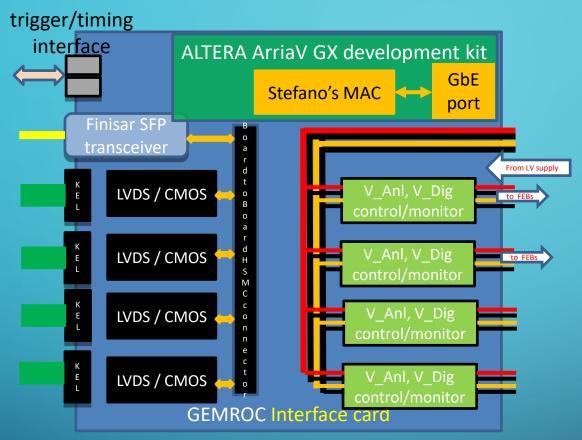

# GEMROC\_InterFace Card block diagram

The GEMROC module LV fanout section has 2 power input:

- VCC Anl

- VCC\_Dig

driven by the DETECTOR LV power supply mainframe, one channel of which supplies two GEMROC modules.

The GbE port of the FPGA module is used to receive commands to turn ON, turn OFF and read current for each of the 4 output power ports.

Power for the GEMROC itself comes from the independent "VCC\_GEMROC" input

Through the MAC unit designed by **Stefano Chiozzi**, **INFN-FE**, the Ethernet port of the GEMROC module supports:

- static IP (example: 192.168.1.aaa, with aaa determined by Board ID)

- UDP communication for LV FANOUT control by SLOW control system

- UDP communication for TIGER configuration by DAQ/RUN control system (PROPOSAL)

- UDP communication for diagnostic TIGER data readout (as for DAC scan tasks)

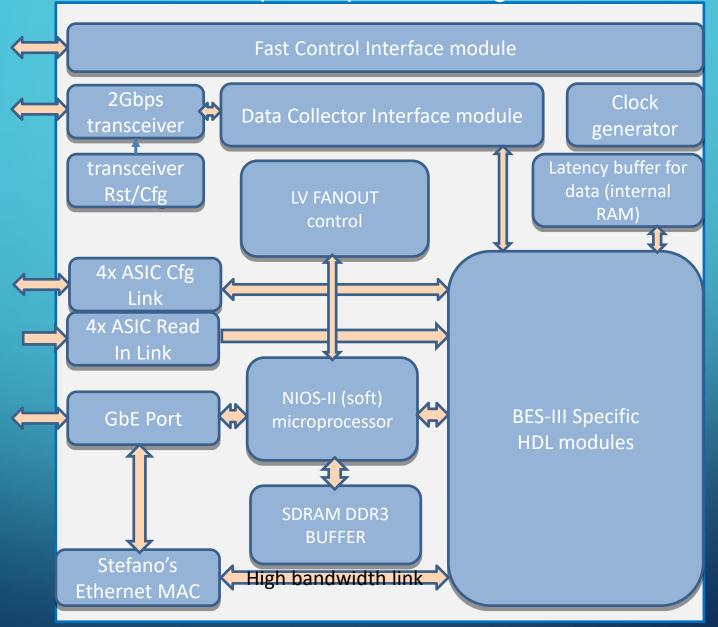

# GEMROC FPGA: firmware (A.C.R.) block diagram

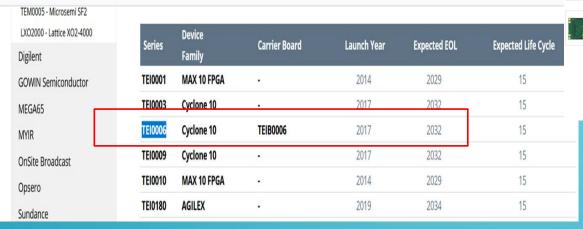

# ARRIA V GX DEV. KIT: ALTERA PART NUMBER DK-START-5AGXB3N

FPGA device: 5AGXFB3H4F35C4N Technology: TSMC's 28nm; Year launched 2011

Figure 1: Sample Ordering Code and Available Options for Arria V GX Devices

Cost: EUR 791,93 (nov 2019)

PDN: Dec 2020 but ran out of distributor's stock months before

FIND A REPLACEMENT !! (with, possibly, the same footprint)

| Embedded Hard IPS —————— B: No hard PCIe or hard memory controller M: 1 hard PCIe and 2 hard memory controllers F: 2 hard PCIe and 4 hard memory controllers                                                           | Transceiver Count D: 9 G: 18 H: 24 K: 36 | F: FineLine BGA (FBGA)  C: Commercial (T <sub>J</sub> = -0° C to 85° C)  I: Industrial (T <sub>J</sub> = -40° C to 100° C) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Family Signature 5A GX I<br>5A: Arria V                                                                                                                                                                                | F B5 H 4                                 | F 35 I 3 N                                                                                                                 |

| Family Variant                                                                                                                                                                                                         |                                          | Package Code 27 : 672 pins 31 : 896 pins G : RoHS5                                                                         |

| A1: 75K logic elements A3: 156K logic elements A5: 190K logic elements A7: 242K logic elements B1: 300K logic elements B3: 362K logic elements B5: 420K logic elements B5: 420K logic elements B7: 504K logic elements | Transceiver                              | G: RoHS6 35: 1,152 pins 40: 1,517 pins  G: RoHS6 P: Leaded (1)  -FPGA Fabric Speed Grade 3 (fastest) 4 5 6                 |

| Note:<br>1. Contact Intel for availability.                                                                                                                                                                            |                                          | Ü                                                                                                                          |

| Maximum Resources                                                                                                                                                                                                      |                                          |                                                                                                                            |

Table 4: Maximum Resource Counts for Arria V GX Devices

| Poso                       | Resource                   |         |         |         | Me      | mber Code | )       |         |         |

|----------------------------|----------------------------|---------|---------|---------|---------|-----------|---------|---------|---------|

| neso                       | urce                       | A1      | A3      | A5      | A7      | B1        | B3      | B5      | В7      |

| Logic Elements<br>(LE) (K) |                            | 75      | 156     | 190     | 242     | 300       | 362     | 420     | 504     |

| ALM                        |                            | 28,302  | 58,900  | 71,698  | 91,680  | 113,208   | 136,880 | 158,491 | 190,240 |

| Registe                    | er                         | 113,208 | 235,600 | 286,792 | 366,720 | 452,832   | 547,520 | 633,964 | 760,960 |

| Mem                        | M10K                       | 8,000   | 10,510  | 11,800  | 13,660  | 15,100    | 17,260  | 20,540  | 24,140  |

| ory<br>(Kb)                | MLAB                       | 463     | 961     | 1,173   | 1,448   | 1,852     | 2,098   | 2,532   | 2,906   |

|                            | Variable-<br>precision DSP |         | 396     | 600     | 800     | 920       | 1,045   | 1,092   | 1,156   |

| Pose             | ource                 |     | Member Code |       |       |       |       |       |       |  |  |  |  |  |

|------------------|-----------------------|-----|-------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

| nest             | Juice                 | A1  | A3          | A5    | A7    | B1    | B3    | B5    | В7    |  |  |  |  |  |

|                  | 18 x 18<br>Multiplier |     | 792         | 1,200 | 1,600 | 1,840 | 2,090 | 2,184 | 2,312 |  |  |  |  |  |

| PLL              | PLL                   |     | 10          | 12    | 12    | 12    | 12    | 16    | 16    |  |  |  |  |  |

| 6 Gbp<br>Transc  |                       | 9   | 9           | 24    | 24    | 24    | 24    | 36    | 36    |  |  |  |  |  |

| GPIO(            | (3)                   | 416 | 416         | 544   | 544   | 704   | 704   | 704   | 704   |  |  |  |  |  |

| LVD<br>S         | Transmit<br>ter       | 67  | 67          | 120   | 120   | 160   | 160   | 160   | 160   |  |  |  |  |  |

| 3                | Receiver              | 80  | 80          | 136   | 136   | 176   | 176   | 176   | 176   |  |  |  |  |  |

| PCIe I<br>Block  | Hard IP               | 1   | 1           | 2     | 2     | 2     | 2     | 2     | 2     |  |  |  |  |  |

| Hard I<br>Contro | Memory<br>oller       | 2   | 2           | 4     | 4     | 4     | 4     | 4     | 4     |  |  |  |  |  |

#### Related Information

High-Speed Differential I/O Interfaces and DPA in Arria V Devices chapter, Arria V Device Handbook

Provides the number of LVDS channels in each device package.

#### Package Plan

#### Table 5: Package Plan for Arria V GX Devices

| Member<br>Code | F672<br>(27 mm) |      | F896<br>(31 mm) |      | F11<br>(35) | 152<br>mm) | F1517<br>(40 mm) |      |  |

|----------------|-----------------|------|-----------------|------|-------------|------------|------------------|------|--|

|                | GPIO            | XCVR | GPIO            | XCVR | GPIO        | XCVR       | GPIO             | XCVR |  |

| A1             | 336             | 9    | 416             | 9    | _           | _          | _                | _    |  |

| A3             | 336             | 9    | 416             | 9    | _           | _          | _                | _    |  |

| A5             | 336             | 9    | 384             | 18   | 544         | 24         | _                | _    |  |

| A7             | 336             | 9    | 384             | 18   | 544         | 24         | _                | _    |  |

| B1             | _               | _    | 384             | 18   | 544         | 24         | 704              | 24   |  |

| В3             | _               | _    | 384             | 18   | 544         | 24         | 704              | 24   |  |

| B5             | _               | _    | _               | _    | 544         | 24         | 704              | 36   |  |

| B7             | _               | _    | _               | _    | 544         | 24         | 704              | 36   |  |

# CANDIDATES FOR THE REPLACEMENT OF THE ARRIA V GX DEV. KIT (NOT SAME FOOTPRINT UNFORTUNATELY)

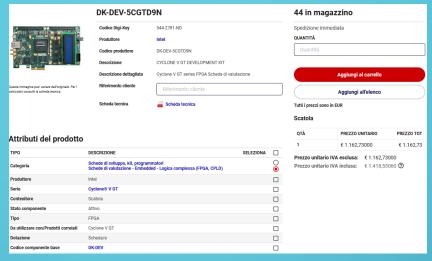

- 1) Cyclone V GT dev. kit Intel DK-DEV-5CGTD9N:

- onboard FPGA: 5CGTFD9E5F35C7N; year launched: 2011; TSMC's 28nm technology

- Status: active; cost: 1.162,73€ (current, Digikey)

- porting of GEMROC FPGA firmware (A.C.R.): fits with timing closure warnings

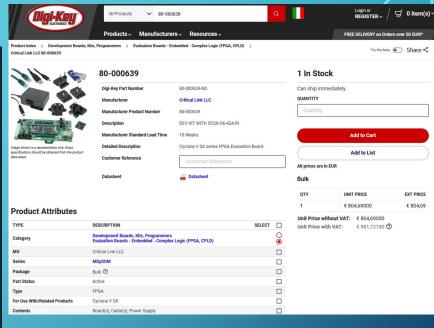

- 2) Cyclone V SX SoC dev. kit Critical Link MitySOM-5CSX:

- onboard FPGA: 5CSXFC6C6U23C7N (SoC); year launched: 2012

- Status: active; cost: 804,69€ (current, Digikey)

- porting of GEMROC FPGA firmware (A.C.R.): unsuccessful due to insufficient I/O

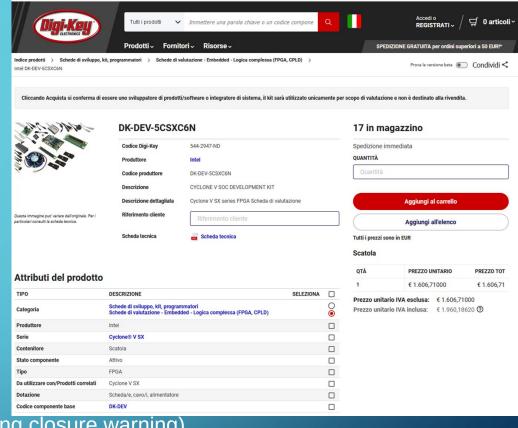

- Cyclone V SX SoC dev. kit Intel DK-DEV-5CSXC6N:

- onboard FPGA: 5CSXFC6D6F31C6N (SoC); year launched: 2011

- Status: active; cost: 1.606,71€ (current, Digikey)

- porting of GEMROC FPGA firmware (A.C.R.): fits with timing closure warnings for more pessimistic timing corners

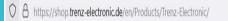

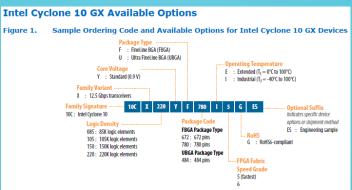

- 4) Cyclone 10 GX dev. kit Trenz TEI0006-03-220-5I:

- onboard FPGA: 10CX220YF780I5G; year launched: 2017; TSMC's 20nm technology

- Status: active; cost: 498.00€ (current, Trenz)

- accessory carrier board Trenz TEIB0006-02 cost: 179,00€ (current, Trenz)

- porting of GEMROC FPGA firmware (A.C.R.): in progress needs Quartus Pro Edition

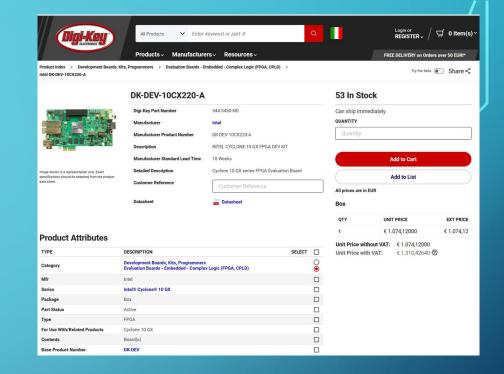

- 5) Cyclone 10 GX dev. kit Intel DK-DEV-10CX220-A:

- onboard FPGA: 10CX220YF780E5G; year launched: 2017; TSMC's 20nm technology

- Status: active; cost: 1.074,12€ (current, Digikey)

- porting of GEMROC FPGA firmware (A.C.R.): in progress needs Quartus Pro Edition

# 1) Cyclone V GT dev. kit Intel DK-DEV-5CGTD9N

## PRO of Cyclone V GT dev. kit:

- dev. kit status: active

- same outline as the Arria V GX dev. kit to be replaced

- current GEMROC firmware fits the onboard FPGA (with timing closure warning)

## CONS of Cyclone V GT dev. kit:

- onboard FPGA is mature. Status reported on the Intel web site: Launched in 2011

- development kit has different number/position of I/O connectors <-> not same footprint as the Arria V GX dev. kit to be replaced

- can't be adapted to the GEMROC module without redesigning the enclosure

- cost

# 1) Cyclone V GT dev. kit Intel DK-DEV-5CGTD9N

FPGA device: 5CGTFD9E5F35C7N

Table 1-3. Maximum Resource Counts for Cyclone V GX and GT Devices—Preliminary

| Resource                     |        | Cycl   | one V GX De | evice   |         | Cycl   | one V GT | Device |         |

|------------------------------|--------|--------|-------------|---------|---------|--------|----------|--------|---------|

| Resource                     | 5CGXC3 | 5CGXC4 | 5CGXC5      | 5CGXC7  | 5CGXC9  | 5CGTD5 | 5CGTD    | •      | 5CGTD9  |

| ALM                          | 11,698 | 18,868 | 28,868      | 56,415  | 113,585 | 28,868 | 56,415   |        | 113,585 |

| LE                           | 31,000 | 50,000 | 76,500      | 149,500 | 301,000 | 76,500 | 149,50   | )      | 301,000 |

| Block Memory (Kb)            | 1,400  | 2,500  | 3,800       | 6,500   | 11,600  | 3,800  | 6,500    | П      | 11,600  |

| MLAB Memory (Kb)             | 147    | 295    | 440         | 836     | 1,717   | 440    | 836      |        | 1,717   |

| Variable-precision DSP Block | 42     | 70     | 124         | 156     | 342     | 124    | 156      | П      | 342     |

| 18 x 19 Multiplier           | 84     | 140    | 248         | 312     | 684     | 248    | 312      | П      | 684     |

| Fractional PLL (1)           | 4      | 6      | 6           | 7       | 8       | 6      | 7        | П      | 8       |

| 3-Gbps Transceiver           | 3      | 6      | 6           | 9       | 12      | _      | _        | П      | _       |

| 5-Gbps Transceiver           | _      | _      | _           | _       | _       | 6      | 9        | П      | 12      |

| GPI0                         | 224    | 368    | 368         | 480     | 560     | 368    | 480      | П      | 560     |

| LVDS                         | 48     | 90     | 100         | 122     | 122     | 100    | 122      |        | 122     |

| PCIe Hard IP Block           | 1      | 2      | 2           | 2       | 2       | 2      | 2        |        | 2       |

| Hard Memory Controller       | 1      | 2      | 2           | 2       | 2       | 2      | 2        |        | 2       |

|                              | •      | •      |             | •       |         |        |          |        |         |

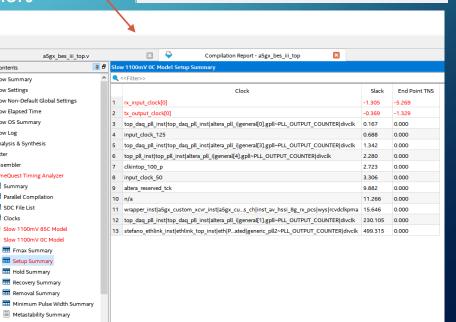

QUARTUS PRIME (STANDARD

VERSION) COMPILATION RESULTS:

## Flow summary:

Timing closure report:

paths with failing

(probably recoverable)

timing closure in all

parameter corners

|          | 0                               | _                                              |

|----------|---------------------------------|------------------------------------------------|

|          | Flow Summary                    |                                                |

|          | < <filter>&gt;</filter>         |                                                |

|          | Flow Status                     | Successful - Mon Jan 10 15:05:12 2022          |

|          | Quartus Prime Version           | 16.1.0 Build 196 10/24/2016 SJ Standard Editio |

|          | Revision Name                   | a5gx_bes_iii_top                               |

|          | Top-level Entity Name           | a5gx_bes_iii_top                               |

|          | Family                          | Cyclone V                                      |

|          | Device                          | 5CGTFD9E5F35C7                                 |

|          | Timing Models                   | Final                                          |

|          | Logic utilization (in ALMs)     | 21,675 / 113,560 (19 %)                        |

| <b>→</b> | Total registers                 | 49230                                          |

|          | Total pins                      | 179 / 616 ( 29 % )                             |

|          | Total virtual pins              | 0                                              |

|          | Total block memory bits         | 4,354,756 / 12,492,800 ( 35 % )                |

|          | Total DSP Blocks                | 3 / 342 ( < 1 % )                              |

|          | Total HSSI RX PCSs              | 1 / 12 (8 %)                                   |

|          | Total HSSI PMA RX Deserializers | 1 / 12 (8 %)                                   |

|          | Total HSSI TX PCSs              | 1 / 12 (8 %)                                   |

|          | Total HSSI PMA TX Serializers   | 1 / 12 (8 %)                                   |

|          | Total PLLs                      | 5 / 20 ( 25 % )                                |

|          | Total DLLs                      | 0/4(0%)                                        |

#### lote to Table 1-3:

The maximum fractional PLLs listed include general purpose PLLs and transceiver PLLs.

Table 1-6. Package Plan for Cyclone V E, GX, and GT Devices—Preliminary (1)

|            |               |      |               |      |                                         |   |               |      |               | I    |                 | 24420 |               |    |

|------------|---------------|------|---------------|------|-----------------------------------------|---|---------------|------|---------------|------|-----------------|-------|---------------|----|

|            | F250<br>(17 m |      | U324<br>(15 m |      | U484<br>(19 m                           |   | F484<br>(23 m |      | F67:<br>(27 m |      | F896<br>(31 mm) |       | F115<br>(35 m |    |

| Device     | GPIO          | XCVR | GPIO          | XCVR | GPIO GPIO GPIO GPIO GPIO GPIO GPIO GPIO |   | XCVR          | GPIO | XCVR          | GP10 | XCVR            |       |               |    |

| 5CEA2      | <b>▲</b> 144  | _    | <b>▲</b> 176  | _    | <b>288</b>                              | _ | ▲ 288         | _    | _             | _    | _               | _     | _             | _  |

| 5CEA4      | 144           | _    | 176           | _    | 288                                     | _ | 288           | _    | _             | _    | _               | _     | _             | _  |

| 5CEA5      | _             | _    | _             | _    | <b>7</b> 272                            | _ | <b>272</b>    | _    | _             | _    | _               | _     | _             | _  |

| 5CEA7      | _             | _    | _             | _    | 240                                     | _ | <b>4</b> 240  | _    | ▲ 336         | _    | <b>480</b>      | _     | _             | _  |

| 5CEA9      | _             | _    | _             | _    | _                                       | _ | 224           | _    | ▼ 336         | _    | <b>†</b> 448    | _     | _             | _  |

| 5CGXC3 (2) | _             | _    | 112           | 3    | <b>208</b>                              | 3 | <b>▲</b> 208  | 3    | _             | _    | _               | _     | _             | _  |

| 5CGXC4 (2) | _             | _    | _             | _    | 224                                     | 6 | 240           | 6    | <b>▲</b> 336  | 6    | _               | _     | _             | _  |

| 5CGXC5 (2) | _             | _    | _             | _    | 224                                     | 6 | 240           | 6    | 336           | 6    | _               | _     | _             | _  |

| 5CGXC7 (2) | _             | _    | _             | _    | 240                                     | 6 | 240           | 6    | 336           | 9    | <b>480</b>      | 9     | _             | _  |

| 5CGXC9 (2) | _             | _    | _             | _    | _                                       | _ | 224           | 6    | 336           | 9    | <b>448</b>      | 12    | 560           | 12 |

| 5CGTD5 (3) | _             | _    | _             | _    | <b>240</b>                              | 6 | <b>240</b>    | 6    | ▲ 368         | 6    | _               | _     | _             | _  |

| 5CGTD7 (3) | _             | _    | _             | _    | 240                                     | 6 | 240           | 6    | 336           | 9    | <b>480</b>      | 9     | _             | _  |

| 5CGTD9 (3) | _             | _    | _             | _    | _                                       | _ | 224           | 6    | ▼ 336         | 9    | <b>448</b>      | 12    | 560           | 12 |

- Notes to Table 1-6:

- (1) The arrows indicate the package vertical migration capability. You can also migrate your design across device densities in the same packaging option if the devices have the same dedicated pins, configuration pins, and power pins.

- (2) The transceiver counts listed are for 3-Gbps transceivers

- (3) The transceiver counts listed are for 5-Gbps transceivers

> Analysis & Synthesis

| Compilation report               | aug | x_5c5cop                                                                                 |         |           |

|----------------------------------|-----|------------------------------------------------------------------------------------------|---------|-----------|

| of Contents                      | Fas | t 1100mV 85C Model Setup Summary                                                         |         |           |

| Flow Summary ^                   | •   | < <filter>&gt;</filter>                                                                  |         |           |

| ■ Flow Settings                  |     | Clock                                                                                    | Slack   | End Point |

| Flow Non-Default Global Settings | 1   | rx_input_clock[0]                                                                        | -0.157  | -0.539    |

| Flow Elapsed Time                | 2   | tx_output_clock[0]                                                                       | 0.538   | 0.000     |

| Flow OS Summary                  | 3   | top_daq_pll_inst top_daq_pll_inst altera_pll_i general[0].gpll~PLL_OUTPUT_COUNTER divclk | 2.574   | 0.000     |

| Flow Log                         | 4   | top_daq_pll_inst top_daq_pll_inst altera_pll_i general[3].gpll~PLL_OUTPUT_COUNTER divclk | 3.856   | 0.000     |

| Analysis & Synthesis             | 5   | input_clock_125                                                                          | 3.876   | 0.000     |

| Fitter                           | 6   | top_pll_inst top_pll_inst altera_pll_i general[4].gpll~PLL_OUTPUT_COUNTER divclk         | 5.735   | 0.000     |

| Assembler                        | 7   | clkintop_100_p                                                                           | 5.929   | 0.000     |

| TimeQuest Timing Analyzer        | 8   | input_clock_50                                                                           | 6.251   | 0.000     |

| ■ Summary                        | 9   | altera_reserved_tck                                                                      | 11.795  | 0.000     |

| == Parallel Compilation          | 10  | n/a                                                                                      | 15.679  | 0.000     |

| ■ SDC File List                  | 11  | wrapper_inst a5gx_custom_xcvr_inst a5gx_cus_ch inst_av_hssi_8g_rx_pcs wys rcvdclkpma     | 16.766  | 0.000     |

| E Clocks                         | 12  | top_daq_pll_inst top_daq_pll_inst altera_pll_i general[1].gpll~PLL_OUTPUT_COUNTER divclk | 233.146 | 0.000     |

| Slow 1100mV 85C Model            | 13  | stefano_ethlink_inst ethlink_top_inst eth Pated generic_pll2~PLL_OUTPUT_COUNTER divclk   | 499.579 | 0.000     |

| Slow 1100mV 0C Model             |     |                                                                                          |         |           |

| max Summary                      |     |                                                                                          |         |           |

| setup Summary                    |     |                                                                                          |         |           |

| ■ Hold Summary                   |     |                                                                                          |         |           |

| Recovery Summary                 |     |                                                                                          |         |           |

| Removal Summary                  |     |                                                                                          |         |           |

| minimum Pulse Width Summary      |     |                                                                                          |         |           |

| Metastability Summary            |     |                                                                                          |         |           |

| Fast 1100mV 85C Model            |     |                                                                                          |         |           |

| setup Summary                    |     |                                                                                          |         |           |

| Hold Summary                     |     |                                                                                          |         |           |

Compilation Report - a5gx\_bes\_iii\_top

# 2) Cyclone V SX SoC dev. kit Critical Link MitySOM-5CSX

FPGA device: 5CSXFC6C6U23C7N

MitySOM MitySOM-5CSx System on Module 25 April 2019

## PRO of MitySOM-5CSX dev. kit:

- dev. kit status: active

- Similar outline as the Arria V GX dev. kit to be replaced

- current GEMROC firmware DOES NOT FIT on the onboard FPGA due to I/O pin count limitation of the onboard FPGA (but it might be used for the GEMROC Fanout modules)

- cost

## CONS of MitySOM-5CSX dev. kit:

- onboard FPGA is mature. Status reported on the Intel web site: Launched in 2011

- development kit has different number/position of I/O connectors <-> not same footprint as the Arria V GX dev. kit to be replaced

- could be adapted to the GEMROC module with little redesigning the enclosure

# 2) Cyclone V SX SoC dev. kit Critical Link MitySOM-5CSX

FPGA device: 5CSXFC6C6U23C7N

Table 1-5. Maximum Resource Counts for Cyclone V SX and ST Devices—Preliminary (Part 1 of 2)

|                 | esource               | C      | yclone V SX Devic | Cyclone V | ST Device |         |  |  |  |  |  |

|-----------------|-----------------------|--------|-------------------|-----------|-----------|---------|--|--|--|--|--|

| , n             | esource               | 5CSXC4 | 5CSXC5            | 5CSXC6    | 5CSTD5    | 5CSTD6  |  |  |  |  |  |

| ALM             |                       | 15,094 | 32,075            | 41,509    | 32,075    | 41,509  |  |  |  |  |  |

| LE              |                       | 40,000 | 85,000            | 110,000   | 85,000    | 110,000 |  |  |  |  |  |

| Block Memory    | (Kb)                  | 2,240  | 3,972             | 5,140     | 3,972     | 5,140   |  |  |  |  |  |

| MLAB Memory     | / (Kb)                | 220    | 480               | 621       | 480       | 621     |  |  |  |  |  |

| Variable-precis | ion DSP Block         | 58     | 87                | 112       | 87        | 112     |  |  |  |  |  |

| 18 x 19 Multip  | lier                  | 116    | 174               | 224       | 174       | 224     |  |  |  |  |  |

| FPGA Fractiona  | al PLL <sup>(1)</sup> | 5      | 6                 | 6         | 6         | 6       |  |  |  |  |  |

| HPS PLL         |                       | 3      | 3                 | 3         | 3         | 3       |  |  |  |  |  |

| 3-Gbps Transc   | eiver                 | 6      | 9                 | 9         | _         | _       |  |  |  |  |  |

| 5-Gbps Transc   | eiver                 | _      | _                 | _         | 9         | 9       |  |  |  |  |  |

| FPGA GPIO       |                       | 124    | 288               | 288       | 288       | 288     |  |  |  |  |  |

| HPS I/O         |                       | 188    | 188               | 188       | 188       | 188     |  |  |  |  |  |

| LVDS            |                       | 31     | 72                | 72        | 72        | 72      |  |  |  |  |  |

|                 |                       |        |                   |           |           |         |  |  |  |  |  |

Table 1-5. Maximum Resource Counts for Cyclone V SX and ST Devices—Preliminaly (Part 2 of 2)

| Decauses                       | C         | yclone V SX Devid | е         | Cyclone V ST Device |           |  |  |

|--------------------------------|-----------|-------------------|-----------|---------------------|-----------|--|--|

| Resource                       | 5CSXC4    | 5CSXC5            | 5CSXC6    | 5CSTD5              | 5CSTD6    |  |  |

| PCIe Hard IP Block             | 2         | 2                 | 2         | 2                   | 2         |  |  |

| FPGA Memory Controller         | 1         | 1                 | 1         | 1                   | 1         |  |  |

| HPS Memory Controller          | 1         | 1                 | 1         | 1                   | 1         |  |  |

| ARM Cortex-A9 MPCore Processor | Dual-core | Dual-core         | Dual-core | Dual-core           | Dual-core |  |  |

Note to Table 1-5:

Table 1-7. Package Plan for Cyclone V SE, SX, ar<mark>d ST Devices—*Preliminary* (1)</mark>

|                        |             |      |         |   |                 | ,    |         |     |      |                 |         |  |  |

|------------------------|-------------|------|---------|---|-----------------|------|---------|-----|------|-----------------|---------|--|--|

| U484<br>Device (19 mm) |             |      |         |   | U672<br>(23 mm) |      |         |     |      | F896<br>(31 mm) |         |  |  |

|                        | GPIO        | XCVR | HPS I/O |   | GPIO            | XCVR | HPS I/O |     | GP10 | XCVR            | HPS I/O |  |  |

| 5CSEA2                 | <b>▲</b> 66 | _    | 161     |   | <b>124</b>      | _    | 188     |     | _    | _               | _       |  |  |

| 5CSEA4                 | 66          | _    | 161     |   | 124             | _    | 188     |     | _    | _               | _       |  |  |

| 5CSEA5                 | 66          | _    | 161     |   | <b>▲</b> 124    | _    | 188     | A   | 288  | _               | 188     |  |  |

| 5CSEA6                 | ▼ 66        | _    | 161     |   | 124             | _    | 188     | ٧   | 288  | _               | 188     |  |  |

| 5CSXC4 (2)             | _           | _    | _       |   | 124             | 6    | 188     |     | _    | _               | _       |  |  |

| 5CSXC5 (2)             | _           | _    | _       |   | <b>124</b>      | 6    | 188     | 4   | 288  | 9               | 188     |  |  |

| 5CSXC6 (2)             | _           | _    | _       |   | 124             | 6    | 188     |     | 288  | 9               | 188     |  |  |

| 5CSTD5 (3)             | _           | _    | _       |   | _               | _    | _       |     | 288  | 9               | 188     |  |  |

| 5CSTD6 (3)             | _           | _    | -       |   | _               | _    | _       | ٧   | 288  | 9               | 188     |  |  |

|                        |             | . —  |         | _ |                 |      |         | . – |      |                 |         |  |  |

Notes to Table 1–7

(3) The transceiver counts listed are for 5-Ghps transceive

Resource count of the SOM Module's FPGA would fit the GEMROCformware design but not the FPGA's pin count.

Critical Link, LLC www.CriticalLink.com

#### **FEATURES**

MitySOM-5CSX Development Board

MitySOM-5CSX SoM Module

#### Additional Hardware Included:

- UART to USB Cable

- Ethernet Cable

- AC to DC 24V 2.7A Adapter

Integrated +2.5V/+3.3V/+5V/+12V Power Supplies

**ATX Power Supply Compatible**

#### Digital Interfaces:

- 10/100/1000 MBit Ethernet Interface

- Debug UART to USB

- USB OTG Interface

- Dual Electrically Isolated CAN Bus Interfaces

- SD/MMC Card Socket

#### Expansion

- Full HSMC Interface

- Partial HSMC Interface

PCI-e x4

Critical Link, LLC www.CriticalLink.com MitySOM MitySOM-5CSx System on Module 25 April 2019

#### FEATURES

- Intel Cyclone V U672 SoC

- Up To Dual ARM Cortex- A9 MPU

- 925MHz Max clock speed

- Dual NEON SIMD Coprocessors

- 32 KB L1 Program Cache (per core)

- 32 KB L1 Data Cache (per core)

512 KB L2 Cache (shared)

- 64 KB on-chip RAM

- ECC Support

- Up To 133 User FPGA I/O Pins

- 44 CPU I/O Pins

- 6 High speed transceivers (SX only)

#### Cyclone V Processor Choices

- Cyclone V SX (3.125 Gbps transceivers)

- Cyclone V SE

#### • Memory

6 August 2014

- Up To 2GB DDR3 CPU RAM x32 bits + ECC

- Up To 512MB DDR3 FPGA RAM x8 bits (optional)

- MitySOM-5CSX Develor.... Up To 272MB QPSI NOR FLASH

#### Mechanical

- 314-Pin Card Edge Connector

- Small 82mm (3.2") x 39mm (1.5") size

#### Hard Processor System (HPS)

- Selection of boot sources

- Up to 2 10/100/1000 Mbps Ethernet

MACs

- Up to 2 USB 2.0 OTG Ports

- Up to 2 CAN Interfaces

- Up to 2 UARTs

- 1 MMC/SD/SDIO

- Up to 4 I2C controllers

- Up to 2 master/2 slave SPI

- 3 HPS PLLs

#### Software and Documentation:

- Linux Kernel

- uBoot

- Development Environment Virtual Machine

- · Development Board Schematics

- Development Board Gerber Files

- Development Board BOM

#### APPLICATIONS

- MitySOM-5CSX Evaluation

- Test and Measurement

- Factory Automation

- Industrial Automation

- Embedded Instrumentation

- Test and Measurement

- Rapid Prototyping

<sup>(1)</sup> The maximum FPGA fractional PLLs listed include FPGA general purpose PLLs and transceiver PLLs.

<sup>(1)</sup> The arrows indicate the package vertical migration capa ility. You can also migrate your design across d vice densities in the same packaging option if the devices have the same dedicated pins, configuration pins, and power pins.

<sup>(2)</sup> The transceiver counts listed are for 3-Gbps transceiver

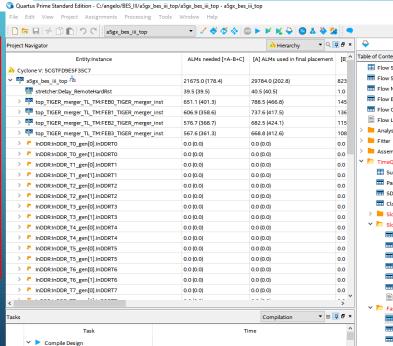

# 3) Cyclone V SX SoC dev. kit Intel DK-DEV-5CSXC6N

FPGA device: 5CSXFC6D6F31C6N

## PRO of Cyclone V SX dev. Kit Intel DK-DEV-5CSXC6N:

- dev. kit status: active

- current GEMROC firmware fits the onboard FPGA (with timing closure warning)

## CONS of Cyclone V SX dev. Kit Intel DK-DEV-5CSXC6N:

- onboard FPGA is mature. Status reported on the Intel web site: Launched in 2011

- development kit has different outline and number/position of I/O connectors <-> not same footprint as the Arria V GX dev. kit to be replaced

- can't be adapted to the GEMROC module without redesigning the enclosure / using an HSMC to HSMC cable adapter

- cost

# 3) Cyclone V SX SoC dev. kit Intel DK-DEV-5CSXC6N

FPGA device: 5CSXFC6D6F31C6N

Table 1-5. Maximum Resource Counts for Cyclone V SX and ST Devices—Preliminary (Part 1 of 2)

| Resource                     | С      | yclone V SX Devic | e       | Cyclone V | ST Device |

|------------------------------|--------|-------------------|---------|-----------|-----------|

| Kesource                     | 5CSXC4 | 5CSXC5            | 5CSXC6  | 5CSTD5    | 5CSTD6    |

| ALM                          | 15,094 | 32,075            | 41,509  | 32,075    | 41,509    |

| LE                           | 40,000 | 85,000            | 110,000 | 85,000    | 110,000   |

| Block Memory (Kb)            | 2,240  | 3,972             | 5,140   | 3,972     | 5,140     |

| MLAB Memory (Kb)             | 220    | 480               | 621     | 480       | 621       |

| Variable-precision DSP Block | 58     | 87                | 112     | 87        | 112       |

| 18 x 19 Multiplier           | 116    | 174               | 224     | 174       | 224       |

| FPGA Fractional PLL (1)      | 5      | 6                 | 6       | 6         | 6         |

| HPS PLL                      | 3      | 3                 | 3       | 3         | 3         |

| 3-Gbps Transceiver           | 6      | 9                 | 9       | _         | _         |

| 5-Gbps Transceiver           | _      | _                 | _       | 9         | 9         |

| FPGA GPIO                    | 124    | 288               | 288     | 288       | 288       |

| HPS I/O                      | 188    | 188               | 188     | 188       | 188       |

| LVDS                         | 31     | 72                | 72      | 72        | 72        |

QUARTUS PRIME (STANDARD **VERSION) COMPILATION RESULTS:**

Flow summary:

Fmax Summary

Setup Summary

Hold Summary

Recovery Summan

Removal Summary

East 1100mV 85C Model

Advanced I/O Timing

Multicorner Timing Analysis Summar

Timing closure report: paths with failing (probably recoverable) timing closure only for more pessimistic corners

Table 1-5. Maximum Resource Counts for Cyclone V SX and ST Devices—Prelimina v (Part 2 of 2)

|                                | C         | yclone V SX Devi | d <mark>e</mark> | Cyclone V | ST Device | Quartus Prime Standard Edition - C:/angelo/BES_III/a5gx_bes | _iii_top/a5gx_bes_iii_top - a5g | x_bes_iii_top |  |  |  |

|--------------------------------|-----------|------------------|------------------|-----------|-----------|-------------------------------------------------------------|---------------------------------|---------------|--|--|--|

| Resource                       | 5CSXC4    | 5CSXC5           | 5CSXC6           | 5CSTD5    | 5CSTD     |                                                             |                                 | 4 6 6         |  |  |  |

| PCIe Hard IP Block             | 2         | 2                | 2                | 2         | 2         | Project Navigator                                           |                                 |               |  |  |  |

| FPGA Memory Controller         | 1         | 1                | 1                | 1         | 1         | Entity:Instance                                             | ALMs needed [=A-B+C]            |               |  |  |  |

| HPS Memory Controller          | 1         | 1                | 1                | 1         | 1         | △ Cyclone V: 5CSXFC6D6F31C6                                 | ALL IS RECOGNET AT STEEL        | p q nen is as |  |  |  |

| ARM Cortex-A9 MPCore Processor | Dual-core | Dual-core        | Dual-core        | Dual-core | Dual-co   | Y 👼 a5gx_bes_iii_top 🛅                                      | 17528.0 (176.6)                 | 22972.5 (197  |  |  |  |

| Note to Table 1-5:             |           |                  |                  |           |           | stretcher:Delay_RemoteHardRst                               | 38.7 (38.7)                     | 39.4 (39.4)   |  |  |  |

Notes to Table 1-7:

<sup>(1)</sup> The maximum FPGA fractional PLLs listed include FPGA general purpose PLLs and transceiver PLLs.

| able 1–7. Package Pian for Cyclone V SE, SX, and ST Devices— <i>Preliminary</i> <sup>(1)</sup> |                 |      |         |                 |      |         |   |                 |      |         |  |

|------------------------------------------------------------------------------------------------|-----------------|------|---------|-----------------|------|---------|---|-----------------|------|---------|--|

| Device                                                                                         | U484<br>(19 mm) |      |         | U672<br>(23 mm) |      |         |   | F896<br>(31 mm) |      |         |  |

|                                                                                                | GPIO            | XCVR | HPS I/O | GPIO            | XCVR | HPS I/O | Г | GPIO            | XCVR | HPS I/O |  |

| 5CSEA2                                                                                         | <b>▲</b> 66     | _    | 161     | <b>▲</b> 124    | _    | 188     | Г | _               | _    | _       |  |

| 5CSEA4                                                                                         | 66              | _    | 161     | 124             | _    | 188     | Г | _               | _    | _       |  |

| 5CSEA5                                                                                         | 66              | _    | 161     | <b>124</b>      | _    | 188     | Г | ▲ 288           | _    | 188     |  |

| 5CSEA6                                                                                         | ▼ 66            | _    | 161     | ▼ 124           | _    | 188     | Г | <b>288</b>      | _    | 188     |  |

| 5CSXC4 (2)                                                                                     | _               | _    |         | 124             | 6    | 188     | Г | _               | _    | _       |  |

| 5CSXC5 (2)                                                                                     | _               | _    | _       | <b>124</b>      | 6    | 188     | Г | <b>288</b>      | 9    | 188     |  |

| 5CSXC6 (2)                                                                                     | _               | _    | _       | <b>124</b>      | 6    | 188     |   | 288             | 9    | 188     |  |

| 5CSTD5 (3)                                                                                     | _               | _    | _       | T -             | _    | _       |   | 288             | 9    | 188     |  |

| 5CSTD6 (3)                                                                                     | _               | _    | _       | _               | _    | _       |   | 288             | 9    | 188     |  |

(1) The arrows indicate the package vertical migration capability. You can also migrate your design actors device densities in the same packaging

option if the devices have the same dedicated pins, configuration pins, and power pins.

(2) The transceiver counts listed are for 3-Gbps transceivers.

(3) The transceiver counts listed are for 5-Ghps transceivers.

▼ Q 🗓 🗗 × 🔷 oject Navigator ALMs needed [=A-B+C] [A] ALMs used in final placement ^ Table of Contents Entity/Instance Flow Summary Cyclone V: 5CSXFC6D6F31C6 Flow Settings a5gx\_bes\_iii\_top 🛅 17528.0 (176.6) 22972.5 (197.9) Flow Non-Default Global Settings stretcher:Delay RemoteHardRst 39.4 (39.4) Flow Elapsed Time top\_TIGER\_merger\_TL\_TM:FEBO\_TIGER\_merger\_inst 579.4 (352.6) 722.3 (425.3) Flow OS Summary top TIGER\_merger\_TL\_TM:FEB1\_TIGER\_merger\_inst 708.3 (407.1) Flow Log top\_TIGER\_merger\_TL\_TM:FEB2\_TIGER\_merger\_inst 658.2 (419.8) Analysis & Synthesis Fitter InDDR:InDDR\_T0\_gen[0].InDDRT0 0.0 (0.0) 0.0 (0.0) Assemble InDDR:InDDR\_T0\_gen[1].InDDRT0 0.0 (0.0) ▼ TimeQuest Timing Analyze InDDR:InDDR T1 gen[0].InDDRT1 0.0 (0.0) 0.0 (0.0) Summary InDDR:InDDR\_T1\_gen[1].InDDRT1 0.0 (0.0) 0.0 (0.0) == Parallel Compilation 0.0 (0.0) InDDR:InDDR\_T2\_gen[0].InDDRT2 0.0 (0.0) SDC File List InDDR:InDDR T2 gen[1].InDDRT2 0.0 (0.0) 0.0 (0.0) InDDR:InDDR T3 gen[0].InDDRT3 0.0 (0.0) 0.0 (0.0) Slow 1100mV 85C Mode InDDR:InDDR\_T3\_gen[1].InDDRT3 0.0 (0.0) 0.0 (0.0) ✓ F

Slow 1100mV 0C Model InDDR:InDDR T4 gen[0].InDDRT4 0.0 (0.0) 0.0 (0.0) InDDR:InDDR\_T4\_gen[1].InDDRT4 0.0 (0.0) 0.0 (0.0) InDDR:InDDR\_T5\_gen[0].InDDRT5 0.0 (0.0) 0.0 (0.0) 0.0 (0.0) InDDR:InDDR\_T5\_gen[1].InDDRT5 0.0 (0.0) InDDR:InDDR T6 gen[0].InDDRT6 0.0 (0.0) 0.0 (0.0) 0.0 (0.0) InDDR:InDDR\_T6\_gen[1].InDDRT6 InDDR:InDDR\_T7\_gen[0].InDDRT7 0.0 (0.0) Compilation ▼ **□** ₽ × Fast 1100mV 0C Model

✓ Compile Design

Flow Summary <<Filter>> Flow Status Successful - Thu Feb 03 09:59:48 2022 Quartus Prime Version 16.1.0 Build 196 10/24/2016 SJ Standard Edition Revision Name a5gx bes iii top Top-level Entity Name a5gx bes iii top Family Cyclone V 5CSXFC6D6F31C6 Device Timing Models Final 17,528 / 41,910 ( 42 % ) Logic utilization (in ALMs) 35487 Total registers 179 / 499 (36 %) Total pins Total virtual pins Total block memory bits 4,067,396 / 5,662,720 (72 %) Total DSP Blocks 3 / 112 (3%) Total HSSI RX PCSs 1/9(11%) Total HSSI PMA RX Deserializers 1/9(11%) Total HSSI TX PCSs 1/9(11%) Total HSSI PMA TX Serializers 1/9(11%) Total PLLs 5 / 15 (33 %)

0/4(0%)

Total DLLs

# 4) Cyclone 10 GX dev. kit Trenz TEI0006-03-220-51

FPGA device: 10CX220YF780I5G

NOTE: porting of GEMROC firmware onto this platform in progress (A.C.R.): moving to Quartus Pro 20.4 (QSys → Platform Developer) requires updating all currently instantiated Intel/ALTERA IP blocks

## PRO of Cyclone 10 GX dev. kit Trenz TEI0006-03-220-5I:

- dev. kit status: active;

- onboard FPGA (20nm TSMC) launched in 2017 with EOL in 2032

- Small outline: 6cm x 8cm

- •/ cost

## CONS of Cyclone 10 GX dev. kit Trenz TEI0006-03-220-5I:

- neither the module itself nor the motherboard carrying the module (see next slide) have number/position of I/O connectors compatible the Arria V GX dev. kit to be replaced

- a dedicated adapter to the GEMROC module would have to be designed; it could be made to fit the existing GEMROC module enclosure

#### €498.00 (592.62 € gross) \*

expected to be available on 05-Aug-2022

| 1.0             | Man to shopping care       |  |

|-----------------|----------------------------|--|

| Remember        |                            |  |

| Order number:   | TEI0006-03-220-5I          |  |

| In Stock:       | 0                          |  |

| Article status: | Full production            |  |

| Quantity        | Unit price                 |  |

| To 9            | €498.00 (592.62 € gross) * |  |

| From 10         | €448.20 (533.36 € gross) * |  |

| From 25         | €448 20 (533 36 € gross) * |  |

Contacts with Trenz to see if prototypes could be obtained sooner. Lead time is due to contingent semiconductors shortage

#### Product information "FPGA Module with Intel Cyclone 10 GX 10CX220, 2 GByte DDR3L, 6 x 8 cm"

The predecessor of this article is TEI0006-02-220-5I. All changes are in the Product Change Notification (PCN).

The Trenz Electronic TEI0006 is an industrial grade module based on Intel Cyclone 10 GX. The Intel Cyclone 10 GX device family delivers higher core, transceiver, and I/O performance than the previous generation of low cost FPGAs.

#### **Key Features**

- Intel Cyclone 10 GX Industrial [10CX220YF780I5G]

- Package: FBGA-780

- Speed Grade: 5 (Fastest)

- Temperature: -40°C to 100°C

- Package compatible device, 10CX150 and 10CX105 as assembly variant on reques

- 2 x SDRAM DDR3L memory IC 8 Gbit (1 GByte), Half rate: 533 MHz; Quarter rate: max. 800 MHz

- 2 x SPI Flash, 1 Gbit (128 MBvte)

- 1 x Gigabit Ethernet

- · Programmable oscillator

- Intel MAX 10 as system controller (CPLD)

- 2 KBit EEPROM memory

- 4 x User LEDs

- I/O interfaces: 226/94/46 (IO's/DIFF. Pairs/LVDS Pairs)

- Board to Board (B2B) connection: plug-on module with 3 x 160-pin Samtec Razor Beam (ST5) connectors

- 5 V power supply

- size: 6 x 8 cm

## 4) Cyclone 10 GX dev. kit Trenz TEI0006-03-220-5I

FPGA device: 10CX220YF780I5G

Intel® Cyclone® 10 GX Device Overview 683485 | 2019.04.01

## **Intel Cyclone 10 GX Maximum Resources**

Table 4. Maximum Resource Counts for Intel Cyclone 10 GX Devices

|                              | Resource              |         | Produc  | ct Line |         |

|------------------------------|-----------------------|---------|---------|---------|---------|

|                              |                       | 10CX085 | 10CX105 | 10CX150 | 10CX220 |

| Logic Eler                   | ments (LE) (K)        | 85      | 104     | 150     | 220     |

| ALM                          |                       | 31,000  | 38,000  | 54,770  | 80,330  |

| Register                     |                       | 124,000 | 152,000 | 219,080 | 321,320 |

| Memory                       | M20K                  | 5,820   | 7,640   | 9,500   | 11,740  |

| (Kb)                         | MLAB                  | 653     | 799     | 1,152   | 1,690   |

| Variable-precision DSP Block |                       | 84      | 125     | 156     | 192     |

| 18 x 19 Multiplier           |                       | 168     | 250     | 312     | 384     |

| Hard Floa                    | ting-point Arithmetic | Yes     | Yes     | Yes     | Yes     |

| PLL                          | Fractional Synthesis  | 2       | 4       | 4       | 4       |

|                              | I/O                   | 4       | 6       | 6       | 6       |

| 12.5 Gbps                    | ps Transceiver 6      |         | 12      | 12 12   |         |

| GPIO (2)                     |                       | 216     | 284     | 284     | 284     |

| LVDS Pair                    | (3)                   | 84      | 118     | 118     | 118     |

| PCIe Hard                    | I IP Block            | 1       | 1       | 1       | 1       |

| Hard Men                     | nory Interfaces       | 1       | 2       | 2       | 2       |

#### **Intel Cyclone 10 GX Package Plan**

#### Table 5. Package Plan for Intel Cyclone 10 GX Devices

The GPIO numbers include the I/O pins in the LVDS and 3 VI/O banks. In each device package, there is one 3 VI/O bank (48 pins).

| _                 |               |      |                    |      |        |                    |      |                      |      |      |  |

|-------------------|---------------|------|--------------------|------|--------|--------------------|------|----------------------|------|------|--|

| Product Line Type |               | 41   | U484<br>34-pin UB( | GA.  | 67     | F672<br>72-pin FB6 | iΑ   | F780<br>780-pin FBGA |      |      |  |

|                   | Size          | 19   | mm × 19            | mm   | 27     | mm × 27 ı          | mm   | 29 mm × 29 mm        |      |      |  |

|                   | Ball<br>Pitch |      | 0.8 mm             |      | 1.0 mm |                    |      | 1.0 mm               |      |      |  |

|                   | I/O<br>Type   | GPI0 | LVDS               | XCVR | GPI0   | LVDS               | XCVR | GPI0                 | LVDS | XCVR |  |

| 10CX08            | 35            | 188  | 70                 | 6    | 216    | 84                 | 6    | -                    | -    | _    |  |

| 10CX10            | )5            | 188  | 70                 | 6    | 236    | 94                 | 10   | 284                  | 118  | 12   |  |

| 10CX15            | 50            | 188  | 70                 | 6    | 236    | 94                 | 10   | 284                  | 118  | 12   |  |

| 10CX22            | 20            | 188  | 70                 | 6    | 236    | 94                 | 10   | 284                  | 118  | 12   |  |

| 10CX22            | 20            | 188  | 70                 | 6    | 236    | 94                 | 10   | 284                  | 11   | 8    |  |

<sup>(2)</sup> The number of GPIOs does not include transceiver I/Os. In the Intel Quartus Prime Pro Edition software, the number of user I/Os includes transceiver I/Os.

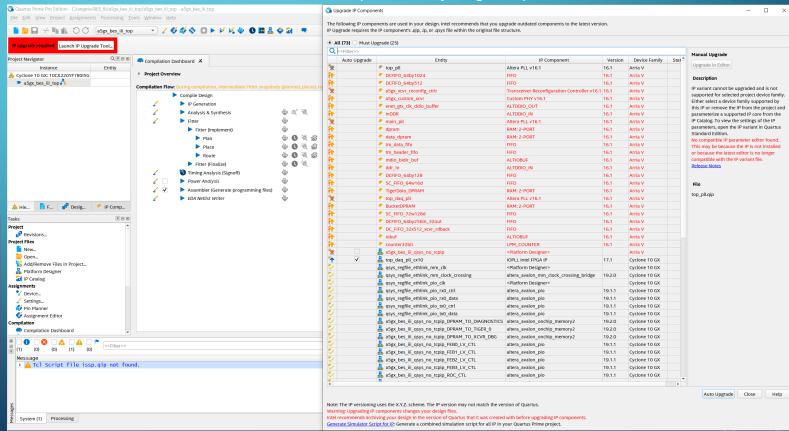

# QUARTUS PRIME PRO EDITION 20.4 COMPILATION RESULTS: MANUAL IP UPGRADE IS REQUIRED (work in progress)

<sup>(3)</sup> Each LVDS I/O pair can be used as differential input or output.

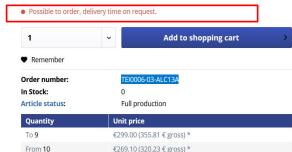

# 4bis Cyclone 10 GX dev. kit Trenz TEI0006-03-ALC13A

FPGA device: 10CX105YF780E5G

Product information "FPGA Module with Intel Cyclone 10 GX 10CX105, 128 MByte DDR3L, 8 x 6 cm'

The Trenz Electronic TEI0006 is an industrial grade module based on Intel Cyclone 10 GX. The Intel Cyclone 10 GX device family delivers higher core, transceiver, and I/O performance than the previous generation of low cost FPGAs.

#### **Key Features**

- Intel Cyclone 10 GX Industrial [10CX105YF780E5G]

- Package: FBGA-780

- Chood Grado: E (Eac

- o Temperature: -40°C to 100°C

- Package compatible device, 10CX150 and 10CX105 as assembly variant on request

- 128 MBvte DDR3L SDRAM

- 2 x SPI Flash, 1 Gbit (total: 256 MByte)

- 1 x Gigabit Ethernet

- · Programmable oscillator

- Intel MAX 10 as system controller (CPLD)

- 2 KBit EEPROM memory

- 4 x User LEDs

- I/O interfaces: 226/94/46 (IO's/DIFF. Pairs/LVDS Pairs)

- Board to Board (B2B) connection: plug-on module with 3 x 160-pin Samtec Razor Beam (ST5) connectors

- 5 V power supply

- size: 6 x 8 cm

A less performant, same footprint version of the Trenz Cyclone 10 GX dev. kit of the previous slide exist

It could be matched to less demanding applications PROs of Cyclone 10 GX dev. kit Trenz TEI0006-03-ALC13A:

- dev. kit status: active;

- onboard FPGA (20nm TSMC) launched in 2017 with EOL in 2032

- small outline: 6cm x 8cm

- cost

FPGA Module with Intel Cyclone 10 GX 10CX105, 128 MByte DDR3L, 8 x 6 cm

## €299.00 (355.81 € gross) \*

Prices plus VAT plus shipping costs

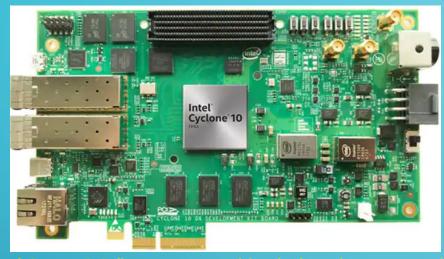

# 4ter) Cyclone 10 GX dev. kit Trenz carrier board

The simple and functional carrier board shown below provides expansion ports (Ethernet, SFP, FMC) to the Cyclone 10 GX modules presented in the previous slides

# 5) Cyclone 10 GX dev. kit Intel DK-DEV-10CX220-A

FPGA device: 10CX220YF780E5G

NOTE: porting of GEMROC firmware onto this platform in progress (A.C.R.): moving to Quartus Pro 20.4 (QSys → Platform Developer) requires updating all currently instantiated Intel/ALTERA IP blocks

PRO of Cyclone 10 GX dev. kit Intel DK-DEV-10CX220-A:

- dev. kit status: active;

- onboard FPGA (20nm TSMC) launched in 2017 with EOL in 2032

- similar outline as the Arria V GX dev. kit to be replaced

- cost

CONS of Cyclone 10 GX dev. kit Intel DK-DEV-10CX220-A:

- the module has a footprint NOT COMPATIBLE, for number/position of I/O connectors, with the Arria V GX dev. kit to be replaced

- a dedicated adapter to the GEMROC module would have to be designed; it could probably be made to fit the existing GEMROC module enclosure

# 5) Cyclone 10 GX dev. kit Intel DK-DEV-10CX220-A

FPGA device: 10CX220YF780E5G

Intel® Cyclone® 10 GX Device Overview 683485 | 2019.04.01

#### **Intel Cyclone 10 GX Maximum Resources**

#### Table 4. Maximum Resource Counts for Intel Cyclone 10 GX Devices

|            |                          |         | -       |         |         |

|------------|--------------------------|---------|---------|---------|---------|

|            | Resource                 |         | Produc  | ct Line |         |

|            |                          | 10CX085 | 10CX105 | 10CX150 | 10CX220 |

| Logic Eler | ments (LE) (K)           | 85      | 104     | 150     | 220     |

| ALM        |                          | 31,000  | 38,000  | 54,770  | 80,330  |

| Register   |                          | 124,000 | 152,000 | 219,080 | 321,320 |

| Memory     | M20K                     | 5,820   | 7,640   | 9,500   | 11,740  |

| (Kb)       | MLAB                     | 653     | 799     | 1,152   | 1,690   |

| Variable-p | e-precision DSP Block 84 |         | 125     | 156     | 192     |

| 18 x 19 M  | Iultiplier               | 168     | 250     | 312     | 384     |

| Hard Floa  | ting-point Arithmetic    | Yes     | Yes     | Yes     | Yes     |

| PLL        | Fractional Synthesis     | 2       | 4       | 4       | 4       |

|            | I/O                      | 4       | 6       | 6       | 6       |

| 12.5 Gbps  | Transceiver              | 6       | 12      | 12      | 12      |

| GPIO (2)   |                          | 216     | 284     | 284     | 284     |

| LVDS Pair  | (3)                      | 84      | 118     | 118     | 118     |

| PCIe Hard  | IP Block                 | 1       | 1       | 1       | 1       |

| Hard Men   | nory Interfaces          | 1       | 2       | 2       | 2       |

|            |                          |         |         |         |         |

#### **Intel Cyclone 10 GX Package Plan**

#### Table 5. Package Plan for Intel Cyclone 10 GX Devices

The GPIO numbers include the I/O pins in the LVDS and 3 VI/O banks. In each device package, there is one 3 VI/O bank (48 pins).

| _                 |               |      |                    |      |        |                    |      |                      |      |      |  |

|-------------------|---------------|------|--------------------|------|--------|--------------------|------|----------------------|------|------|--|

| Product Line Type |               | 41   | U484<br>34-pin UB( | GA.  | 67     | F672<br>72-pin FB6 | iΑ   | F780<br>780-pin FBGA |      |      |  |

|                   | Size          | 19   | mm × 19            | mm   | 27     | mm × 27 ı          | mm   | 29 mm × 29 mm        |      |      |  |

|                   | Ball<br>Pitch |      | 0.8 mm             |      | 1.0 mm |                    |      | 1.0 mm               |      |      |  |

|                   | I/O<br>Type   | GPI0 | LVDS               | XCVR | GPI0   | LVDS               | XCVR | GPI0                 | LVDS | XCVR |  |

| 10CX08            | 35            | 188  | 70                 | 6    | 216    | 84                 | 6    | -                    | -    | _    |  |

| 10CX10            | )5            | 188  | 70                 | 6    | 236    | 94                 | 10   | 284                  | 118  | 12   |  |

| 10CX15            | 50            | 188  | 70                 | 6    | 236    | 94                 | 10   | 284                  | 118  | 12   |  |

| 10CX22            | 20            | 188  | 70                 | 6    | 236    | 94                 | 10   | 284                  | 118  | 12   |  |

| 10CX22            | 20            | 188  | 70                 | 6    | 236    | 94                 | 10   | 284                  | 11   | 8    |  |

<sup>(2)</sup> The number of GPIOs does not include transceiver I/Os. In the Intel Quartus Prime Pro Edition software, the number of user I/Os includes transceiver I/Os.

# QUARTUS PRIME PRO EDITION 20.4 COMPILATION RESULTS: MANUAL IP UPGRADE IS REQUIRED (work in progress)

<sup>(3)</sup> Each LVDS I/O pair can be used as differential input or output.

# Migrating designs to the Intel Quartus Pro Edition

## Intel® Quartus® Prime Standard Edition

The Intel® Quartus® Prime Standard Edition Software includes extensive support for earlier device families in addition to the Intel® Cyclone® 10 LP device family.

## Intel® Quartus® Prime Pro Edition

The Intel® Quartus® Prime Pro Edition Software is optimized to support the advanced features in next-generation FPGAs and SoCs with the Intel® Agilex™, Intel® Stratix® 10, Intel® Arria® 10, and Intel® Cyclone® 10 GX device families.

# Migrating designs to the Intel Quartus Pro Edition

## Update Assignments to Reference Instances Only

#### Other Intel® Quartus® Prime software products

- Assignments to instantiated entities must reference both entity and instance names in project hierarchy

- Example: entity a:a|entity b:b|entity c:c

#### Quartus Prime Pro Edition

- Entity names should no longer be used in assignments; use instance names only

- Entity names still accepted by the compiler (for now) but are ignored and generate warning messages

- Example: a|b|c

Action: remove entity names from existing assignments directly in .qsf file or through Assignment Editor, and avoid using them in new assignments

### Check Entity Name Use in .sdc and Related Scripts

#### Other Intel® Quartus® Prime software products

Supports use of both entity and instances names for constraints, similar to their use in project assignments

#### Intel Quartus Prime Pro Edition

- Continues to support use of both entity and instance names with no generated warnings

- However, certain commands in scripts that perform custom name processing return strings without entity names

- Processing of returned strings must reflect this

- get\_registers example that works in all Quartus products due to wildcard use:

### Check References to Synthesized Node Names

- Names may change significantly between other Intel® Quartus® Prime software product projects and Intel Quartus Prime Pro Edition

- Names never guaranteed to remain consistent in other Quartus software products

- More significant changes when moving to Pro Edition

- Example: foo~123 may synthesize in Pro Edition as foo.567

- Check .qsf, .sdc, and Tcl script references to synthesized nodes

- Use Node Finder to help locate and fix

- Also check names of duplicated registers and PLL clock outputs

# intel

# Migrating to the Intel® Quartus® Prime Pro

## Software

## How Do I Migrate?

- Update your project assignments (.qsf), timing constraints (.sdc), and Tcl scripts

- Regenerate your IP

- Adjust your RTL for the new Intel® Quartus® Prime Pro synthesis engine

## Why Regenerate IP?

## In other Intel® Quartus® Prime Software products

- Proprietary Verilog configuration scheme used in the top level of all IP cores and Platform Designer for synthesis

- Prevents ambiguous instantiation errors during synthesis due to identical naming or multiple instantiations of RTL entities

- Still potential for such errors during simulation, requiring a fix

- Create separate Verilog configuration

- Delete duplicate entities

- Rename conflicting entities

#### In Intel Quartus Prime Pro Edition

- Proprietary Verilog configuration not used or supported

- All variants of a particular core (even with identical parameterization and functionality) compiled into the same library for entire project

- Example: all variants of Intel® Arria® 10 PCIe\* core compiled into altera\_pcie\_a10\_hip\_151 library

- Simulation and synthesis file sets instantiate entities identically

- Generated IP file directory structure now matches compilation library

Programmable Solutions Group

## Conclusione:

Penso sia meglio partire da un progetto di esempio in Quartus Prime Pro edition ed integrare i moduli specifici di BES-III dedicati mano a mano....

## How Do I Migrate?

- Update your project assignments (.qsf), timing constraints (.sdc), and Tcl scripts

- Regenerate your IP

- Adjust your RTL for the new Intel® Quartus® Prime Pro synthesis engine

- Discussed in free online training "Using the synthesis engine in the Quartus Prime Software"

- http://wl.altera.com/education/training/courses/OSYNQPRO