#### Outlook

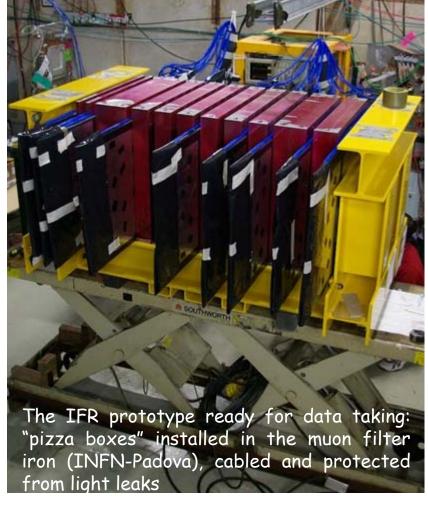

Beam test at Fermilab of the IFR prototype electronics and DAQ system

#### SuperB IFR prototype:

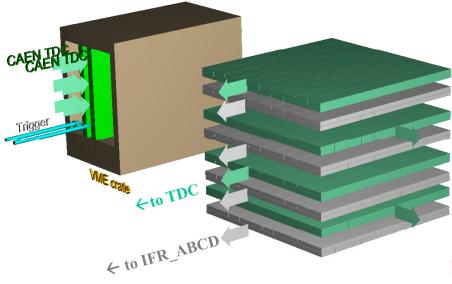

• 5 layers of x-y scintillators, 1 cm thick, read in binary mode

4 layers of scintillators 2 cm thick, read in timing mode (3 out of 4 also readout in binary mode)

#### SuperB-IFR prototype readout electronics:

- "IFR\_ABCD": sensor Amplification, Bias-conditioning, Comparators, Data processing: it samples the level of the comparators outputs @ >= 80MHz and stores it, pending the trigger request

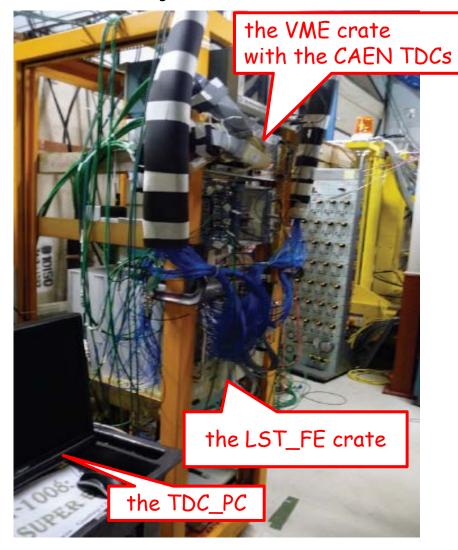

- "CAEN\_TDC": a multi-hit TDC design based on CERN HP-TDC; hosted in a VME crate and read out via a VME-PCI bridge to the DAQ PC

- "IFR\_FE\_BiRO": collects data from IFR\_ABCD cards upon trigger request and sends it to DAQ PC (via GbE)

- "IFR\_TLU": a module (Trigger Logic Unit) to generate a fixed latency trigger based on primitives from the IFR prototype itself or from external sources

IFR\_FE\_BiRO + IFR\_TLU are actually a single module

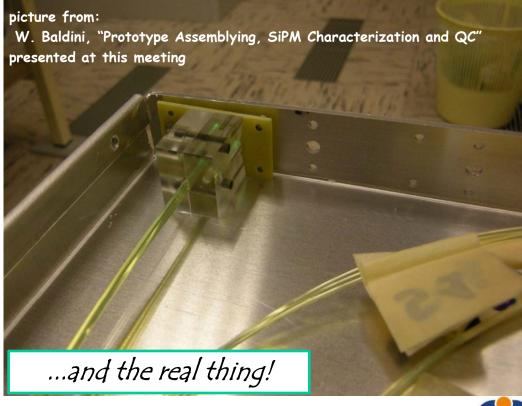

...and the real thing!

pictures from G. Cibinetto, "Some note on the beam test" presented at this meeting

### the concept....

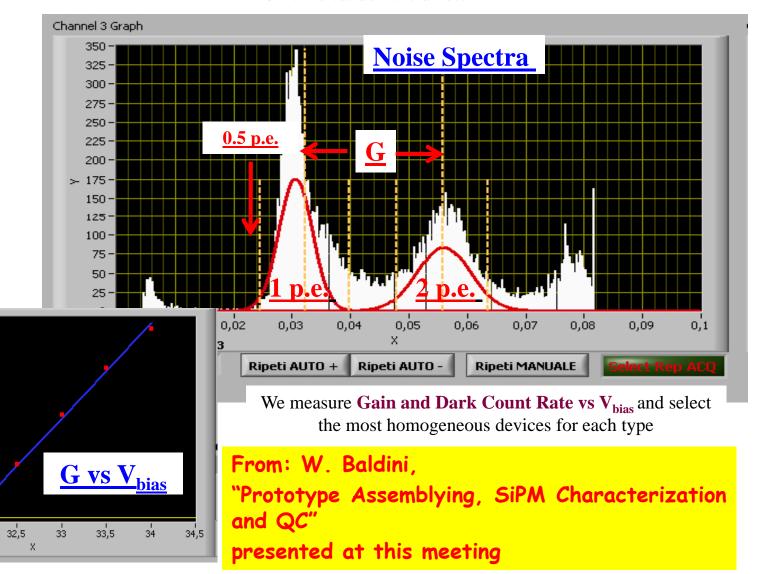

## SuperB IFR electronics: Beam test of the IFR prototype electronics and DAQ system SiPM characterization

$0,026 \cdot$

0,024 -

0,02 -

0,018-> 0,016-

0,014 -

0,012 -

0,01 -

0,008 -

0,006 -

32

31,5

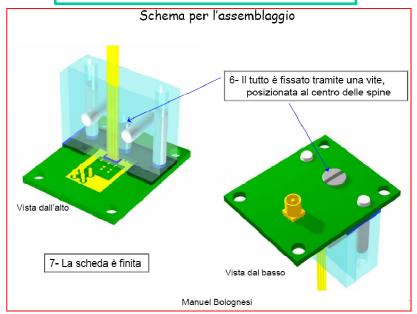

SuperB IFR electronics: Beam test of the IFR prototype electronics and DAQ system FR ABCD dimensions: VME 6U x 220mm 2 x 32 output needed for Programmable timing mode readout only bias voltage 32 x32 x **-**□ x KEL connector 32 x 64 x comparator ampli w/ programmable threshold 4  $\bigcirc$ w/ fixed pulse width w/ diff ECL outputs CONNECTOR TO THE "LST\_FE" CRATE BACKPLANE Bias Threshold DAC DAC inside CycloneIII FPGA based the A.C.R. 2009-10-06 daughter card prototype Outline of the "IFR ABCD" card "pizza box" (Amplifier, Bias, Comparator, Data Processing)

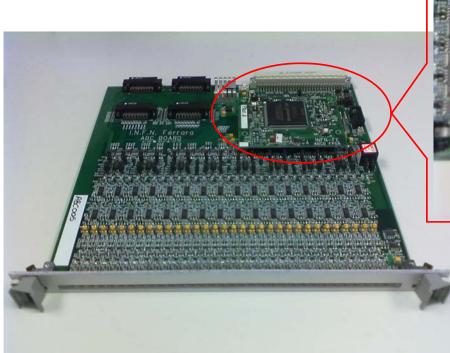

"IFR ABCD" card features:

• ampli: two stage w/discrete components:

BGA2748 + BGA2716

discri: ADCMP563BRQ (ECL out, dual)

For the readout in timing mode of the SuperB IFR prototype it is foreseen to use two comparators at different thresholds for each sensor

signal connector compatible with BaBar IFR signal cables (re-usable): KEL 8831E-034-170LD

- DAC: LTC2625CGN#PBF (I<sup>2</sup>C, 12bit, octal)

- FPGA: Cyclone III ALTERA EP3C25Q240C8

TOTAL "IFR ABCD" cards produced: 12

To enable the reading of a 9th prototype layer

IFR ABCD card: MMIC ampli design & test, schematics, and layout pre-placement by R. Malaguti, INFN-Ferrara

XV SuperB Meeting – Caltech

Dec 16 2010

A.Cotta Ramusino, INFN Ferrara

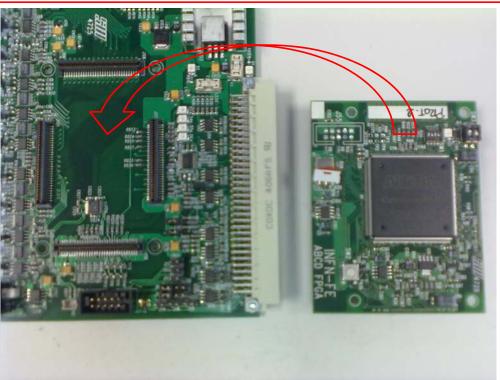

Detail of the digital "IFR\_ABCD" daughter card

SuperB IFR electronics: Beam test of the IFR prototype electronics and DAQ system IFR\_FE\_BIRQ "IFR FE\_BiRO\_TLU\_carrier" FE crate backplane to the connectors Signal level translators DIN LST TRIGGER **PORT** card add-on Flat cable Flat cable A.C.R. 2010-03-17 HSMC Port B HSMC breakout HSMC breakout adapter HSMC Port A 125 MHz Power USB 2.0 RJ-45 Measure Jack Display 10/100/1000 Device (x32) Ethernet 8MB SRAM 1.8V CMOS Graphics LCD Cyclone III EP3C120F780 64MB Flash SMA Output SMA Input (x16) LP Filter and 256MB DDR Audio Amp Dual Channe  $\odot$ PC 50 MHz Speaker Header Quad 7-Seg/ User LEDs Cyclone III Development Board Block Diagram Outline of the "IFR FE BIRO TLU" module

"IFR FE BiRO TLU" module features:

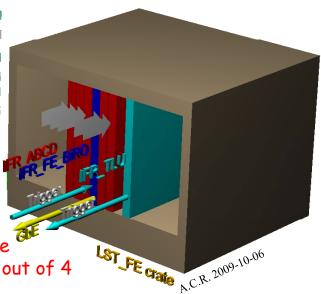

The functions of the IFR FE BiRO and of the IFR\_FE\_TLU cards are combined into a single system made of

- a carrier card which fits in the "LST\_FE" crate (6U  $\times$  220mm depth)

- an add-on card: it's simply the ALTERA Zyclone III development kit (DK-DEV-3C120N) equipped with breakout adapters for the kit's HSMC connectors

The carrier card hosts level adaptors and application specific I/O ports which allow the **add-on** card to:

- ·receive power

- ·receive the "fast OR" signals from the "ABCD" cards to generate triggers from

- \*generate and distribute triggers (also to the TDC system)

- generate and distribute clock and reset signals (also to the TDC system)

- ·poll data from the "ABCD" cards

- ·configure the programmable resources on the "ABCD" cards

- ·connect to the host PC running the DAQ software via ethernet (tcp/ip)

Total "IFR\_FE\_BiRO\_TLU" needed for the prototype readout: 1

IFR\_FE\_BIRC

Trigger

GBE

the "IFR\_FE\_BiRO\_TLU" module

"IFR\_FE\_BiRO\_TLU" module features: (continues)

The FPGA on board the **add-on** card is connected to the RUN CONTROL/DAQ PC of the prototype test setup via an Ethernet port.

The FPGA features a NIOS-II microcontroller which implements the full TCP/IP stack.

The NIOS-II receives commands (i.e. START, STOP, INIT) from the RUN CONTROL/DAQ PC on a TCP server socket and sends data to a TCP server socket on the PC. Data is collected through the LST\_FE backplane from the "ABCD" cards upon a trigger request. The data collection section of the FPGA is coded in VHDL.

The FPGA of the add-on card generates the timing (clock and reset) for all the digitizers and handles the trigger distribution as well.

The FPGA of the add-on card generates the timing (clock and reset) for all the digitizers and handles the trigger distribution as well

les/cycloneIII\_3c120\_niosII\_standarc

V432 M-RAM,M144K: 0/0

SuperB IFR electronics: update on

events

Record from the SuperB\_data.txt where the DATA COLLECTOR task stores the

Altera Nios II EDS 10.0 [qcc4]

pkt: 122070, len: 152, P12366F2 80F0158F

85EF5DØF

PELSOP

2FØ158F

83FØ158F

ยังเยเรยเ

752F109C 7FFF7FFF 0 0 81F14F9F

pkt: 122071, len: 152, F12366F3 90F14E0F "IFR\_FE\_BiRO\_TLU" module features: (continues)

One "Binary mode" event is the collection of 5 samples, taken 12.5ns apart, of the output of each of the 32 HIGH threshold discriminators, on each of the 8 "ABCD".

The samples from one card are preceded by a board header.

The "ABCD" internal pipeline is dimensioned so that the sample selected by a trigger is most likely the center sample in the group of 5.

ו תח תח חח חר

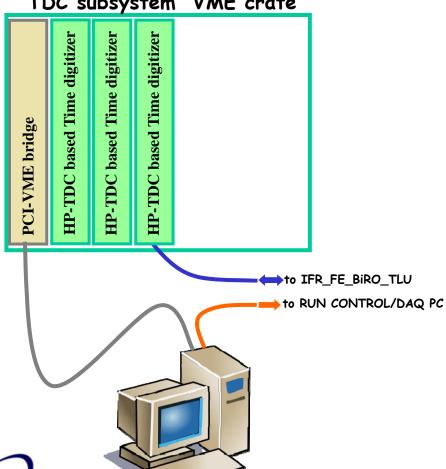

#### "TDC subsystem" VME crate

#### "TDC subsystem" features:

The TDC subsystem uses 3 commercial TDC modules based on CERN's HP-TDC to digitize the time of arrival of the pulses from the "ABCD" boards and from the detectors used in the beam test.

The "IFR\_FE\_BIRO\_TLU" provides the 40MHz reference clock to all the TDCs and receives the "Event Ready" ECL output signal from the last TDC in the readout chain.

The "Event Ready" signal is released by the TDC module when the event selected by the trigger is read from its output FIFO.

Being the TDC readout slower than the BiRO readout, the detection of the falling edge of the "Event Ready" allows the "IFR\_FE\_BIRO\_TLU" to release the IFR\_BUSY signal delivered to the beam test TRIGGER LOGIC

The TDC subsystem VME crate is controlled and read out by the "TDC-PC" via a PCI-VME bridge.

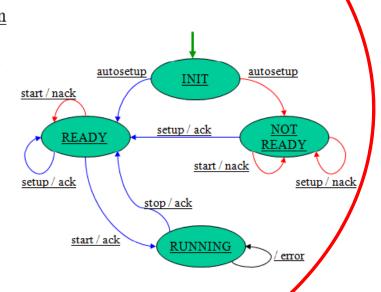

#### Behavior of the TDC PC

The behavior of the data acquisition program is illustrated in the FSM bubble diagram. Blue lines mean the operation requested succeeds, otherwise a red line is used.

For each command received, an ack/nack message is sent.

Running errors are signaled to the OCL via an error message and the running continue.

INIT is the initial state: in this state a TDC setup is done and then the program waits for connection from the OCL.

XIV SuperB Meeting - LNF

Sept-28-2010

Nicola Dalpasso, Universita' Ferrara

## SuperB IFR electronics: Beam test of the IFR prototype electronics and DAQ system Beam test "On Line" software features:

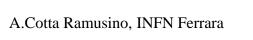

The diagram below, prepared by the main developer of the "On Line" engine, computer scientist Matteo Manzali, temporarily with INFN-Ferrara, shows how the <a href="IFR\_FE\_BiRO\_TLU">IFR\_FE\_BiRO\_TLU</a> and the TDC subsystem interact with the "On Line" system, which includes the DAQ, the ODC and the on-line monitoring modules.

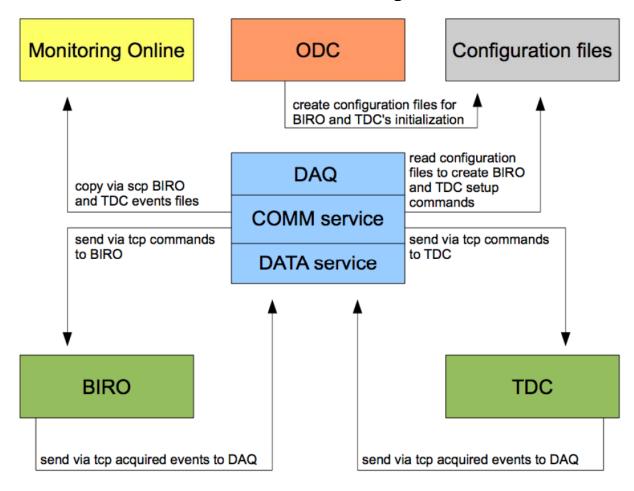

#### Beam test "On Line" software features:

The QT based, graphical user interface of the "On Line" software engine

courtesy of M. Manzali, Dec. 2010

#### Beam test "On Line" software features:

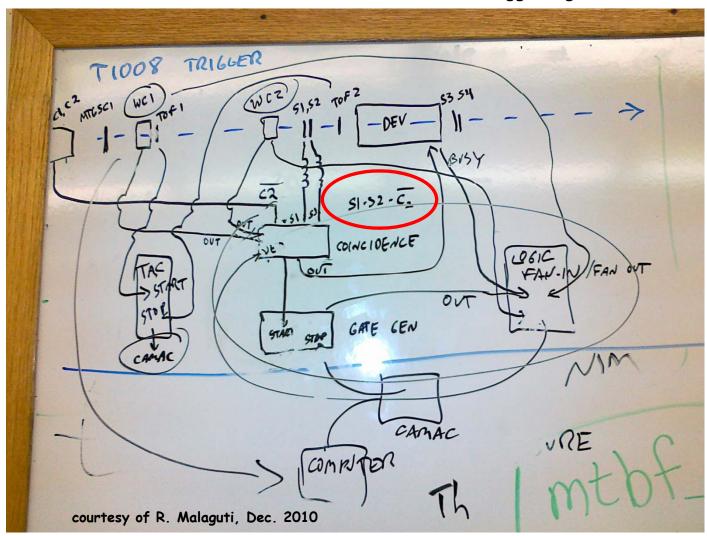

The beam test trigger logic:

#### Legenda:

C1, C2: signals from the differential Cherenkov detector.

C2 was used as an electron veto.

S1 through S4: trigger scintillators

TOF1, TOF2: time of flight detector

WC1, WC2: wire chambers

Circled in the picture is the basic trigger condition:

S1 & S2 & /C2

# SuperB IFR electronics: Beam test of the IFR prototype electronics and DAQ system Preliminary beam test results

Reference talk:

# FIRST RESULTS FROM BEAM TEST G. Cibinetto, E. Feltresi, N. Gagliardi, M. Munerato

presented at this meeting by Mauro Munerato, University of Ferrara

# FIRST RESULTS FROM BEAM TEST

G. Cibinetto, E. Feltresi, N. Gagliardi, <u>M. M</u>

## SuperB IFR electronics: Beam test of the IFR prototype electronics and DAQ system Preliminary beam test results

Reference talk:

# FIRST RESULTS FROM BEAM TEST G. Cibinetto, E. Feltresi, N. Gagliardi, M. Munerato

presented at this meeting by Mauro Munerato, University of Ferrara

FIRST RESULTS FROM

BEAM TEST

G. Cibinetto, E. Feltresi, N. Gagliardi, M. M

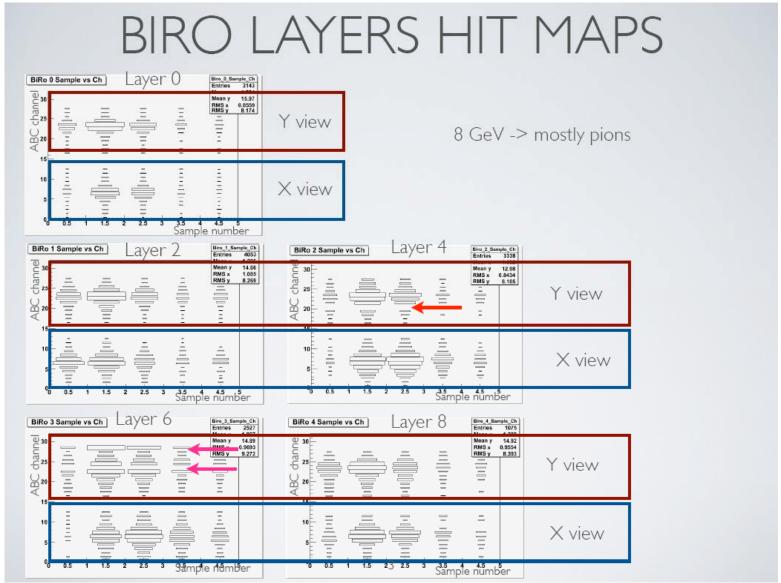

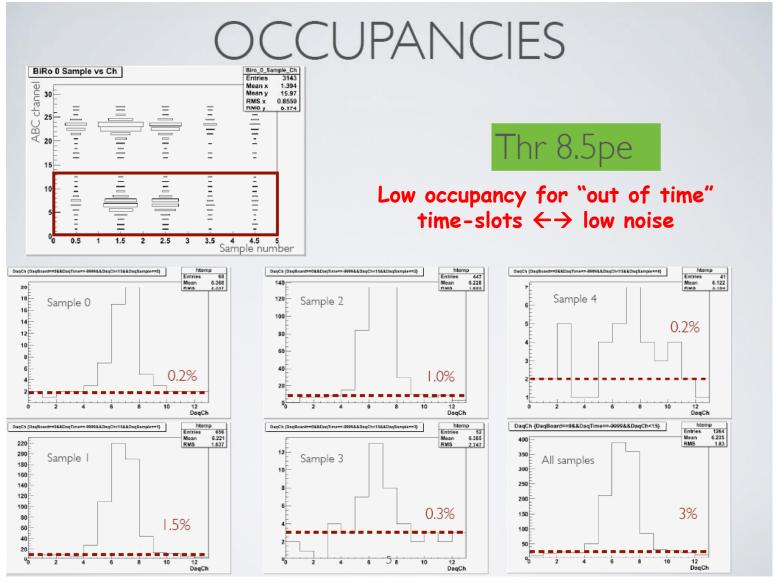

#### A reminder:

Layer 0 = the first one hit by beam particles

Layer 0, 2, 4, 6, 8 are equipped with double layered X-Y planes, each layer 1cm thick. Each bar in these layers is read only at one side.

These planes are only read out in "binary" mode

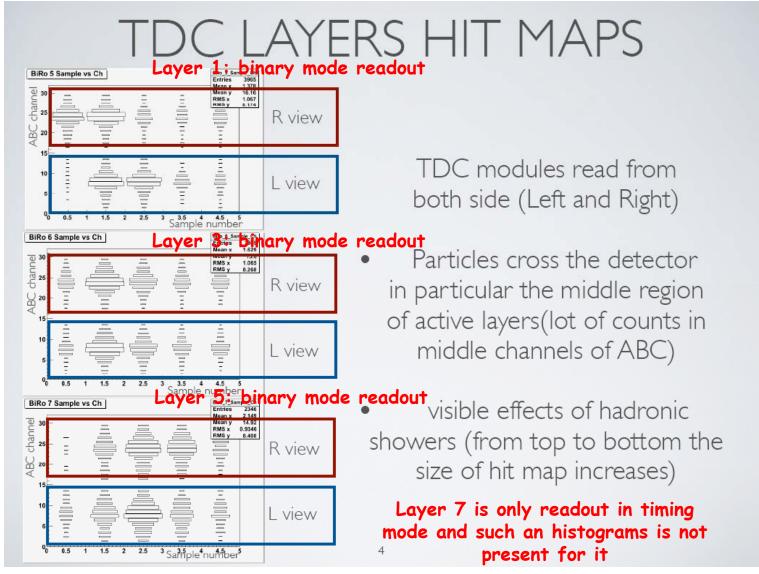

Layer 1,3, 5, 7 are equipped with single layer planes, 2 cm thick. For these layers all the bars are read from both sides

These planes are read out in "timing" mode and 3 out of 4 are also read out in "binary" mode

SuperB IFR electronics: Beam test of the IFR prototype electronics and DAQ system

Preliminary beam test results

# SuperB IFR electronics: Beam test of the IFR prototype electronics and DAQ system Preliminary beam test results

Dec 16 2010

SuperB IFR electronics: Beam test of the IFR prototype electronics and DAQ system

Preliminary beam test results

#### Preliminary beam test results

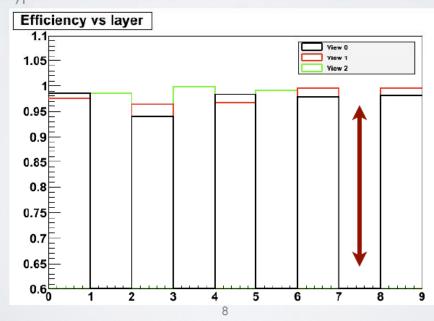

## **EFFICIENCY**

Efficiencies can be calculated using muon events, pions events or mixed e Fachtbar in these layers is read only results shouldn't change much.

Layer 0, 2, 4, 6, 8 are equipped with double layered X-Y planes, each layer 1cm thick.

at one side.

These planes are only read out in

To calculate efficiency we require that the particle hit both the scintillators binary mode the prototype.

Layer 1,3, 5, 7 are equipped with single layer planes, 2 cm thick. For these layers all the bars are read from both sides

These planes are read out in "timing" mode Layer 7 is only read out in "timing" mode and do not appear in this plot.

Efficiency is higher for thicker planes, as expected.