# CALOCUBE T+ROC2 PROGRAMMER'S GUIDE

## 1. INTRODUCTION

This document contains a description of Calocube T+ROC2 registers and it is intended to be used as programmer guide.

#### 2. HIDRA CHIP SEQUENCE GENERATION.

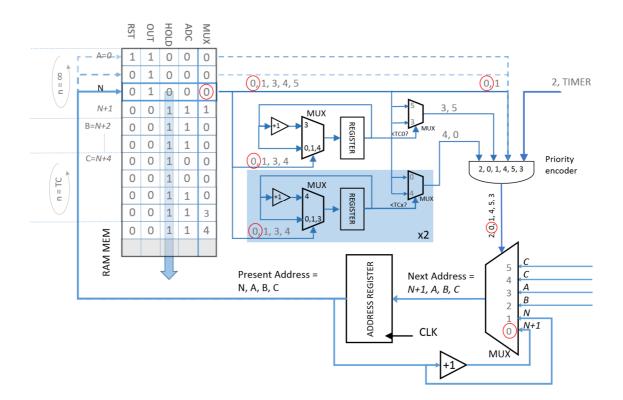

HIDRA ASIC sequence is stored in a RAM memory as shown in figure 1. Each row (position, address, state ...) of this RAM represent the signals needed by the HIDRA ASIC in a given instant of time and each column represent therefore the sequence in time of a particular signal. The time distance of two consecutive rows is 16,  $\hat{6}$  *ns* corresponding to the time distance of two consecutive rising edges of a 60 MHz clock (distributed to the T+ROC2 from the T+ROC1). A given row contain also the control signal of a multiplexer governing the next row in time. By default (MUX = 0 in the figure) the next row will be consecutive to the present one. If the value of MUX control signals is not the default one, the next position will be selected by the multiplexer accordingly. An external signal (indicated by number 2 in the figure 1) has priority over all the rest of control signals and allow exit of programmed loops. Sequence repetition is also allowed by the appropriate control signal (MUX = 3 in the figure) and the content of register 0x17 containing the times (= TC in figure 1) a given sequence is repeated.

Figure 1 T+ROC2 HIDRA ASIC sequence generation block diagram

RAM memory is up to 4096 position depth and 16 bits wide. RAM address is stored in registers 0x04 (LSB) and register 0x05 (MSB), RAM data is stored at register 0x01 (LSB) and 0x02 (MSB). Correspondence between bits registers and signals is as follow:

|               | BIT 0        | RSTA        |

|---------------|--------------|-------------|

| 01            | BIT 1        | RSTB        |

| 0x            | BIT 2        | HOLD        |

| ER            | BIT 3        | HOLDG       |

| ST            | BIT 4        | CAL_EN      |

| REGISTER 0x01 | BIT 5        | OUT_D       |

| RE            | BIT 6        | OUT_RST     |

|               | BIT 7        | OUT_CLK     |

|               | BIT 0        | OUT_EN      |

| 02            | BIT 1        | SCLK        |

| REGISTER 0x02 | BIT 2        | SCS         |

|               | BIT 3        | INC         |

|               | BIT 4        | 12          |

|               | BIT 5        | 13          |

| RE            | BIT 6        | EN_TRG/BUSY |

|               | BIT 7        | RST_COUNT   |

| -             | 1 1 T DOGODI |             |

Table 1. T+ROC2 RAM data registers.

Control signals are INC, 12, 13, RST\_COUNT and the external signal is EXT\_TRG (not shown in the list, as far as said previously cannot be set by the RAM bits). If INC is set a loop counter is incremented as many time as set in register 0x17 (TC) and the next address in RAM where the sequence will continue is stored at registers 0x0E (LSB) and 0x0F (MSB). When the number of repetitions at register 0x09 are reached, then the next address position is stored at register 0x0C (LSB) and 0x0B (MSB). If the external signal EXT\_TRG is set then the next address is stored at registers 0x0A (LSB) and 0x0B (MSB). If RST\_COUNT is set the next address will be 0x0000. If signal 12 (or 13) is set a loop counter is incremented as many time (+1 time) as set in register 0x18 (or 0x19) and the next address in RAM where the sequence will continue is stored at registers 0x10 (or 0x12) (LSB) and 0x11 (or 0x13) (MSB). When the number of repetitions at register 0x18 (or 0x19) are reached the next address position will be the consecutive one.

T+ROC2's registers can be modified by two means. Through a T+ROC1 serial link access (7500 KBUAD, 8 bits data, 1 start bit, 1 stop bit, no parity) and through an RS232 link access (115 KBAUD, 8 bits data, 1 start bit, 1 stop bit, no parity).

Any access to modify the content of a T+ROC2 registers is 2 bytes long. First byte represent the register address and second one the content of that register.

| Address | R/W | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|---------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0x00    | R/W | REG  | Control Register:<br>Bit 0: 0 sequence reset / 1 normal operation.<br>Bit 1: GAIN2SEL.<br>Bit 2: 0 RS232 reset active / 1 RS232 normal operation.<br>Bit 3: 0 external trigger / 1 internal trigger (for test purposes)<br>Bit 4: 0 normal operation / 1 internal trigger counter reset<br>Bit 5: Used for test purposes. Should be 0 during normal operation<br>Bit 6: Used for test purposes. Should be 0 during normal operation<br>Bit 7: 1 configuration / 0 data taking<br>Default register content 0x00. |  |  |

| 0x01    | R/W | REG  | This register stores the <b>LSB data</b> to be write into the RAM.<br>Bit 0: RSTA.<br>Bit 1: RSTB.<br>Bit 2: HOLD.<br>Bit 3: HOLD_G.<br>Bit 4: CAL EN.                                                                                                                                                                                                                                                                                                                                                          |  |  |

T+ROC2 register address are as follow:

|      |     |     | Bit 5: OUT_D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |     |     | Bit 6: OUT_RST.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |     |     | Bit 7: OUT_CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |     |     | Default register content 0x00.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |     |     | This register stores the <b>MSB data</b> to be write into the RAM.<br>Bit 0: OUT_EN.<br>Bit 1: SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x02 | R/W | REG | Bit 2: SCS.<br>Bit 3: INC.<br>Bit 4: 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |     |     | Bit 5: 13.<br>Bit 6: EN_TRG/BUSY.<br>Bit 7: RST_COUNT.<br>Default register content 0x00.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x04 | R/W | REG | This register stores the <b>LSB RAM address</b> where to write and from where to read.<br>Default register content 0x00.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x05 | R/W | REG | This register stores the <b>MSB RAM address</b> where to write and from where to read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0X06 | R/W | REG | Default register content 0x00.It is possible to read the content of most of T+ROC2 registers. Thisregister store the address of the T+ROC2 register to be read.0x00: Control Register.0x01: LSB RAM data0x02: MSB RAM data0x03: 0x000x04: LSB RAM address0x05: MSB RAM address0x06: Read selection register0x07: 0x000x08: 1ump Address LSB destination in case an Ext TRG is detected.0x0C: Jump Address LSB destination in case of TC.0x0D: Jump Address LSB destination in case of INC.0x10: Jump Address LSB destination in case of I2.0x11: Jump Address LSB destination in case of 12.0x12: Jump Address LSB destination in case of 13.0x13: Jump Address LSB destination in case of 13.0x14: Jump Address LSB destination in case of 12.0x15: Jump Address LSB destination in case of 12.0x14: Jump Address LSB destination in case of 12.0x15: Jump Address LSB destination in case of 13.0x16: ST Threshold at HIDRA2_10x17: Number of times a given sequence is repeated (# 13).0x18: ST LOAD0x10: ST Threshold at HIDRA2_20x16: ST Threshold at HIDRA2_40x20: RS232_E |

|               |              |       | 0.00 TDG CIDLLOD                                                                                                                                                            |

|---------------|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |              |       | 0x22: TRG_GEN LSB.                                                                                                                                                          |

|               |              |       | 0x23: TRG_GEN LSB.                                                                                                                                                          |

|               |              |       | 0x24: GAIN HOLD TIMER LSB                                                                                                                                                   |

|               |              |       | 0x25: GAIN HOLD TIMER MSB                                                                                                                                                   |

|               |              |       | 0x26: HOLD TIMER LSB                                                                                                                                                        |

|               |              |       | 0x27: HOLD TIMER MSB                                                                                                                                                        |

|               |              |       | 0x2B: Scaler selector. Default register content 0x00.                                                                                                                       |

|               |              |       | 0x2C: Scaler LSB. Default register content 0x00.                                                                                                                            |

|               |              |       | 0x2D: Scaler MSB. Default register content 0x00.                                                                                                                            |

| 0x07          | W            | REG   | Any access to this register followed by any byte content perform a RAM write at RAM address set by registers 0x05 and 0x04 of the data contained in registers 0x01 and 0x02 |

|               |              |       | 0x00:                                                                                                                                                                       |

|               |              |       | When an access to this register is followed by byte 0x00, a RAM read is                                                                                                     |

|               |              |       | execute from the address set by registers 0x05 and 0x04. Depending of                                                                                                       |

| 0x08          | w            | REG   | the content of register 0x06, LSB (if 0x01) or MSB (if 0x02) of RAM                                                                                                         |

| 0x08          | vv           | KEU   | data is read.                                                                                                                                                               |

|               |              |       | 0x01:                                                                                                                                                                       |

|               |              |       | When an access to this register is followed by byte 0x01, a register read is                                                                                                |

|               |              |       | performed depending of the content of register 0x06.                                                                                                                        |

| 01/00         | DAV          | DEC   | Number of times a given sequence is repeat.                                                                                                                                 |

| 0X09          | R/W          | REG   | Default register content 0x3F.                                                                                                                                              |

| 0.01          | DAU          | DEC   | If an external trigger is detected jump <b>destination address LSB.</b>                                                                                                     |

| 0x0A          | R/W          | REG   | Default register content 0xB0.                                                                                                                                              |

|               |              |       | If an external trigger is detected jump <b>destination address MSB</b> .                                                                                                    |

| 0x0B          | R/W          | REG   | Default register content 0x04.                                                                                                                                              |

|               |              |       | If control bit INC is set and has been detected as many times as set in                                                                                                     |

| 0x0C          | R/W          | REG   | register 0x09, jump <b>destination address LSB.</b>                                                                                                                         |

| UNUC          | IV W         | KLU   | Default register content 0x00.                                                                                                                                              |

|               |              |       | If control bit INC is set and has been detected as many times as set in                                                                                                     |

| 00D           | DAV          | DEC   |                                                                                                                                                                             |

| 0x0D          | R/W          | REG   | register 0x09, jump <b>destination address MSB</b> .                                                                                                                        |

|               |              |       | Default register content 0x00.                                                                                                                                              |

|               | DAV          | DEC   | If control bit INC is set and has not been detected the number of times set                                                                                                 |

| 0x0E          | R/W          | REG   | in register 0x09, jump <b>destination address LSB</b> .                                                                                                                     |

|               |              |       | Default register content 0xC0.                                                                                                                                              |

| 01101         | <b>D</b> 111 |       | If control bit INC is set and has not been detected the number of times set                                                                                                 |

| 0X0F          | R/W          | REG   | in register 0x09, jump destination address MSB.                                                                                                                             |

|               |              |       | Default register content 0x07.                                                                                                                                              |

| 0x10          | R/W          | REG   | If control bit 12 is set jump destination address LSB.                                                                                                                      |

| 0.110         |              | 1.2.0 | Default register content 0x00.                                                                                                                                              |

| 0x11          | R/W          | REG   | If control bit 12 is set jump destination address MSB.                                                                                                                      |

| 0711          | 17,11        | NLU   | Default register content 0x00.                                                                                                                                              |

| $0 \times 12$ | R/W          | REG   | If control bit 13 is set jump destination address LSB.                                                                                                                      |

| 0x12          | IX/ W        | KEU   | Default register content 0x00.                                                                                                                                              |

| 0.12          | DAV          | DEC   | If control bit 13 is set jump destination address MSB.                                                                                                                      |

| 0x13          | R/W          | REG   | Default register content 0x00.                                                                                                                                              |

| 0.14          | DAU          | DEC   | If control bit 12 and control bit 13 are set jump <b>destination address LSB</b> .                                                                                          |

| 0x14          | R/W          | REG   | Default register content 0x00.                                                                                                                                              |

|               |              |       | If control bit 12 and control bit 13 are set jump <b>destination address</b>                                                                                                |

| 0x15          | R/W          | REG   | MSB.                                                                                                                                                                        |

| 0.110         |              |       | Default register content 0x00.                                                                                                                                              |

|               | 1            |       | Number of times a given sequence is repeat. Controlled by signal INC                                                                                                        |

| 0x17          | R/W          | REG   | Default register content 0x3F.                                                                                                                                              |

|               |              |       | Number of times a given sequence is repeat. Controlled by signal 12                                                                                                         |

| 0X18          | R/W          | REG   |                                                                                                                                                                             |

|               |              |       | Default register content 0x3F.                                                                                                                                              |

| 0X19          | R/W          | REG   | Number of times a given sequence is repeat. Controlled by signal13                                                                                                          |

|              |         |     | Default register content 0x3F.                                        |

|--------------|---------|-----|-----------------------------------------------------------------------|

|              |         |     | CAL MASK LOAD:                                                        |

|              |         |     | Bit 0: CAL CLK.                                                       |

|              |         |     |                                                                       |

|              |         |     | Bit 1: CAL RST. 0 reset / 1 normal operation.<br>Bit 2: CAL D         |

|              |         |     |                                                                       |

| 0x1A         | W       | REG | Bit 3: CAL EN (0)                                                     |

|              |         |     | Bit 4: CAL EN (1)                                                     |

|              |         |     | Bit 5: CAL EN (2)                                                     |

|              |         |     | Bit 6: CAL EN (3)                                                     |

|              |         |     | Bit 7: Not used.                                                      |

|              |         |     | Default register content 0x00.                                        |

|              |         |     | ST MASK LOAD:                                                         |

|              |         |     | Bit 0: ST CLK                                                         |

|              |         |     | Bit 1: ST RST 0 reset / 1 normal operation.                           |

|              |         |     | Bit 2: ST EN                                                          |

| 0x1B         | W       | REG | Bit 3: ST D(0)                                                        |

| UXID         | ••      | KLU | Bit 4: ST D(1)                                                        |

|              |         |     | Bit 5: ST D(2)                                                        |

|              |         |     | Bit 6: ST D(3)                                                        |

|              |         |     | Bit 7: Not used.                                                      |

|              |         |     | Default register content 0x00.                                        |

| 0x1C         | R/W     | REG | ST Threshold at HIDRA2_1 the mapping of the bits with ASIC <b>TBD</b> |

| UXIC         | K/ W    | KEG | Default register content 0x55.                                        |

| 01D          | R/W     | DEC | ST Threshold at HIDRA2_2 the mapping of the bits with ASIC <b>TBD</b> |

| 0x1D         | K/W     | REG | Default register content 0x55.                                        |

| 01E          | R/W     |     | ST Threshold at HIDRA2_3 the mapping of the bits with ASIC <b>TBD</b> |

| 0x1E         | K/W     |     | Default register content 0x55.                                        |

| 0-15         | R/W     |     | ST Threshold at HIDRA2_4 the mapping of the bits with ASIC <b>TBD</b> |

| 0x1F         | K/W     |     | Default register content 0x55.                                        |

| 0220         | R/W*    | REG | RS232_Enable_TX only accessible through an RS232 access.              |

| 0X20         | K/ W    | KEG | Default register content 0xFF.                                        |

|              |         |     | USB_RS232_Enable_TX only accessible through T+ROC1 configuration      |

| 0x21         | $R/W^*$ | REG | access.                                                               |

|              |         |     | Default register content 0x00.                                        |

|              |         |     | TRG_GEN LSB. Used to set the frequency of an internal random trigger  |

|              |         |     | generator. This generator will produce a trigger pulse every          |

| 0X22         | R/W     | REG | 200ns*(256*MSB + LSB)* RND_GEN. Where RND_GEN is a number             |

|              |         |     | randomly generated between 1 and 256 (Used for test purposes).        |

|              |         |     | Default register content 0xFF.                                        |

|              |         |     | TRG_GEN MSB. Used to set the frequency of an internal random trigger  |

|              |         |     | generator. This generator will produce a trigger pulse every          |

| 0x23         | R/W     | REG | 200ns*(256*MSB + LSB)* RND_GEN. Where RND_GEN is a number             |

|              |         |     | randomly generated between 1 and 256 (Used for test purposes).        |

|              |         |     | Default register content 0xFF.                                        |

| 0x24         | R/W     | REG | GAIN HOLD TIMER LSB.                                                  |

| 0x24         | R/W     | REG | GAIN HOLD TIMER MSB.                                                  |

| 0x25<br>0x26 | R/W     | REG | HOLD TIMER LSB.                                                       |

| 0x20<br>0x27 | R/W     | REG | HOLD TIMER MSB.                                                       |

| UA27         | 11/ 11  |     | Scaler selection (0x00-0x7F)                                          |

| 0x2B         | R/W     | REG | Default register content 0x00.                                        |

|              |         |     | Selected scaler LSB.                                                  |

| 0x2C         | R       | REG | Default register content 0x00.                                        |

|              |         |     | Selected scaler MSB.                                                  |

| 0x2D         | R       | REG | Default register content 0x00.                                        |

|              | 1       | I   | Table 2. T. BOC2 registers                                            |

Table 2. T+ROC2 registers

\* All the register are accessible through a T+ROC1 configuration access or a RS232 link (115000 BAUD, 8 bits data, 1 bit stop, no parity, no flow control) access but registers 0x20 and 0x21. Register 0x20 can only be write through a RS232 access and register 0x21 can only be write through a T+ROC1 configuration access. Both of them however can be read either through a T+ROC1 configuration access. Content of registers 0x20 and 0x21 should to be equal in order to get response from that particular T+ROC2 through the RS232 link.

#### **Examples**

1- Example of how to write (0x02 = MSB\_Data, 0x01 = LSB\_Data) at position (0x05 = MSB\_Add, 0x04 = LSB\_Add) in the RAM memory:

FT\_HANDLE ftHandle; FT\_STATUS ftStatus; DWORD BytesWritten; char TxBuffer[256]; // Contains data to write to device

TxBuffer[0] = 0x00; TxBuffer[1] = 0x01; // is a write at T+ROC1 configuration T+ROC2 register. TxBuffer[2] = 0x0A; TxBuffer[3] = 0x00; // register at T+ROC1 # of Byte to be written to T+ROC1 TxBuffer[4] = 0x05; TxBuffer[5] = 0xMSB\_Add; // MSB of the RAM mem address to be written TxBuffer[6] = 0x04; TxBuffer[7] = 0xLSB\_Add; // LSB of the RAM mem address to be written TxBuffer[8] = 0x02; TxBuffer[9] = 0xMSB\_Data; // MSB of the data to be written TxBuffer[10] = 0x01; TxBuffer[11] = 0xLSB\_Data; // LSB of the data to be written TxBuffer[12] = 0x07; TxBuffer[13] = 0x00;

// The content of registers 0x02,0x01 are written in the RAM address at registers 0x05,0x04. // We choose to load the MSB registers before the LSB but the order can be any the write do // not take place until the 0x07, 0x00 is executed at T+ROC2.

ftStatus = FT\_Open(0, &ftHandle);

ftStatus = FT\_Write(ftHandle, TxBuffer, sizeof(TxBuffer), &BytesWritten);

```

if (ftStatus == FT_OK) {

// FT_Write OK

}

else {

// FT_Write Failed

}

FT_Close(ftHandle);

```

// sizeof(TxBuffer) = 0x0E

Comments: No enable of the configuration links, has been made as far as by default all the configuration links are enabled at T+ROC1.

2- Example of how to read from position (0xMSB\_Add ,0xLSB\_Add) in the RAM memory:

FT\_HANDLE ftHandle; FT\_STATUS ftStatus; DWORD EventDWord; DWORD TxBytes; DWORD RxBytes; DWORD BytesReceived; DWORD BytesWritten; char TxBuffer[256]; char RxBuffer[256];

```

TxBuffer[0] = 0x00; // register at T+ROC1

TxBuffer[1] = 0x01; // register at T+ROC1

TxBuffer[2] = 0x0C; // register at T+ROC1 is a write of

TxBuffer[3] = 0x00; // register at T+ROC1 # of Bytes to write to T+ROC1

TxBuffer[4] = 0x05;

TxBuffer[5] = 0xMSB_Add; // most signifiant byte of the RAM address to write

TxBuffer[6] = 0x04;

TxBuffer[7] = 0xLSB Add; // Less signifiant byte of the RAM address to write

TxBuffer[8] = 0x06;

TxBuffer[9] = 0x01;

TxBuffer[10] = 0x08;

TxBuffer[11] = 0x00;

TxBuffer[12] = 0x06;

TxBuffer[13] = 0x02;

TxBuffer[14] = 0x08;

TxBuffer[15] = 0x00;

ftStatus = FT_Open(0, &ftHandle);

if(ftStatus != FT_OK) { // FT_Open failed

return;

}

ftStatus = FT_Write(ftHandle, TxBuffer, sizeof(TxBuffer), &BytesWritten);

// sizeof(TxBuffer) = 0x10

if (ftStatus == FT OK) {

// FT_Write OK

}

else {

// FT_Write Failed

FT_Close(ftHandle);

return;

}

TxBuffer[0] = 0x00; // register at T+ROC1

TxBuffer[1] = 0xC1; // register at T+ROC1 is a read (0x80) of two bytes through link 0 (0x41)

TxBuffer[2] = 0x02; // register at T+ROC1 is a read of TxBuffer[3] bytes

TxBuffer[3] = 0x00; // register at T+ROC1 # of Byte to be written to T+ROC1

ftStatus = FT_Write(ftHandle, TxBuffer, sizeof(TxBuffer), &BytesWritten);

```

```

// sizeof(TxBuffer) is now = 0x4

```

```

if (ftStatus == FT_OK) {

// FT_Write OK

```

}

else {

// FT\_Write Failed

FT\_Close(ftHandle);

return;

}

ftStatus = FT\_Read(ftHandle,RxBuffer,RxBytes,&BytesReceived); // where RxBytes is in this example is = 0x02

if (ftStatus == FT\_OK) {

// FT\_Read OK

}

else {

// FT\_Read Failed

FT\_Close(ftHandle);

Return;

}

// data stores at RAM address = (MSB\_Add, LSB\_Add)

// are now in RxBuffer[0]= LSB\_Data and RxBuffer[1]= MSB\_Data

FT\_Close(ftHandle);

Comments: No enable of any configuration link has been made in this example, it is assume therefore that has been made previously. To perform a read on the RAM memory is preceded by two writes access.

### 3. LabView CONFIGURATION PROGRAM.

In order to easy the configuration process a LabView program has been developed allowing to load the sequence, the self- trigger mask and calibration mask from a .CSV file.

Selection of a .CSV format for sequence edition and generation allows the use of common tools like EXCEL or OPEN OFFICE. Tree column are then generated, the first one represent the RAM hexadecimal address (to be load on registers 0x04 and 0x05 of T+ROC2), second one represent the status of control signals according to Table 1 of this document and the corresponding columns in the file (to be load on registers 0x01 and 0x02 of T+ROC2) third one, if different of zero, represent the jump destination when a jump condition is reached and the fourth one represent the vaslue of register 0x09, 0x18 and 0x19 depweding on the value of the third column.

y Tecnológicas

Examples of this files can be found under the following link: https://drive.google.com/drive/folders/10x0ShipqAlj7d-CmJNDGhZY3WfP3qGPa?usp=sharing

Program main tab can be seen at figure 3.

|                        |                     |                                                                                  |           | y Tecnológicas                           |                                             |       |

|------------------------|---------------------|----------------------------------------------------------------------------------|-----------|------------------------------------------|---------------------------------------------|-------|

| 3.vi Front Panel       |                     |                                                                                  |           |                                          |                                             |       |

| View Project Operate 1 |                     | ▼ <u>₩</u> ₩                                                                     |           |                                          | Search                                      | ۹ 🤉   |

|                        |                     |                                                                                  |           |                                          |                                             | Tools |

| SEQUENCE CON           | FIGURATIONS         | T MASK CONFIGURATION                                                             | AL MASK ( | CONFIGURATION                            | SET DAQ MASK                                |       |

| TROC2-1 🥥              | % C:\CARLOS\CALOO   | CUBE\VHDL\TESTER_HIDRA_V2\SEQ_CsI.csv                                            |           |                                          | FT_open_Status<br>FT_OK ▽                   |       |

| TROC2-2                | B C:\CARLOS\CALOO   | CUBE\VHDL\TESTER_HIDRA_V2\SEQ_Csl.csv                                            |           | Device Info<br>FT31FFYIA                 | FT_close_Status<br>FT_OK $\bigtriangledown$ |       |

| TROC2-3                | 8 C:\CARLOS\CALOG   | CUBE\VHDL\TESTER_HIDRA_V2\SEQ_CsLcsv                                             |           |                                          |                                             |       |

|                        | B C) CARLOS CALO    | CUBE\VHDL\TESTER_HIDRA_V2\SEQ_CsLcsv                                             | -         | Array 3                                  | ALOCUBE\VHDL\TESTER_HIDRA_V2\SEQ_CsI.csv    |       |

| TROC2-4                | Ju c. (CAREOS(CAEOC |                                                                                  |           |                                          | ALOCUBE\VHDL\TESTER_HIDRA_V2\SEQ_LYSOcs     | v     |

| TROC2-4                |                     | CUBE\VHDL\TESTER_HIDRA_V2\SEQ_LYSO.csv                                           |           | । ध C:\CARLOS\C                          | ALOCOBE\VHDL\TESTER_HIDRA_V2\SEQ_LYSOCS     |       |

|                        | S C:\CARLOS\CALOO   | CUBE\VHDL\TESTER_HIDRA_V2\SEQ_LYSO.cov<br>CUBE\VHDL\TESTER_HIDRA_V2\SEQ_LYSO.cov |           | ।% C:\CARLOS\C<br>%<br>%                 | ALOCOBE\VHUL\TESTER_HIDKA_V2\SEQ_LYSOCS     |       |

| TROC2-5                | % C:\CARLOS\CALOC   |                                                                                  |           | ାଧି C:\CARLOS\C<br>ବ<br>ବ<br>ବ<br>ବ<br>ବ | ALOCUBE(MHOL)TESTEK, HIDRA_VZ(SEQ_LYSUS     |       |

Figure 3. LabView configuration programm main tab.

Up to eight T+ROC2 board can be connected to the same T+ROC1, either for configuration or for data taking. Up to eight T+ROC2 can be selected then lighting the corresponding LED control. On a by T+ROC2 basis the sequence file it is selected.

Similar tab exist for self-trigger and calibration configuration.

| dit View Project Operate To | ools Window Help                          |                      |                                          | HT             |

|-----------------------------|-------------------------------------------|----------------------|------------------------------------------|----------------|

| 수 🕸 🔘 🚺 15pt Applicatio     | ion Font 🔻 🚛 🙃 - 🕮 - 🕸 -                  |                      |                                          | • Search 🔍 🤶 🖽 |

|                             |                                           |                      |                                          |                |

|                             |                                           |                      |                                          | Tools          |

|                             |                                           |                      |                                          |                |

|                             |                                           |                      |                                          |                |

| SEQUENCE CON                | FIGURATION ST MASK CONFIGURA              | TION CAL MASK CONFIG | URATION SET DAQ MASK                     |                |

|                             |                                           | 1                    |                                          | <u>L</u>       |

|                             |                                           |                      |                                          |                |

| TROC2-1 🥥                   | R C:\CARLOS\CALOCUBE\VHDL\TESTER_HIDRA_V2 | ST_MASK.csv          |                                          |                |

|                             |                                           |                      |                                          |                |

| TROC2-2                     | 8                                         |                      |                                          |                |

| TROC2-3                     | 8                                         |                      |                                          |                |

| IROC2-5                     | ) a                                       |                      |                                          |                |

| TROC2-4                     | 8                                         | ) (÷)                | Array 6                                  |                |

|                             |                                           | <u>Ji</u>            | % C:\CARLOS\CALOCUBE\VHDL\TESTER_HIDRA_V | (\ST_MASK.csv  |

| TROC2-5                     | 8                                         |                      | a                                        |                |

|                             |                                           |                      | 4                                        |                |

| TROC2-6                     | 8                                         |                      | 3                                        |                |

| 70000 7                     |                                           |                      | 3                                        |                |

| TROC2-7                     | C:\CARLOS\CALOCUBE\VHDL\TESTER_HIDRA_V2   | \ST_MASK.csv         | 3                                        |                |

| TROC2-8                     |                                           |                      | 3                                        |                |

|                             | 1.                                        | 1                    | P                                        |                |

| Tab Control                 |                                           |                      |                                          |                |

|                             |                                           |                      |                                          |                |

Figure 4. LabView configuration programm ST\_MASK tab.

3.1 Configuration in Linux

The LabVIEW configuration program has been developed using the FTD2XX driver in synchronous FIFO mode. "FT calls" designed for the D2xx driver are running under Linux CENTOS7 or Windows7. The configuration program has been tested under these operating systems. Labview 2017 version has been downloaded directly from the NI webpage. FTDI has two types of drivers for all supported operating systems. These are the virtual COM port driver (VCP) and the D2XX API driver. For the installation of

the D2XX linux driver, it is recommended to download the suitable Linux D2XX driver of x86 – for 32bit IA-32 CPUs from the FTDI D2XX driver webpage. The driver files are contained in a tar gzip file: e.g. gunzip libftd2xx-i386-1.4.8.tar.gz and tar –xvf libftd2xx-i386-1.4.8.tar

Procedure:

1) All driver files need to be copied and symbolic links created using the Linux sudo command for root permissions:

sudo cp /releases/build/lib\* /usr/local/lib

2) Make the following symbolic links and permission modifications in /usr/local/lib: cd /usr/local/lib sudo ln -s libftd2xx.so.x libftd2xx.so sudo chmod 0755 libftd2xx.so.1.4.8

3) The symbolic link is used to select a default driver file. Any program can be linked against a specific version of the library by using a version numbered library file. Make sure the following dependences are correctly installed:

/etc/udev/rules.d/99-libftdi.rules

/usr/lib/libftdi.so.1

/usr/lib/ftdi.so.1.18.0

4) Add user to the user group

Usermod –G 984 nameuser

Adduser –G 5 nameuser less /etc/groups

Add user nameuser dialout tty

5) Plug in the FTDI based device. VCP driver need to

**5)** Plug in the FTDI based device. VCP driver need to be removed for its particular use: *sudo rmmod ftdi sio*.

# References

- Xilinx, "UG380 Spartan-6 FPGA" Configuration User Guide (ver 2.10). DS162 Spartan-6 FPGA Data Sheet: DC and Switching Characteristics (ver 3.1.1). DS160 - Spartan-6 Family Overview (ver 2.0).

- 2. Xilinx," UG470 7 Series FPGAs Configuration User Guide," ver 1.13.1, (August 21th, 2018).

- **3.** Gianluigi Zampa, "HiDRA2: High Dynamic Range Amplifier frontend ASIC," HiDRA2 DATASHEET, (March, 2018).

- 4. FTDI, "FTDI drivers, Document Reference No.: FT 000723 Clearance No.: FTDI 302," (July 6th, 2017).

- 5. Analog Devices, "16-Bit, 500 kSPS PulSAR ADC in MSOP," Datasheet.

- 6. G.Martínez, et al. "TROC1 manual," January, 2019. Firmware version x0C0B.