#### Goals della riunione

## Goals per oggi:

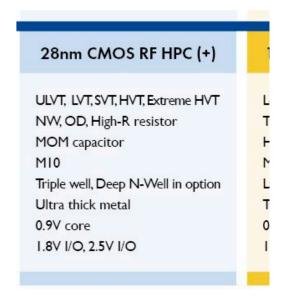

- Accesso alla tecnologia 28 nm TSMC HPC+

- Tool di progettazione

- Logo del progetto

- Report dai WG

- Milestone 1

- Definizione delle specifiche

#### TSMC 28 nm HPC+

- Scelta obbligata per TSMC.

- Esperienza pregressa di alcuni dei progettisti in FALAPHEL

- Occorre mettere a comune le esperienze per alcuni BB

- È possibile sottomettere i chip passando dal CERN.

- Facciamo una programmazione interna

https://europractice-ic.com/mpw-prototyping/asics/tsmc/

# Tool di progettazione

#### ©Contratto Cadence con INFN. Ci permette di

- 1) usare la licenza a scopo non commerciale ai fini a) formativi b) ricerca fondamentale

c) partecipazione a programmi di ricerca finanziati da governi nazionali e EU, d)

partecipazione in programmi di ricerca all'interno finanziati da enti pubblici.

- 2) fabbricare da terzi disegni che creiamo

- ② 3) scambiare i disegni solo con <u>alcuni laboratori internazionali.</u> Eventuali collaboratori aggiuntivi devono esser autorizzati da Cadence a loro unica discrezione.

- A differenza del contratto precedente possiamo scambiare i disegni tra sedi INFN.

- Tuttavia non è permesso scambiare disegni con le Università, che tra l'altro hanno un contratto "educational"

- Stante così le cose una soluzione "semplice" potrebbe esser quella di far progettare tutti (dipendenti e associati) su macchine INFN e poi integrare i disegni

- Punto delicato (in fase di discussione) è l'eventuale rivalsa dell'INFN nei confronti di progettisti che infrangessero la licenza a scopi commerciali.

# Logo

## Due 'logo" sono stati proposti da Philippe

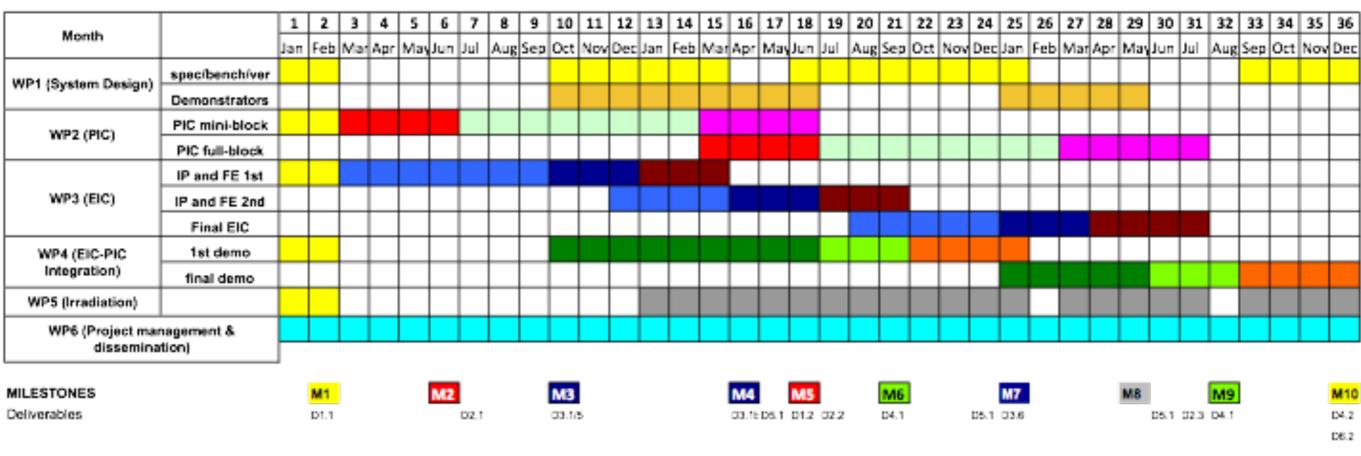

#### Gantt chart

#### Legenda

# Specifications/benchmark/verification PIC design & layout PIC fabrication EIC design & layout EIC fabrication Integration test Integration design EIC-PIC Integration EIC test PIC test Irradiation

#### Milestones

- M1 (Definitions of the specs and KPI) (T0+2)

- M2 (Silicon Photonics PIC design for the submission of the mini-block chip fabrication) (T0+6)

- M3 (1st submission of the High Speed rad-hard block design) (T0+10)

- M4 (2nd submission of the High Speed rad-hard block design) (T0+16)

- M5 (Final Silicon Photonics PIC design for the submission of the full block chip fabrication) (T0+18)

- M6 (First integration EIC+PIC) (T0+21)

- M7 (Final, large area EIC submission) (T0+25)

- M8 (Qualification of rad-hardness of PIC and EIC) (T0+29)

- M9 (Final demonstrator integration) (T0+32)

- M10 (Final demonstrator qualification) (T0+36)

# Assegni

| A<br>d<br>R<br># | T<br>y<br>p<br>e | Un<br>it | Mon<br>ths | Research Topic                                         | Bandito/<br>Partenza | Vincitore |

|------------------|------------------|----------|------------|--------------------------------------------------------|----------------------|-----------|

| 1                | J                | PI       | 30         | PIC design and test. PIC-EIC 2021 integration and test |                      |           |

| 2                | S                | PI       | 24         | Driver design. PIC-EIC integration and test            | 2020/2021            | G. Ciarpi |

| 3                | J                | PI       | 12         | PLL/CDR design and test                                | test 2022            |           |

| 4                | J                | PV       | 30         | DAC design and test                                    | 2020/2021            |           |

| 5                | S                | PV       | 12         | FE design, test and integration in the demonstrator    | n in the             |           |

| 6                | J                | P<br>D   | 12         | Irradiation tests and analysis                         | 2022                 |           |

### WP Structure

Table 3. Work Packages.

| WP | Topic                                         | Leader                                                                   | Unit                                | Areas of work                                                                                 |

|----|-----------------------------------------------|--------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------|

| 1  | System Design                                 | Luigi Gaioni                                                             | INFN Pavia                          | Demonstrator design, system specifications and key performance indicators                     |

| 2  | Silicon<br>Photonics                          | Stefano Faralli                                                          | Scuola Superiore S.<br>Anna of Pisa | PIC blocks, Ring-Resonator<br>Modulator, MachZehnder<br>Modulator, WDM and SDM                |

| 3  | Electronics                                   | Gianluca Traversi<br>(focus FE) and<br>Guido Magazzu<br>(focus IP cores) | INFN Pavia INFN Pisa                | Serdes, Driver, PLL/CDR, DAC,<br>Bandgap, Front-End                                           |

| 4  | EIC-PIC<br>Integration                        | Sergio Saponara                                                          | University of Pisa                  | Packaging and integration,<br>thermal studies, prototyping and<br>fabrication                 |

| 5  | Radiation<br>hardness                         | Serena Mattiazzo                                                         | INFN Padova                         | Tests with X-rays, Heavy Ions, protons, neutrons                                              |

| 6  | Project<br>management<br>and<br>dissemination | Fabrizio Palla                                                           | INFN Pisa                           | Resource management, planning and coordination. Dissemination and exploitation of the results |