# TF7 Electronics and On-Detector Processing

Conveners: Dave Newbold, Francois Vasey Members: Niko Neufeld, Valerio Re, Christophe de la Taille, Marc Weber

- The development of electronics in general and ASICs in particular will continue to play a very important role for all future experiments in HEP.

- These HEP developments will have to follow the microelectronics industry to smaller feature sizes in order to benefit from the increasing transistor density, the intrinsic high speed and the lower power consumption.

- In addition, the need to follow industry to newer technologies is also mandatory as production lines for older technologies are discontinued.

- Infrastructures at the HEP institutes for the design of complex mixed-mode CMOS ASICs have to be built up to match future challenges and emerging design and verification methods need to be explored.

- To process the data generated by the detectors' high speed optical links, chips for data aggregation and filtering as well as FPGAs need to be brought to the level required for future experiments.

- If integrated photonic nodes become available, new avenues of development might open.

- The low operation voltages of present and future chip technologies will make the development of on-chip DC-DC converters and power management blocks essential for future low mass detectors.

- The scope of this task force should also include developments exploring more sophisticated interactions between on-detector and off-detector electronics, keeping in mind and profiting from the rapid evolution of commodity electronics.

The radiation tolerance for the electronics required by future experiments, in particular those at hadron machines, is unique to applications in HEP and needs to be addressed in a common international effort

- Interconnection technologies, post processing and packaging will become essential for future high-density detectors.

- In hybrid pixel detectors for example the high cost of flip-chip bonding is a limiting factor, and alternative methods are already in use in industry and may also be explored by HEP.

- Access to these sophisticated technologies is often restricted to large size projects, and will benefit from a community-wide approach.

- The format and packaging of on-detector electronics will be driven partly by integration, material, and power/cooling concerns, and will thus need to be covered across task forces TF7 and TF8.

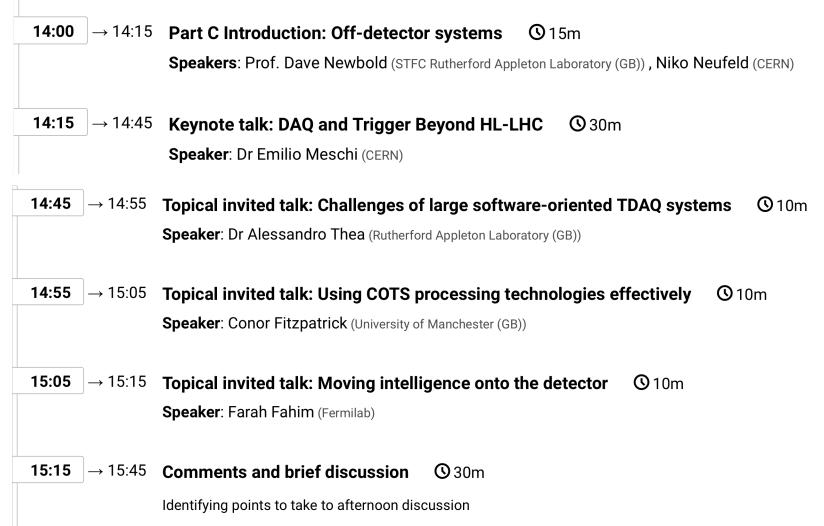

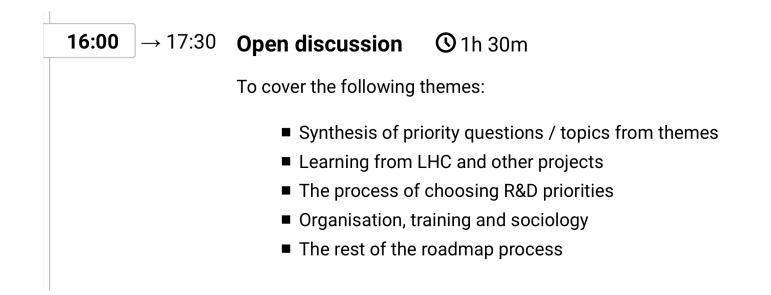

| <b>09:00</b> → 09:15 | Introduction and background ③15m<br>Speakers: Prof. Dave Newbold (STFC Rutherford Appleton Laboratory (GB)), Francois Vasey (CERN)                                           |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>09:15</b> → 09:30 | Part A Introduction: ASICs and front-end electronics 0 15m<br>Covering scope and summary of inputs                                                                           |

|                      | Speakers: Christophe De La Taille (OMEGA (FR)), Valerio Re (Universita and INFN (IT))                                                                                        |

| <b>09:30</b> → 10:00 | Keynote talk: Future trends, challenges and opportunities in ASICs for HEP: a birds-eye view ③ 30m   Speaker: Angelo Rivetti (INFN - National Institute for Nuclear Physics) |

| <b>10:00</b> → 10:10 | Topical invited talk: Moving to leading-edge technology nodes O10m                                                                                                           |

| <b>10:10</b> → 10:20 | Topical invited talk: 3D integration ③ 10m   Speaker: Christophe Wyon (CEA French Alternative Energies and Atomic Energy Com)                                                |

| <b>10:20</b> → 10:30 | Topical invited talk: Perspectives on future development (TBC) ③ 10m   Speaker: Erik Heijne (Czech Technical University in Prague (CZ))                                      |

| <b>10:30</b> → 11:00 | Comments and brief discussion ③ 30m<br>Identifying points to take to afternoon discussion                                                                                    |

| <b>11:15</b> → 11:30 | Part B Introduction: Links, powering and integration ③15m<br>Speakers: Francois Vasey (CERN), Marc Weber (KIT - Karlsruhe Institute of Technology (DE)) |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>11:30</b> → 12:00 | <b>Keynote talk: Front-End Power and Links: Trends and Expected Needs</b> ③ 30m<br><b>Speaker</b> : Philippe Farthouat (CERN)                           |

| <b>12:00</b> → 12:10 | Topical invited talk: Future rad-hard optical links ① 10m<br>Speaker: Jan Troska (CERN)                                                                 |

| <b>12:10</b> → 12:20 | Topical invited talk: Wireless link technologies on the detector③ 10mSpeaker: Richard Brenner (Uppsala University (SE))                                 |

| <b>12:20</b> → 12:30 | Topical invited talk: Powering and data communications challenges at FCChh① 10mSpeaker: Werner Riegler (CERN)                                           |

| <b>12:30</b> → 13:00 | Comments and brief discussion ③ 30m<br>Identifying points to take to afternoon discussion                                                               |

- Are requirements of future experiments reasonably achievable for electronics?

- Design of electronics systems should be an integral part of the design of detectors and experiments

- Next slides: a selection of outcomes from the input session on Future Facilities (Feb.19)

## FCC-hh

#### **Challenges for Read-Out Electronics & Trigger (TF7)**

- Huge amounts of data produced (e.g. O(1000TByte/s) = O(10Pbps) for zero-suppressed tracker)

- Streaming:

- Read-out everything  $\rightarrow$  need fast low power radiation hard optical links

- Alternative: summarize received data by higher-level quantities and only transmit and store those

- Triggered: Read-out interesting events → challenge to achieve a data reduction of factor O(10) (HL-LHC aims for factor 40) with much higher pile-up

- → need efficient triggering intelligent decision as close to the sensor as possible (ML or AI on front-end, programmable ASICs, FPGAs?)

- $\rightarrow$  radiation hard buffering/storage

- $\rightarrow$  High bandwidth, low power, radiation hard data links

- Industry at link speeds of 400Gbps, need to be adapted to radiation hardness, low power, low material and distributed data sources

- Rad. hard link R&D targeting 25Gbps has started at CERN, but will need 50-100Gbps links to fulfil FCC-hh requirements

- Low-power: 10Pbps = 1 million lpGBTs (~500mW)  $\rightarrow$  500kW for the links alone!

- Cooling needs cause large amounts of dead material  $\rightarrow$  minimize cooling needs

- New technologies: CMOS with integrated photonics (Silicon Photonics)

- DOE Instrumentation BRN: "The presently used data link architecture in which front-end ASICs communicate electrically to optical converters does not scale to arbitrary data rates.... New architectures will need to be explored to solve this problem. In terms of ASIC technology, industry predicts that photonics will be integrated with CMOS processes within 5 to 10 years."

## FCC-hh

#### • Wireless read-out systems:

- Potential to reduce material interesting if wireless transmission can fulfil the low-power requirement

- But main material contribution coming from power and cooling needs (and not from optical fibers)

- Analogue to digital conversion will be located at the front-end

- Already the case for all HL-LHC upgrades, e.g. analogue calorimeter trigger Run1 and Run2 → digitization at the front-end for HL-LHC

- Advantages: low noise, standardised and efficient digital transmission

- But needs radiation hard and low-power ADCs and ASICs (300MGy, 10<sup>18</sup>neutrons/cm<sup>2</sup>)

- For comparison: HL-LHC factor 30 less, 65nm ok up to O(3MGy)

- Develop radiation hard power management blocks (DC/DC converters, regulators)

- Develop precision clock and timing circuits (PLL, DLL, Timing Discriminators, Delay Lines, Picosecond TDCs)

- Timing distribution with pico-second synchronization

## Linear high-energy e+e- machines

- Highly integrated electronics crucial for LC detectors, to enable required compactness and hermeticity

- ASICs central for all subsystems ultra-low power consumption a central theme

- Optimised for *power-pulsing* however, suitability of such ASICs for beam tests, pre-installation calibration and cosmics data taking is a challenge.

- Maximal integration requires modern technologies, *small feature size*: costly development, increasing demand on *verification*

- Compact interfaces high-density boards for services and communication between VFE and off-detector electronics

- Large-area multi-layer electronics boards with high mechanical precision, far beyond industry standards in particular for highly granular calorimeters

- DAQ requirements relatively benign ~100 MB of zero-suppressed data per bunch-train, up to ~5 GB/s

- Significantly higher for calibration runs without or with reduced zero suppression

- CMOS technologies are becoming more and more complex, making it impossible to effectively support too many variants

- 65 nm, 28 nm, next?

- Radiation tolerance, cryogenic temperatures

- Design of integrated electronics in CMOS sensors (65 nm, 28 nm imaging processes)

- Will 3D integration become available?

#### INFN

• CHIPIX65 (call gruppo V, P.I. Lino Demaria)

28 nm CMOS ASIC for pixel detectors with high time resolution

• **Timespot** (call gruppo V, P.I. Adriano Lai)

28 nm CMOS ASIC for pixel detectors with high time resolution

• Falaphel (call gruppo V, P.I. Fabrizio Palla)

28 nm CMOS for CMOS ASICs interfacing with silicon photonics devices for high rate data transmission

#### • AIDAINNOVA

WP with network on 28 nm CMOS, 130nm/65nm chips for detectors in the project

## TF7 outlook

- At this point TF7 is open to suggestions from the community ( I solicit inputs from INFN)

- Development of new electronics systems with advanced technologies (nanometer CMOS, 3D integration) requires a community of fully trained designers; in my opinion, it is crucial that INFN supports this community