# Proposta QUANTEP QUANtum Technologies Experimental Platform

Franco Spinella

#### QUANTEP

- In risposta alla Call tematica di Gr V sullo sviluppo di tecnologie quantistiche (valutazione entro settembre)

- Responsabile nazionale Andrea Salamon (Roma 2)

- 8 Sezioni coinvolte: LNL,MI,PG,PV,RM2,SA,TO

- 20 FTE/y circa, budget ~ 1 M€

- Goal: Sviluppo di circuiti integrati fotonici operanti in regime di singolo fotone per algoritmi di quantum computing, integrazione su silicio di rivelatori e sorgenti di singolo fotone e di circuiti per il controllo della polarizzazione

#### Stato dell'arte

- Vari progetti INFN nell' ambito della silicon photonics su Silicon On Insulator (QUICHE, SPE, Phos4Brain, ...) -> applicazioni non QC o non single photon o senza sorgenti/rivelatori integrati.

- Progetti INFN (piu' Univ.) nell'ambito del quantum computing, anche con fotoni singoli, ma basati su banchi ottici

- Proposta vuole integrare le due attività, sviluppando un circuito ottico su substrato di SOI per uso in condizioni di single photon e che permetta di sperimentare con gate quantistici (c-not) e con sorgente e rivelatore integrati.

## Fotonica su SOI (Silicon On Insulator)

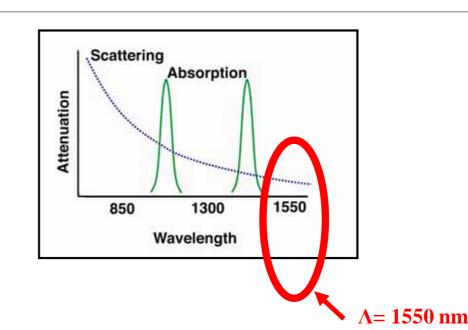

❖Il Silicio e' un ottimo materiale per la trasmissione della luce, alto indice di rifrazione ( > 3.5) e bassa attenuazione (alle giuste lunghezze d'onda)

standard

telcom.

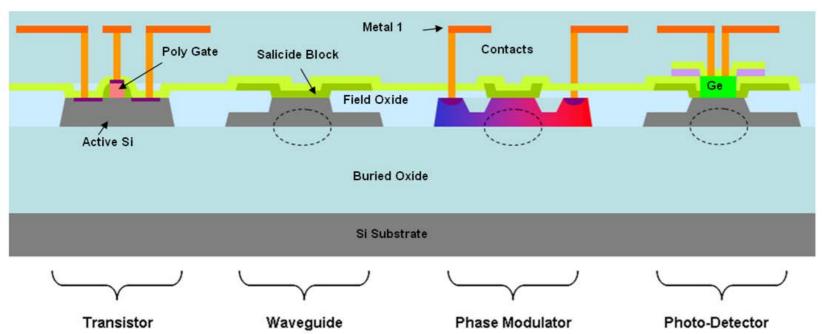

E' possibile integrare vari componenti ottici e/o anche elettrici CMOS compatibili

#### Fotonica su SOI 2

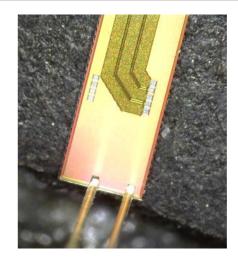

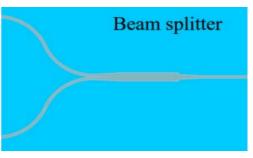

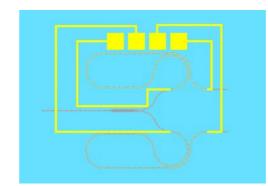

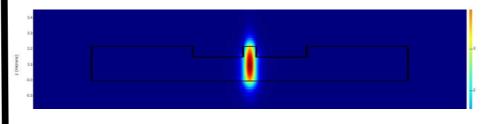

❖IC fotonici realizzati nel precedente progetto SPE con IHP SG25PIC (interferometro Mach-Zender)

- Tools: Cadence + Lumerical

- Cadence non piu' disponibile

- ❖IPKISS + TexEDA + Lumerical

Fibre I/O accoppiate con reticolo di Bragg

Beam splitter simmetrico 50%

Sfasatore termo ottico

Simul. Lumerical

## Quantum Computing con ottica lineare

- [1982] R. P. Feynman suggerisce di costruire un computer basato sulla manipolazione di funzioni d'onda per poter simulare la natura con un calcolatore quantistico

- [1994] P. W. Shor propone un algoritmo di fattorizzazione di numeri interi in numeri primi operante su un computer quantistico più efficiente dell'analogo classico

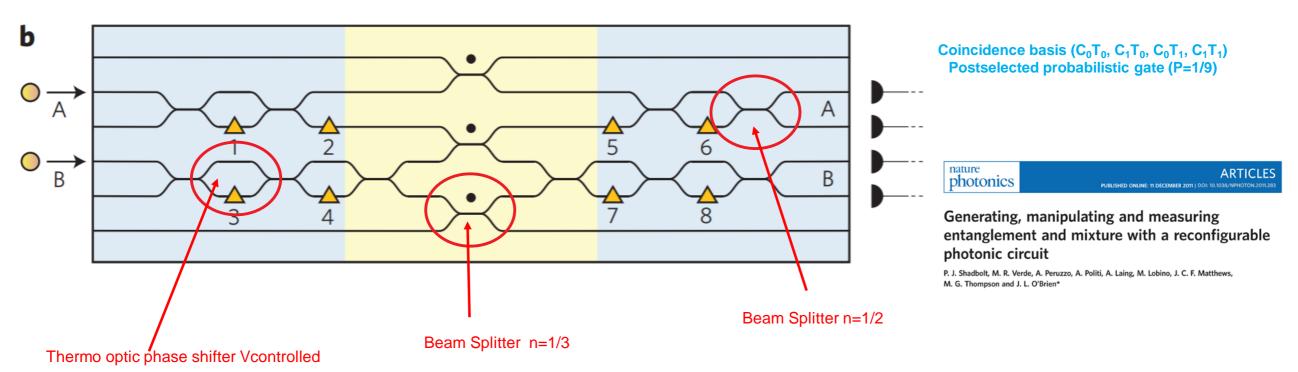

- [2001] Knill, Laflamme e Milburn dimostrano come sia possibile usare l'ottica lineare per l'elaborazione di informazioni quantistiche servendosi di beam splitter, phase shifter, sorgenti e rivelatori di singolo fotone.

- In particolare con questi elementi si puo' costruire un gate CNOT (controlled not) che e' il mattone fondamentale di tutti gli algoritmi quantistici.

## Controlled NOT (CNOT)

❖Gate quantistico fondamentale, opera su 2 QBIT. Inverte il secondo (target) se e solo se il primo e' |1>

| INPU        | ΙΤ          | OUTPUT      |             |  |

|-------------|-------------|-------------|-------------|--|

| Controllo   | Target      | Controllo   | Target      |  |

| $ 0\rangle$ | $ 0\rangle$ | $ 0\rangle$ | $ 0\rangle$ |  |

| $ 0\rangle$ | $ 1\rangle$ | $ 0\rangle$ | $ 1\rangle$ |  |

| 1 angle     | $ 0\rangle$ | 1 angle     | $ 1\rangle$ |  |

| 1 angle     | $ 1\rangle$ | 1 angle     | $ 0\rangle$ |  |

Puo' essere costruito con elementi di ottica lineare:

#### **QUANTEP 1**

- QUANTEP propone di realizzare il CNOT in due versioni:

- IC fotonico, con sorgenti e rivelatori esterni, accoppiati tramite fibra

- IC fotonico completo di sorgenti single photon, polarizzatori e rivelatori single photon integrati su silicio

Il Silicio sara' realizzato da IHP: Innovations for high performance MicroElectronics Istituto di ricerca tedesco specializzato in IC fotonici e RF

### **QUANTEP 2**

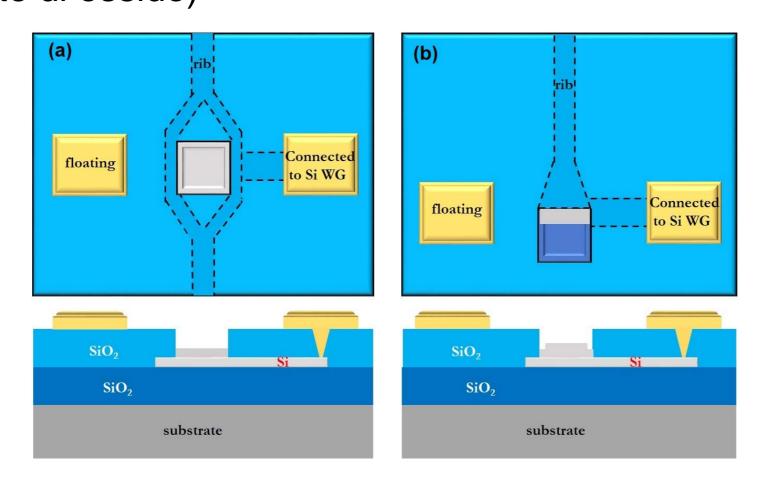

- \* Fase 1: processo IHP SG25PIC ( SOI con processo CMOS a 250 nm)

- ❖ Fase 2: sorgenti e rivelatori si ottengono tramite deposizioni ioniche su silicio (effettuate dagli enti di ricerca partner) Concordate con IHP lavorazioni di post produzione ( es. creazione delle aree scoperte di ossido)

#### WP

- A Pisa vorremmo collaborare al WP3: progetto e simulazione dell'ottica lineare integrata su silicio

- Interesse anche per il WP1: integrazione del sistema e test Qualche test a Pisa, principalmente a RM2

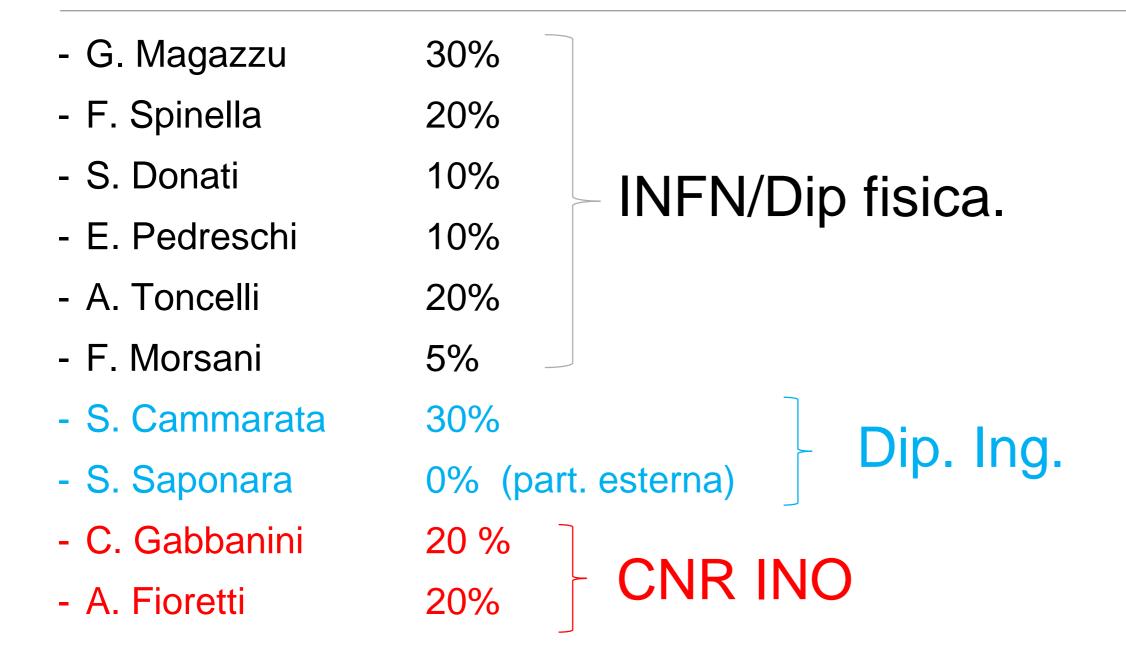

## - Anagrafica

- Previsti fondi per un assegno su Pisa

- Durata call 3 anni

## - Richieste alla Sezione e budget

- Bonding dei prototipi in camera pulita 1w/y tecnico AT

- Laboratorio: la maggior parte dei test si faranno a RM2

A Pisa potremo utilizzare il lab di Mu2e dove e' presente un tavolo ottico

- Simulazioni elettromagnetiche richiedono molta CPU. PC molto potente P9 multicore 0.5 TB RAM di Mu2e ma potremmo valutare richiedere supporto su una farm di Sezione

#### - Budget:

|    | 3 | Human resources (AdR)              | 25    |    |   | SPServices  |

|----|---|------------------------------------|-------|----|---|-------------|

| PI | 3 | CAD license (Lumerical FDTD)       | 5     | 5  |   | SW licenses |

|    | 3 | CAD license (TexEDA IC)            | 2.5   | 4  |   | SW licenses |

|    | 3 | Travels                            | 2     | 2  | 2 | Travels     |

|    | 3 | IHP custom runs NRE costs          | 39    |    |   | Consumables |

|    | 3 | IHP three dopings levels NRE costs | 15    |    |   | Consumables |

|    | 3 | IHP MPW run costs 40 mm2           | 80    |    |   | Consumables |

|    | 3 | PCB and bonding                    |       | 5  | 5 | Consumables |

|    |   | Total PI                           | 168.5 | 16 | 7 |             |