#### Overview

• update on the development of the IFR prototype electronics and DAQ system

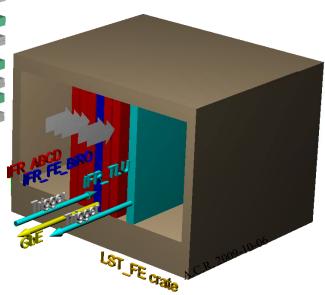

Second ABCD crate added

FE crate

SuperB IFR prototype:

← to IFR\_ABCI 5 layers of x-y scintillators, 1 cm thick, read in binary mode

4 layers of scintillators 2 cm thick, read in timing mode

Trigger

SuperB-IFR prototype readout electronics (baseline):

- "IFR\_ABCD": sensor Amplification, Bias-conditioning, Comparators, Data processing: it samples the level of the comparators outputs @ >= 80MHz and stores it, pending the trigger request

- "CAEN TDC": a multi-hit TDC design based on CERN HP-TDC; hosted in a VME crate and read out via a VME CPU or via a VME-PCI bridge to the DAQ PC

- "IFR FE BiRO": collects data from IFR\_ABCD cards upon trigger request and sends it to DAQ PC (via GbE)

- "IFR\_TLU": a module (Trigger Logic Unit) to generate a fixed latency trigger based on primitives from the IFR prototype itself or from external sources

IFR\_FE\_BiRO + IFR\_TLU are now a single module

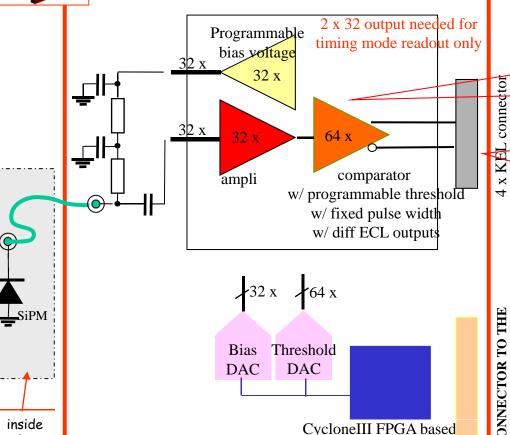

"IFR ABCD" card features:

ampli: two stage w/discrete components:

BGA2748 + BGA2716

discri: ADCMP563BRQ (ECL out, dual)

For the readout in timing mode of the SuperB IFR prototype it is foreseen to use two comparators at different thresholds (2.5 pe and 1.5 pe for instance) for each sensor

signal connector compatible with BaBar IFR signal cables (re-usable): KEL 8831E-034-170LD

- DAC: LTC2625CGN#PBF (I<sup>2</sup>C, 12bit, octal)

- FPGA: Cyclone III ALTERA EP3C25Q240C8

#### "IFR\_ABCD" needed for prototype readout:

1 for each of 4 BiRO planes (readout at only one end of scintillator) +

1 for each of 4 planes read with TDCs (readout at both ends of scintillator)

TOTAL "IFR\_ABCD" cards: 8

TOTAL "IFR ABCD" cards produced: 12

(to enable the reading of a 9th prototype layer + spares)

dimensions: VME 6U x 220mm

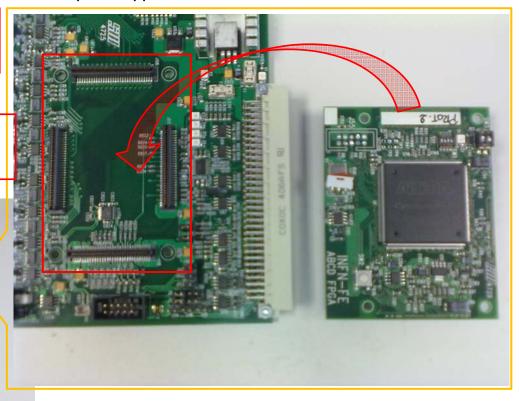

Outline of the "IFR ABCD" card

A.C.R. 2009-10-06

(Amplifier, Bias, Comparator, Data Processing)

IFR ABCD card: MMIC ampli design & test, schematics, and layout pre-placement by R. Malaguti, INFN-Ferrara

daughter card

Sept-29-2010

the

prototype

"pizza box"

FR\_ABCD

CONNECTOR TO THE "LST\_FE" CRATE BACKPLANE

16 pairs x 4 P-ECL outputs to the TDCs

32 x monitor outputs

(analog) from the

amplifiers

(on MMCX connectors)

96 pin DIN connector to the backplane

Detail of the digital "IFR\_ABCD" daughter card

32 x SiPM inputs (on MMCX connectors)

"IFR\_ABCD" card

#### "IFR\_ABCD" status update:

- · 8 boards delivered and tested

- 4 boards expected in TWO WEEKS

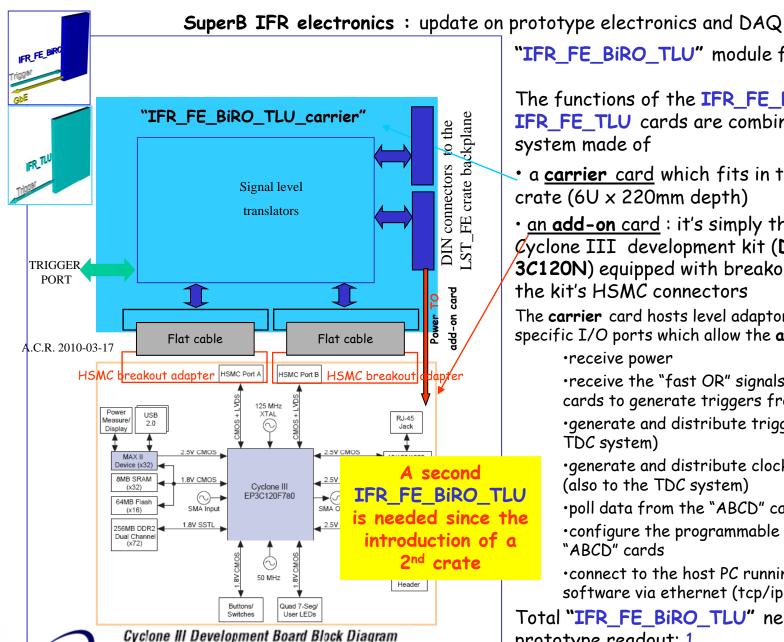

"IFR FE BiRO TLU" module features (new):

The functions of the IFR FE BiRO and of the IFR\_FE\_TLU cards are combined into a single system made of

- a carrier card which fits in the "LST\_FE" crate (6U  $\times$  220mm depth)

- an add-on card: it's simply the ALTERA Zyclone III development kit (DK-DEV-(3C120N) equipped with breakout adapters for the kit's HSMC connectors

The carrier card hosts level adaptors and application specific I/O ports which allow the **add-on** card to:

- ·receive power

- ·receive the "fast OR" signals from the "ABCD" cards to generate triggers from

- \*generate and distribute triggers (also to the TDC system)

- •generate and distribute clock and reset signals (also to the TDC system)

- ·poll data from the "ABCD" cards

- ·configure the programmable resources on the "ABCD" cards

- ·connect to the host PC running the DAQ software via ethernet (tcp/ip)

Total "IFR\_FE\_BIRO\_TLU" needed for the prototype readout: 1

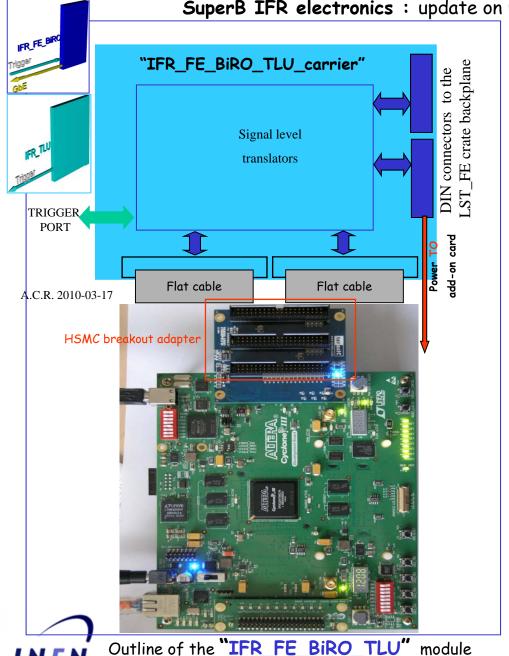

Outline of the "IFR FE BIRO TLU" module

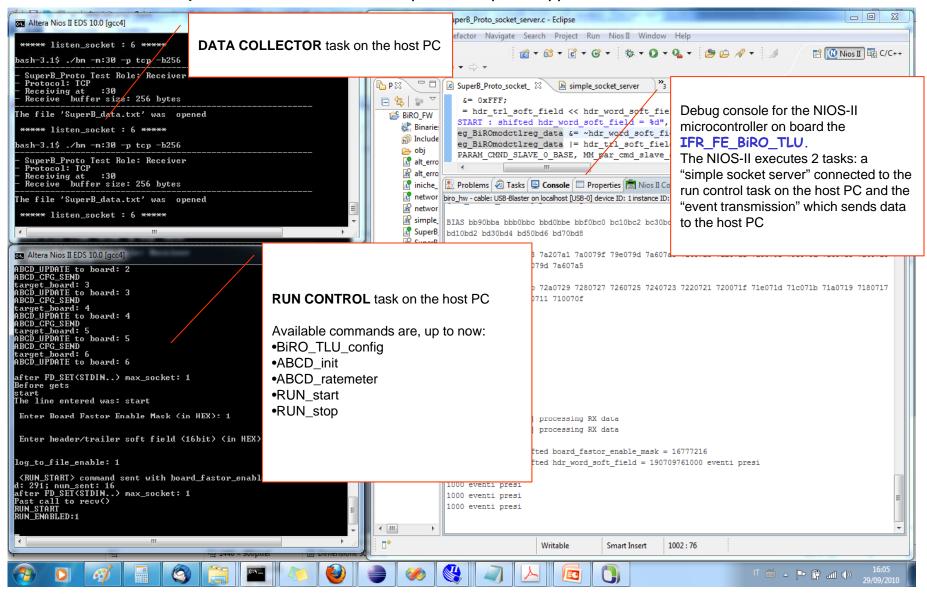

The FPGA on board the **add-on** card is connected to the RUN CONTROL/DAQ PC of the prototype test setup via an Ethernet port.

The FPGA features a NIOS-II microcontroller which implements the full TCP/IP stack.

The NIOS-II receives commands (i.e. START, STOP, INIT) from the RUN CONTROL/DAQ PC on a TCP server socket and sends data to a TCP server socket on the PC. Data is collected through the LST\_FE backplane from the "ABCD" cards upon a trigger request. The data collection section of the FPGA is coded in VHDL.

The FPGA of the add-on card generates the timing (clock and reset) for all the digitizers and handles the trigger distribution as well.

## "IFR\_FE\_BiRO\_TLU"

#### interface

## status update:

- · 2 carrier boards have been delivered

- · 2 assemblies have been tested and are being used to test the Binary Mode readout ("BiRO") crates

One more interface card will have to be stuffed to be kept as a spare

The "IFR\_FE\_BIRO" CRATE

# "IFR\_FE\_BiRO" crate status update:

A notebook PC is presently used to control the

IFR\_FE\_BiRO\_TLU board via Ethernet using

standard TCP/IP socket programming.

The IFR\_FE\_BiRO\_TLU has access to the IFR\_ABCD cards to configure them and read them out

In the current test setup the IFR\_ABCD cards are programmed to use their internal test pulse generators.

The "FAST\_OR" outputs of the IFR\_ABCD cards

are received by the IFR\_FE\_BiRO\_TLU which generates a trigger and reads out the boards through the crate's backplane.

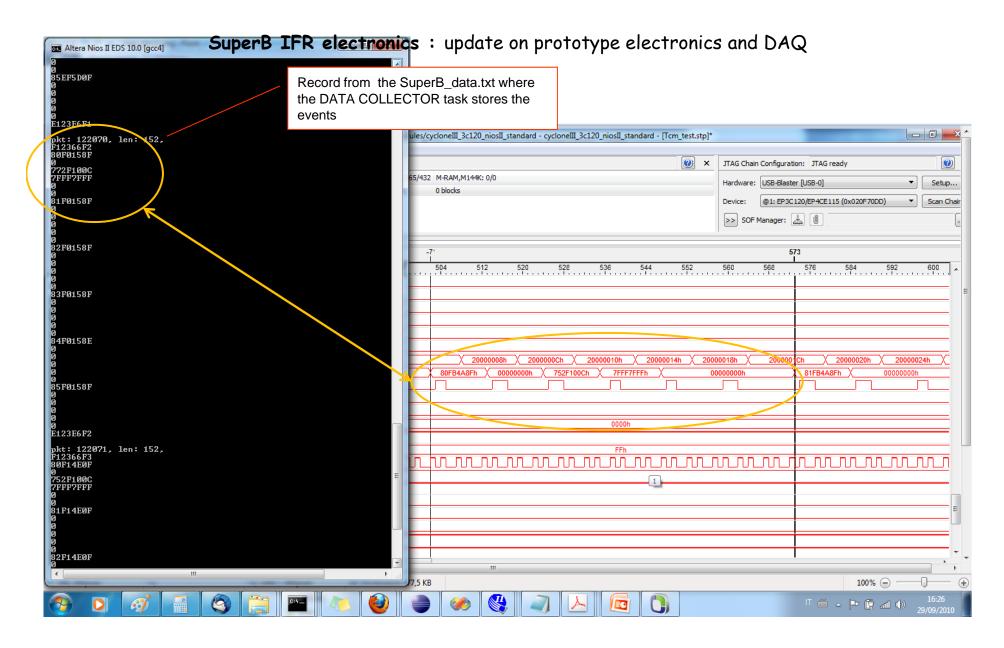

Internal pulser test results: screenshots from the notebook used to control and collect data from the IFR FE BiRO crate

11

SuperB IFR electronics: update on prototype electronics and DAQ 🔽 SignalTap II Logic Analyzer - C:/angelo/super8/CyIII\_development/TSEOptimized\_CyIII\_plus\_core\_modules/cycloneIII\_3c120\_niosII\_standard - cycloneIII\_3c120\_niosII\_standard - [Tcm\_test.stp]\* \_ 0 X File Edit View Project Processing Tools Window Instance Manager: 🍳 🕪 🔳 Ready to acquire JTAG Chain Configuration: JTAG ready (g) × Memory: 1867776 M512,MLAB: 0/0 M4K,M9K: 365/432 M-RAM,M144K: 0/0 Hardware: USB-Blaster [USB-0] ▼ Setup... auto\_sig... Not running 10929 cells 1867776 bits 0 blocks 228 blocks 0 blocks @1: EP3C120/EP4CE115 (0x020F70DD) Scan Chain >> SOF Manager: log: 2010/09/29 16:24:31 #0 Segnali di lettura per le schede ABCD readout\_serial\_ck\_56 readout\_serial\_ck\_78 readout\_shift\_enbl\_12 readout\_shift\_enbl\_34 readout\_shift\_enbl\_56 readout\_shift\_enbl\_78 ± BiRO\_module:BiRO\_module\_inst|tcm\_wr\_address 20000004h ± BiRO\_module:BiRO\_module\_inst|tcm\_wr\_data F1231CFCh BiRO\_module:BiRO\_module\_inst|tcm\_wrreq BiRO\_module:BiRO\_module\_inst[valid\_data\_word\_flag BiRO\_module:BiRO\_module\_ins Scrittura dei dati dell'evento nella memoria ±....O\_module:BiRO\_module 0000h BiRO\_module:BiRO\_module\_ins di pacchetto della porta TCP/IP ± spare\_SE\_nRst spare clk fpqa tlu\_in\_busy tlu\_in\_tnumclk tlu\_reset tlu\_reset\_nim\_out tlu\_reset\_nim\_out\_2 tlu\_reset\_nim\_out\_3 spare\_nrst\_fpga Il flag "datavalid" segnala al Data Setup NIOS-II della BiRO-DAO che il 1 pacchetto da 1 evento e' х Hierarchy Display: pronto e puo' quindi chiamare ■ V cycloneIII 3c120 niosII standard sopc:cycloneIII 3c120 niosII standard sopc instance la send() MM\_wr\_master\_of\_data\_tcm\_0:the\_MM\_wr\_master\_of\_data\_tcm\_0 auto\_signaltap\_0 00:25:50 □ = □ □ = □ □ □ □ □

Internal pulser test results: screenshots from the notebook used to control and collect data from the IFR FE BiRO crate

Internal pulser test results: screenshots from the notebook used to control and collect data from the IFR\_FE\_BiRO crate

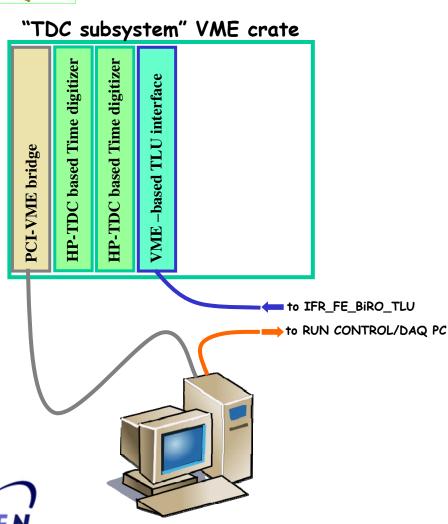

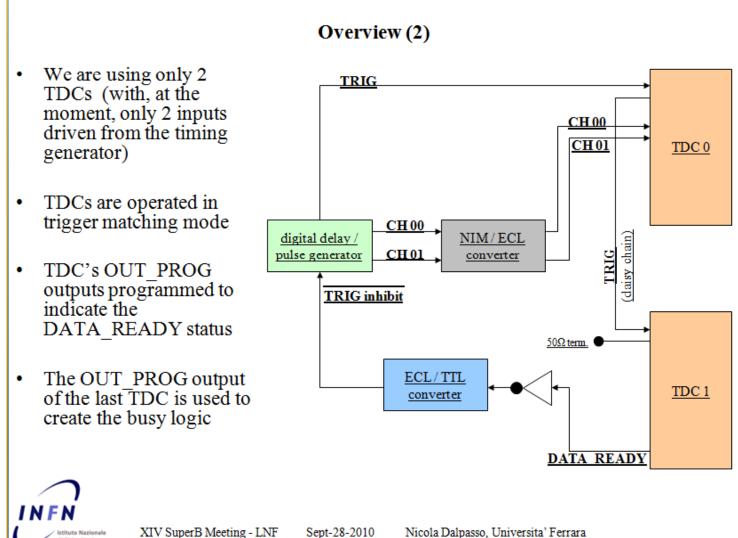

"TDC subsystem" features:

The **TDC** subsystem uses 2 commercial TDC modules based on CERN's HP-TDC to digitze the time of arrival of the pulses from the "ABCD" boards.

The TDC subsystem will also use a VME-based module to interface to the "IFR\_FE\_BiRO\_TLU" and receive trigger/timing signals

The **TDC** subsystem VME crate will be controlled and read out by the "TDC-PC" via a PCI-VME bridge.

The TDC\_PC will then send the triggered data to the RUN CONTROL/DAQ PC via a TCP/IP connection.

## "TDC subsystem" VME crate

HP-TDC based Time digitizer

HP-TDC based Time digitizer

VME –based TLU interface

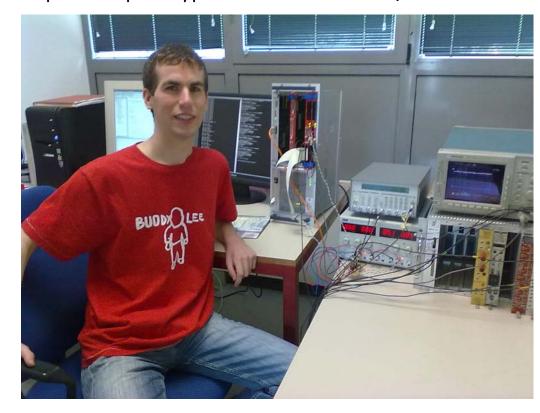

- · TDC readout: DONE

- port toward the Online Detector Control program : DONE,

- acknowledgments to Stefano Chiozzi, INFN-Ferrara and Nicola Dalpasso, above, undergraduate student at the Ferrara University

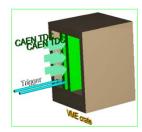

#### Introduction

- The aim is to read events from multiple TDC modules and send them to another computer via TCP / IP.

- · A busy logic is introduced to block new events before the previous is read.

- The TDC's readout buffer hold no data or the data of a single event.

Sept-28-2010

NICOLA DALPASSO, Universita' Ferrara

#### Overview

- The job of the TDC PC is:

- to respond to start/stop acquisition commands. The ACK and NACK messages confirm the correct execution of the operation. Data acquisition errors are signaled via an error message to the ODC.

- send acquired data to DAQ

- TCP/IP protocol is used for communication between TDC PC and DAQ / ODC.

XIV SuperB Meeting - LNF

Sept-28-2010

#### Read an event

- Steps to read a single event:

- wait the DATA\_READY flag for each TDC module, through polling the Status Register

- read all the data (enclosed between Global Header and Global Trailer) from the TDCs

- Busy logic: a new event active the OUT\_PROG output which is then negated an converted to TTL levels. This signal inihbit the trigger blocking the creation of new events. When all the data are read from the last TDC, the OUT\_PROG is deactived and the trigger is enabled.

Sept-28-2010

#### Format of the packets

Data from a single event are copied in a packet and a header (holding the total size of the packet) and a trailer are added. The packet is then sent to DAQ.

#### Example of a packet:

```

0x78600000: TDC PC HEADER: BYTE COUNT 0096: TRIGGER NUMBER 00000

0x4000001f: CAEN TDC GLOBAL HEADER: EVENT COUNT 00000000: GEO 31

0x0800076b: TDC CHIP HEADER: TDC 0: EVENT ID 00000000 : BUNCH ID 00001899

0x00076d52 : TDC DATA : EDGE 0 : CHANNEL 0000 : DATA 00486738

0x00176e97 : TDC DATA : EDGE 0 : CHANNEL 0002 : DATA 00487063

0x18000004 : TDC CHIP TRAILER : TDC 0 : EVENT ID 00000000 : WORD CNT 00000004

0x0900076b: TDC CHIP HEADER: TDC 1: EVENT ID 00000000: BUNCH ID 00001899

0x19000002 : TDC CHIP TRAILER : TDC 1 : EVENT ID 00000000 : WORD CNT 00000002

0x0a00076b: TDC CHIP HEADER: TDC 2: EVENT ID 00000000: BUNCH ID 00001899

0x1a000002 : TDC CHIP TRAILER : TDC 2 : EVENT ID 00000000 : WORD CNT 00000002

0x0b00076b: TDC CHIP HEADER: TDC 3: EVENT ID 00000000: BUNCH ID 00001899

0x1b000002 : TDC CHIP TRAILER : TDC 3 : EVENT ID 00000000 : WORD CNT 00000002

0x8400019f:CAEN TDC GLOBAL TRAILER:STATUS 4:WORD CNT 00000012:GEO 31

0x4000001f: CAEN TDC GLOBAL HEADER: EVENT COUNT 00000000 : GEO 31

0x08000115 : TDC CHIP HEADER : TDC 0 : EVENT ID 00000000 : BUNCH ID 00000277

0x18000002 : TDC CHIP TRAILER : TDC 0 : EVENT ID 00000000 : WORD CNT 00000002

0x09000115:TDC CHIP HEADER:TDC1:EVENT ID 00000000:BUNCH ID 00000277

0x19000002 : TDC CHIP TRAILER : TDC 1 : EVENT ID 00000000 : WORD CNT 00000002

0x0a000115 : TDC CHIP HEADER : TDC 2 : EVENT ID 00000000 : BUNCH ID 00000277

0x1a0000002 : TDC CHIP TRAILER : TDC 2 : EVENT ID 00000000 : WORD CNT 00000002

0x0b000115 : TDC CHIP HEADER : TDC 3 : EVENT ID 00000000 : BUNCH ID 00000277

0x1b000002 : TDC CHIP TRAILER : TDC 3 : EVENT ID 00000000 : WORD CNT 00000002

0x8400015f: CAEN TDC GLOBAL TRAILER: STATUS 4: WORD CNT 00000010: GEO 31

0xb8000000 : TDC PC TRAILER : STATUS ERROR 0000 : TRIGGER NUMBER 00000

```

XIV SuperB Meeting - LNF

Sept-28-2010

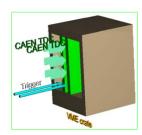

#### Behavior of the TDC PC

- The behavior of the data acquisition program is illustrated in the FSM bubble diagram. Blue lines mean the operation requested succeeds, otherwise a red line is used.

- For each command received, an ack/nack message is sent.

- Running errors are signaled to the OCL via an error message and the running continue.

- INIT is the initial state: in this state a TDC setup is done and then the program waits for connection from the OCL.

XIV SuperB Meeting - LNF

Sept-28-2010