## Low Level RF for superB

Olivier BOURRION

LPSC Grenoble

September 28, 2010

### Table of Contents

- LLRF motivation reminder

- Peedback techniques

- Direct RF feedback

- One turn delay feedback

- 3 Loop implementation

- Loop details

- Hardware plateform

- A few technical details

- 4 Conclusions and questions

#### Table of Contents

- LLRF motivation reminder

- Peedback techniques

- Direct RF feedback

- One turn delay feedback

- 3 Loop implementation

- Loop details

- Hardware plateform

- A few technical details

- 4 Conclusions and questions

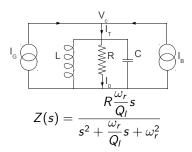

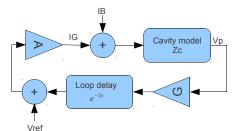

## Cavity model

- $I_G$  Generator current

- I<sub>B</sub> Beam current

- $I_{\mathrm{T}}$  Cavity current  $(\overrightarrow{I_T} = \overrightarrow{I_G} + \overrightarrow{I_B})$

- I<sub>0</sub> Loss current in shunt resistance

- V<sub>C</sub> Cavity voltage

- Q1 Loaded quality factor

- ullet High intensity beam o cavity voltage perturbated by  $I_B$

- Objective: maintain constant  $V_C$

- $I_G$  contribution should compensate  $I_B$

- ullet Modulation of  $I_B o ext{modulation } I_G$

4/30

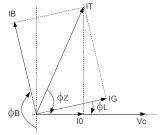

# Cavity tuning / phasor diagram

- $\phi_{\rm L}$  Loading angle

- $\phi_{Z}$  Cavity tuning angle

- $\phi_{\rm B}$  Stable phase angle (above transition  $I_B$  points upward)

- From diagram study:  $\tan \phi_Z = \tan \phi_0 + \frac{I_B}{I_B} (\tan \phi_0 \sin \phi_B + \cos \phi_B)$

- Maintaining generator current in phase with cavity voltage  $\rightarrow$  $\tan \phi_Z = \frac{I_B}{I_B} \cos \phi_B$

- Cavity tuning angle increase with current

- Frequency shift due to cavity tuning  $\delta f = -f_{RF} \frac{Z_{sh}}{O} \frac{I}{V_{PF}} N_c$

In LER: 233 kHz In HER: 252 kHz

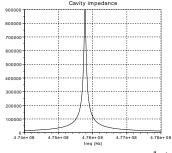

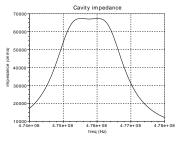

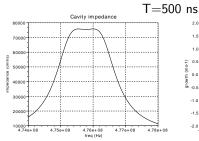

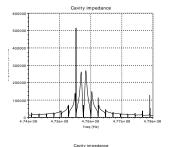

## Instabilities and cavity impedance

Instabilities growth rates proportionnal to the cavities impedance:

$$au_l^{-1} pprox rac{el_B F_{rf} \alpha}{2EQ_s} \left[ Re \ Z_c(\omega_{rf} + l\omega_{rev} + \omega_s) - Re \ Z_c(\omega_{rf} - l\omega_{rev} - \omega_s) \right]$$

Applying this to the detunned cavity impedance yields:

- mode -1 growth rate is 33 ms<sup>-1</sup> (baseline LER)

- Comparable to synchrotron frequency  $(1/ au_{-1})/\omega_{s}\sim 0.5$

- Exceed the radiation damping rate (LER damping time =20.3 ms)  $(1/\tau_{-1})/(1/\tau_d)\sim 670$

#### Table of Contents

- LLRF motivation reminder

- Peedback techniques

- Direct RF feedback

- One turn delay feedback

- 3 Loop implementation

- Loop details

- Hardware plateform

- A few technical details

- 4 Conclusions and questions

# Direct RF feedback (1/2)

Expected impedance reduction

$$Z_{fbk}(\omega) = \frac{Z(\omega)}{1 + GAe^{-jT\Delta\omega}Z(\omega)}$$

- In theory the highest gain *GA* is desired:

- Maintain loop stability → Phase Margin is impacted by loop delay

- Canonical value of PM =  $\pi/4$  yields

$$GAR \le \frac{Q}{\omega_r} \frac{\frac{\pi}{4T} + 2\omega_r}{1 + \omega_r \frac{4T}{T}} = G_{max}AR$$

Impedance reduction limited by the loop delay T

# Direct RF feedback (2/2)

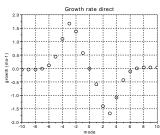

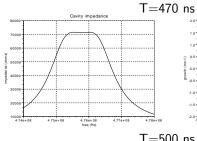

• Plots with loop gain =  $1.3 \times G_{max}AR$  (flat response) and T=440 ns (PEP2 delay value)

- Maximum impedance decreased by a factor of 12.8

- -1 Mode is damped by a factor of 20

- Side effect: other modes growth rates are increased!

- More impedance reduction is needed

# Delay influence

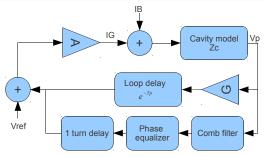

## Comb filter feedback principle

- Overcome loop delay limitation

- Correction applied with one turn delay

- Minimize impedance at certain frequencies

- Attenuation needed at synchrotron sidebands  $\rightarrow$  dual peaked comb filter  $H_{comb}(jw) = \frac{G(1-e^{-jwT_{rev}})}{1-2K\cos(2\pi\nu_s)e^{-jwT_{rev}}+K^2e^{-j2wT_{rev}}}$

- Response is modified by the complement to reach one turn delay  $H(jw) = H_{comb}(jw) \times e^{-jw(T_{rev} T_g})$

- ullet Out of klystron bandwidth, large dephasing o loop instability

- ullet Precompensation of the dephasing o phase equalizer

### Comb filter feedback limitations

- Gain margin of 10 dB for loop stability (when  $\phi=\pi$ )  $G_{max} \leq \frac{1+2K\cos(2\pi\nu_s)+K^2}{6}$

- The closest K come to the unity, higher the gain, and narrower the bandwidth

- Max gain on comb loop is function of K

- with K=63/64 G=0.655

- with K=127/128 G=0.660

- PEP2 practical value was 0.2? Something to understand here

- Reminder: longitudinal radiation damping rate: 0.0492 ms<sup>-1</sup>

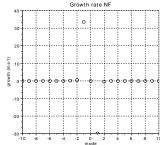

### **Simulations**

$$K = 63/64$$

$\begin{array}{c} \textrm{K=}127/128 \\ \textrm{33 ms}^{\textrm{-}1} \rightarrow \\ \textrm{0.05 ms}^{\textrm{-}1} \end{array}$

### Table of Contents

- LLRF motivation reminder

- Peedback techniques

- Direct RF feedback

- One turn delay feedback

- 3 Loop implementation

- Loop details

- Hardware plateform

- A few technical details

- 4 Conclusions and questions

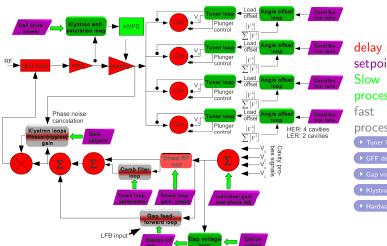

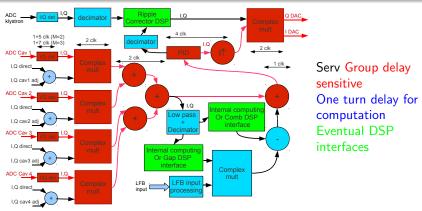

### LLRF feedback overview

delay sensitive setpoints processing

processing

## Cavity tuning

#### Tuner loop

- Minimizing of the phasing between cavity probe signal and cavity forward voltage

- Setpoint: load offset angle

#### Angle offset loop

PEP2 implementation arguments. Since all cavities have the same voltage applied, it may be necessary to:

- decrease the gap voltage by having non zero angle. Lowers voltage on fragile cavity

- compensate eventual misphasing between beam and generator current (relative beam phase due to geometry, waveguide length, ...)

# Gap feedforward (1/2)

#### Problem

- Gap in the ring, is like an amplitude modulation of the beam current

- Current generator with feedback loop is there to compensate beam current effect on the cavity

- Empty bunch → cavity voltage is not degraded by beam current, power not extracted by beam, unnecessary power used

- Need a way to avoid unnecessary modulation of the klystron

# Gap feedforward (2/2)

#### Solution

- Detect periodic gap transients by sampling cavity sum signal over one turn

- Adaptative filtering is done by combining previous sampling and station I&Q reference in order to minimize the gap transient effect

- Orrection is applied one turn later

#### Longitudinal feedback input

- In order to provide more power for kicking lower order mode

- Cosine and sine of LFB kick is applied to Q & I outputs of the model respectively

## Gap voltage loop

#### Gap voltage has to be maintained constant

- Direct RF loop works well to damp transient but the loop gain is small

- Workaround: use a slow loop that will modify setpoints (station I&Q reference)

- Minimize error at fundamental frequency between gap voltage and forward voltage with higher gain

## Klystron loops

- Anti saturation loop

- tend to maintain a constant drive power by changing HVPS

- → Keep Klystron out of saturation

- Klystron gain loop

- Direct RF and comb loop must see a constant klystron gain

- But previous loop plays with HVPS in order to keep constant drive power

- This loop hides gain changes due to HVPS changes

- Klystron ripple (or phase) loop

- Changes in HVPS induces phase shift in the klystron

- Slow changes due to anti saturation loop could be hidden by a slow loop

- ullet However HVPS usually display ripples o fast computation needed

▶ Back to loops overview

Hardware p

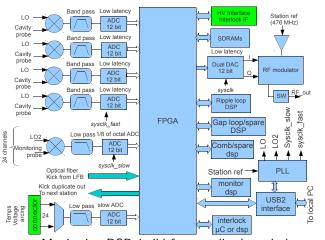

## All digital solution

- Digital Down

Conversion

- Group delay is critical

- Data in one board

- Computing power

- Memories for fault recording and excitation

- Monitoring DSP, build fast amplitude and phase monitoring signals

- Interlock interfaces (arcing???)

# FPGA content - focus on latency critical path

- The sharper the CIC filter, the larger the group delay

- PID used as lead compensator, negative group delay!

- PEP2 RFP module had 86 ns of I/O delay, BW=3 MHz (Teytelman)

- Total duration 17/19 + 12 due to ADC/DAC is 29/31 clock cycles

• Worst case: at 250 MHz  $\rightarrow$  31  $\times$  4 ns = 124 ns! • back to delay influence

# Digital Down Conversion (DDC) (1/2)

#### Principle

- Bring bandwidth of interest to baseband by multiplying a signal at Intermediate Frequency by a sine and cos at the same IF frequency

- Benefits:

- No dissymmetry in I&Q pathes (path length, encoding, ...)

- No susceptibility to DC offsets

- Focus on latency critical path

# Digital Down Conversion (2/2)

Simplification possible by using  $Fs = 4 \times IF$  in the limited latency path.

- Easier to implement, doesn't need real multipliers and sine/cos table (values 0,1,-1,0)

- Input should be clean or steeply bandpass filtered  $\rightarrow$  at the cost of group delay!!

- Mixer quality (IF harmonics!) → existing chips have attenuation of first harmonics <-65 dB</li>

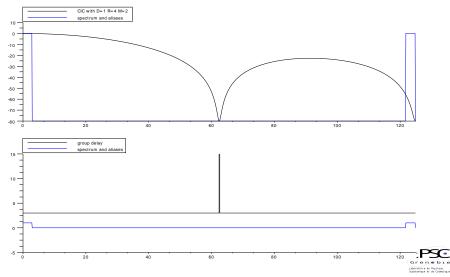

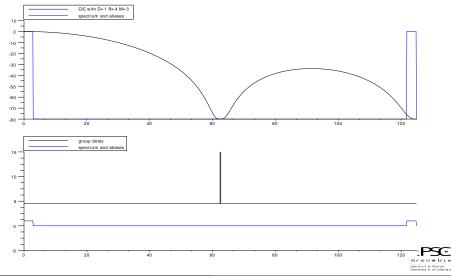

## CIC design

M integrators

decimator

M combs

- Very simple to implement in FPGA

- Only additions/substractions

- Following slides will present two sets of parameters (D=1,R=4, M=2 or M=3).

- Interesting to note filter selectivity vs group delay.

# CIC design

# CIC design

#### Table of Contents

- LLRF motivation reminder

- 2 Feedback techniques

- Direct RF feedback

- One turn delay feedback

- 3 Loop implementation

- Loop details

- Hardware plateform

- A few technical details

- Conclusions and questions

#### Conclusion

- By simulation, the highest growth rate should be 0.05 ms<sup>-1</sup>, in real life should be a little bit higher

- All feedbacks can be implemented in a digital fashion (FPGA or software for slow loop) → Flexibility and maintenability

- Determine necessary signal range for an optimal feedback (filtering vs group delay)

- Any comments or questions?

## Open questions

- How to test an electronic prototype?

- Possible to build a test setup with klystron, RF source, cavity, ???

- Have access to a similar installation?

- Samples of very technical questions:

- Tuner, HVPS, interlock interfaces?

- Amplifier drive level? Need output attenuator (fix or programmable?)

- Klystron recommended drive power

- Klystron model for lead compensator

- Arc interlock module ?

- ...

- Interlocutors are needed