#### Outline

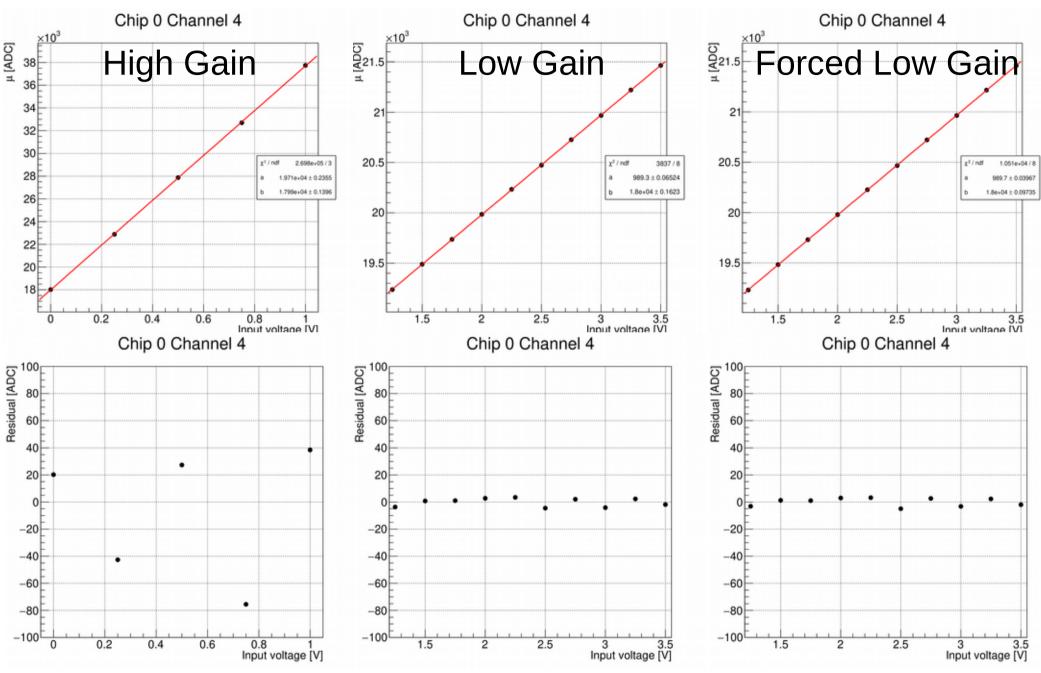

**PURPOSE** Test calibration mode on the HiDRA board 6 **METHOD** Data acquired in three different configurations:

- For High Gain V<sub>cal</sub> in [0, 1] V

- For Low Gain V<sub>cal</sub> in [1.25, 3.5] V

- For Forced Low Gain (G2SEL on) V<sub>cal</sub> in [1.25, 3.5] V

CAVEAT Among the four chips mounted on the board, the first two work correctly, whereas strange a behavior was found on the last two (both in acquisition and calibration mode): for this reason we present here the results relative to the channels of the **first chip** only.

## HiDRA Gain - Chip 0 Channel 4

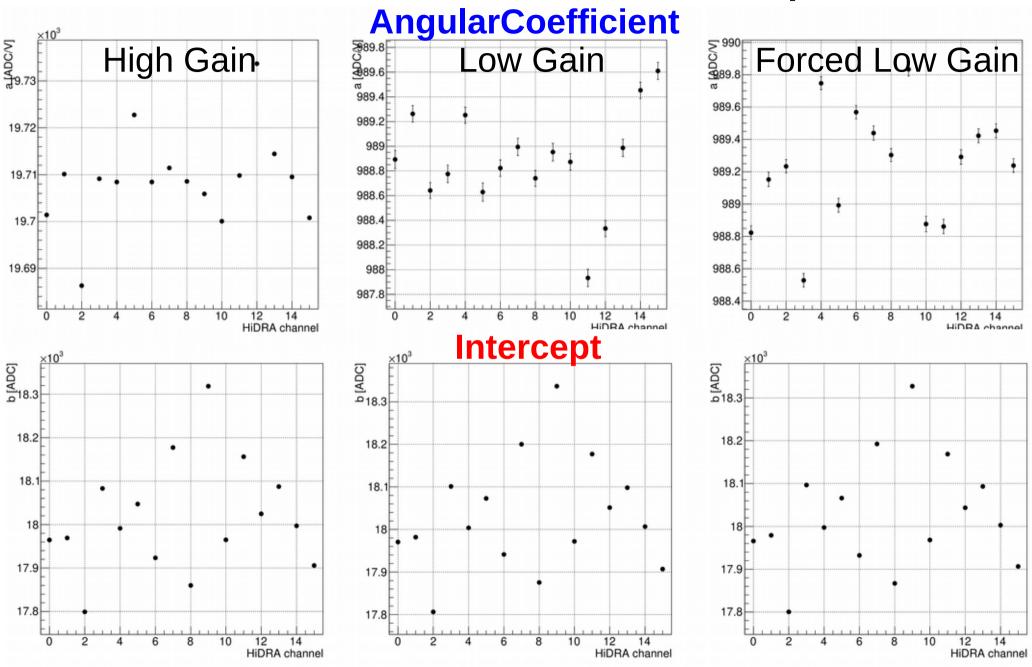

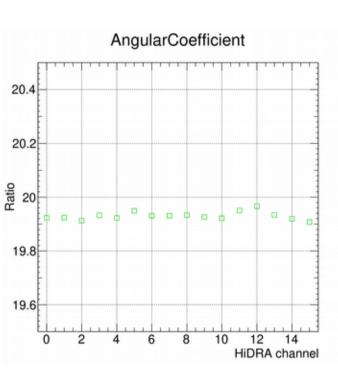

### Linear Coefficient - Chip 0

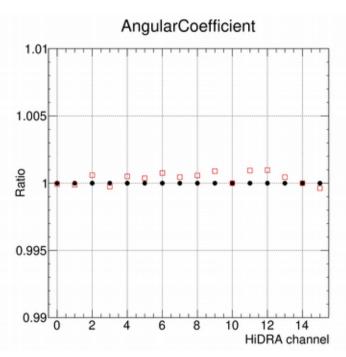

### Linear Coefficient Ratio - Chip 0

### Back Up

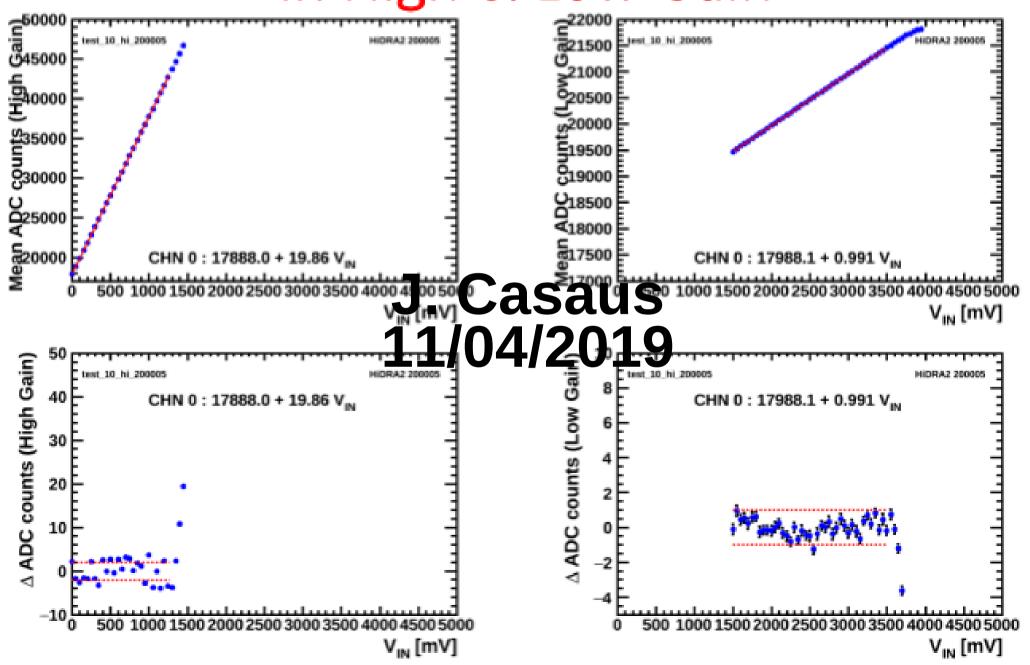

# Gain Calibration: Linearity Range in High & Low Gain

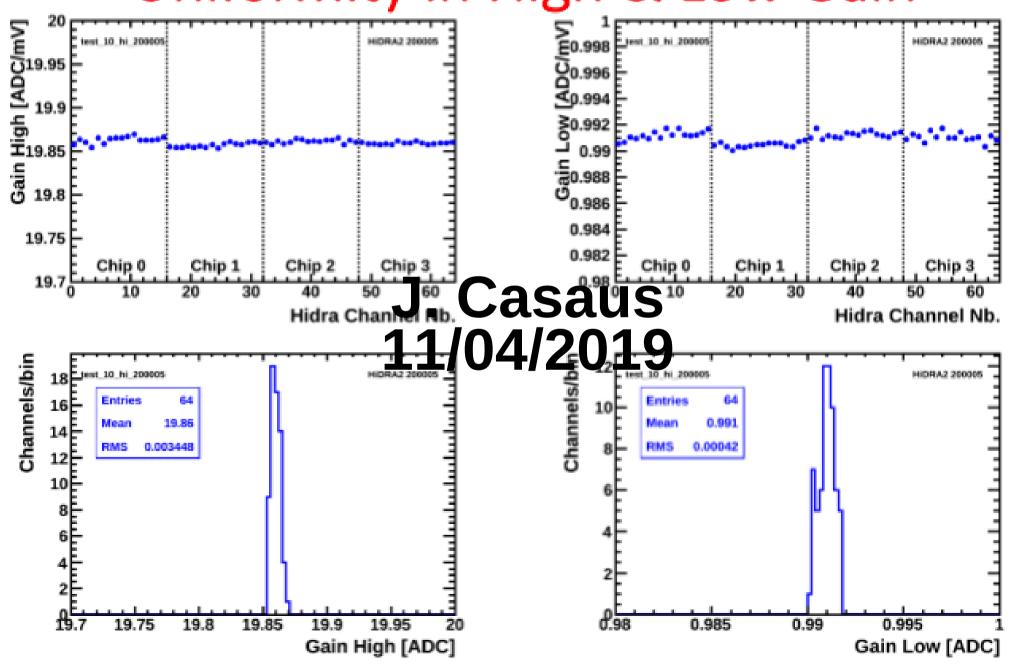

# Gain Calibration: Channel Uniformity in High & Low Gain

# Gain Calibration: Channel Uniformity in High & Low Gain

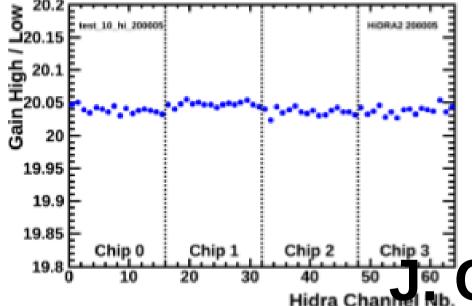

Results on HiDRA2 Board 200005

#### Pedestals & Noise:

- Pedestal values in the 17500 18200 range

- Noise in the range 10 14 ADC with a clear odd-even channel structure

- Average High/Low 20.04

- All channels within 0.1% of the average