# Developments of Stitched Monolithic Pixel Sensors towards the application in the ALICE ITS3

Gianluca AGLIERI RINELLA

On behalf of the ALICE Collaboration

### Outline

Introduction to ALICE ITS3

**Sensor Developments**

Monolithic Stitched Sensor Prototype (MOSS)

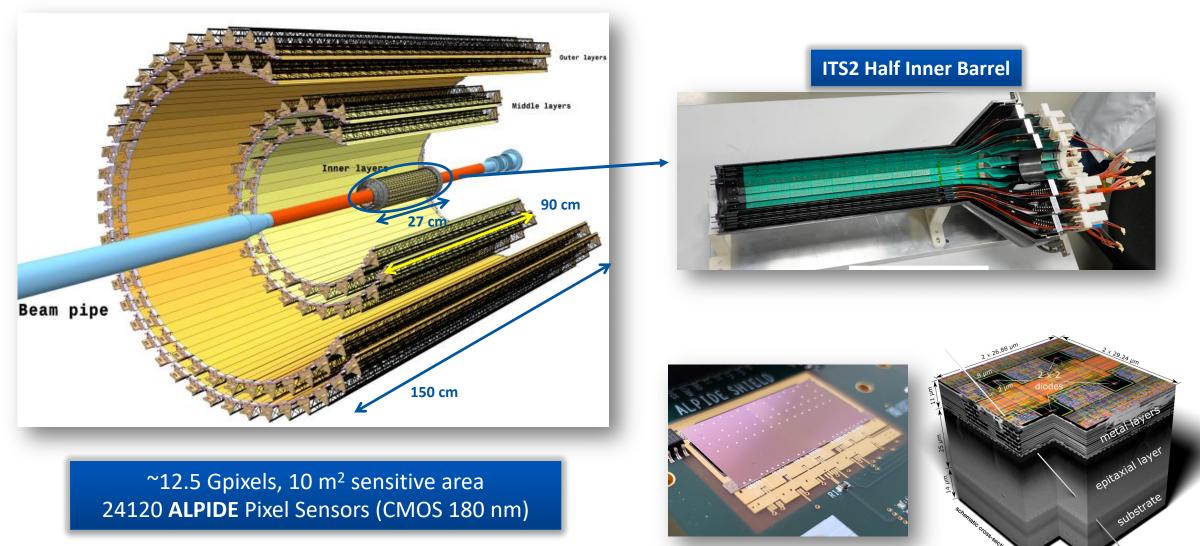

# **ALICE ITS2 Inner Tracking System**

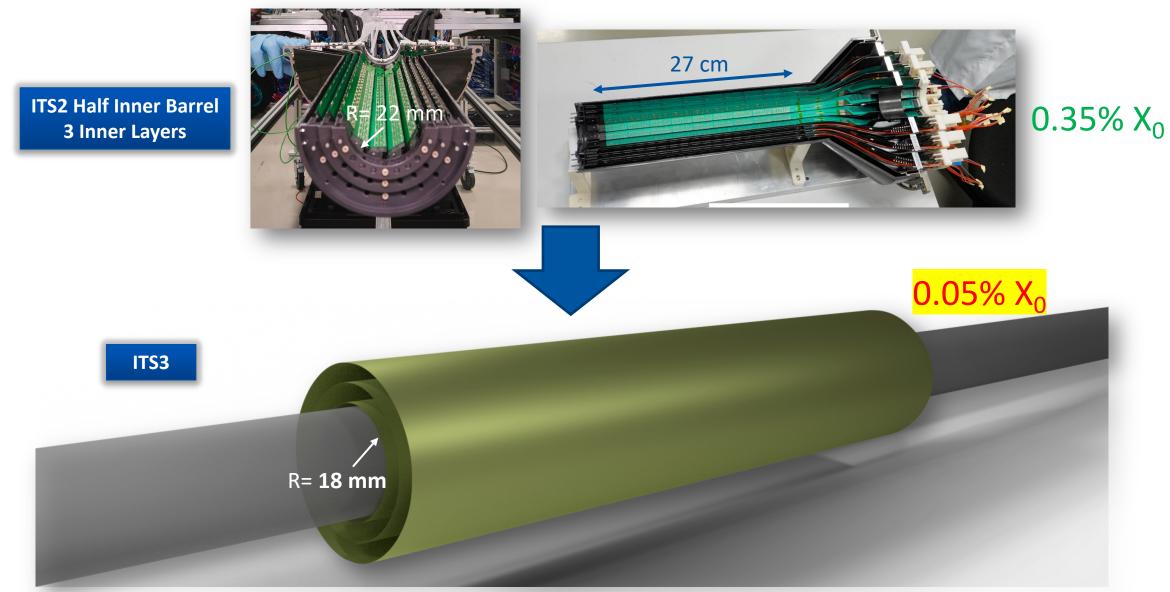

# **ITS3 Concept**

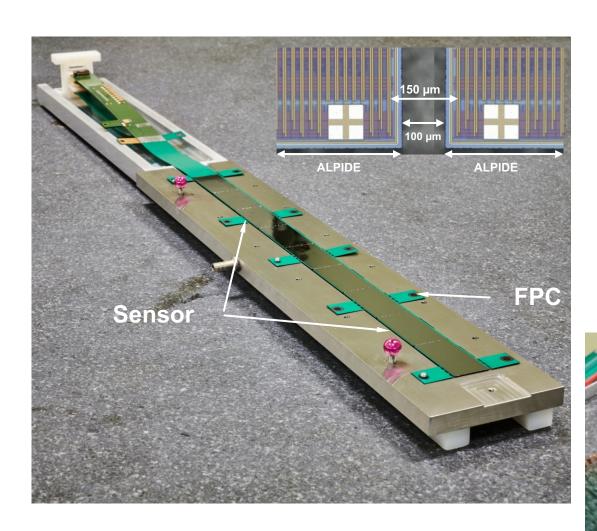

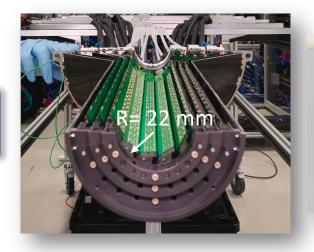

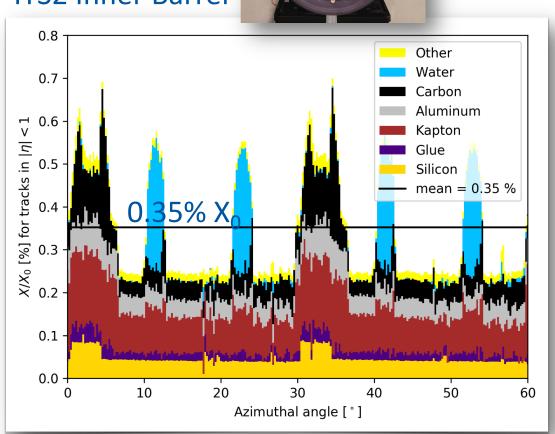

ITS2 Half Inner Barrel

3 Inner Layers

# **ITS3 Concept**

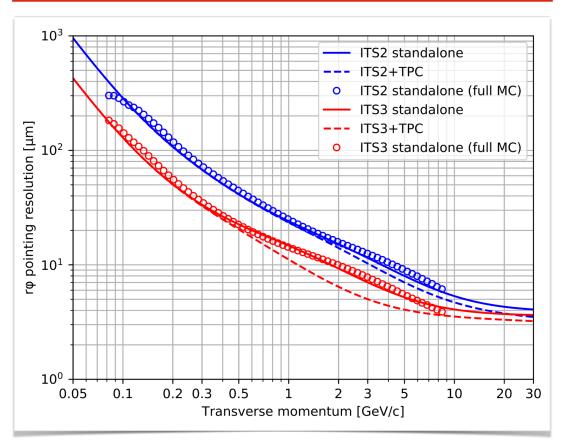

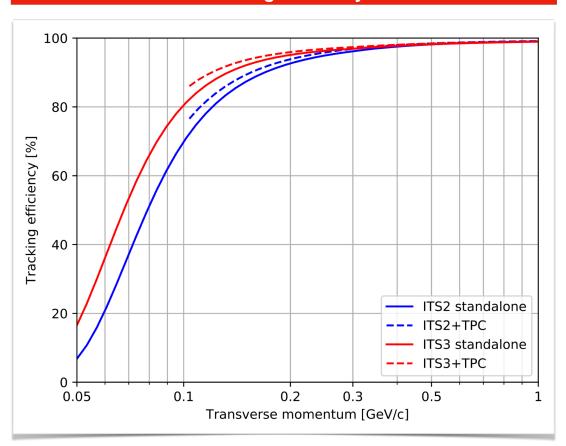

# **Enhanced Tracking Performance**

#### tracking efficiency

improvement of factor 2 over all momenta

large improvement for low transverse momenta

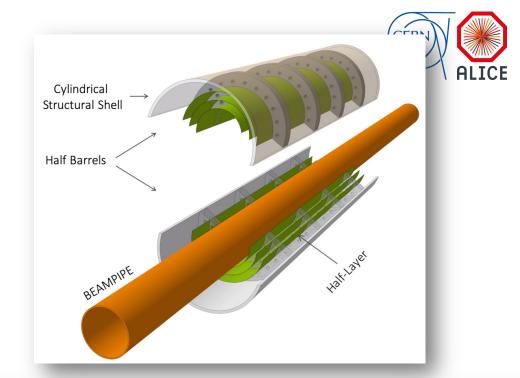

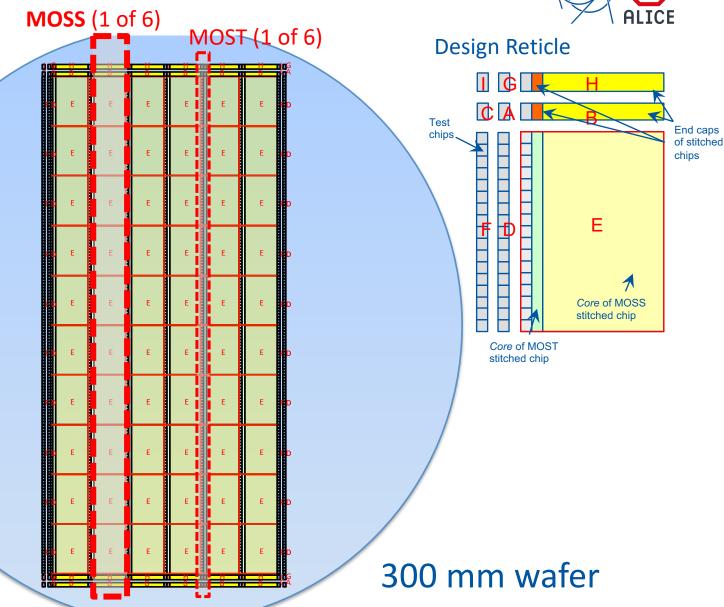

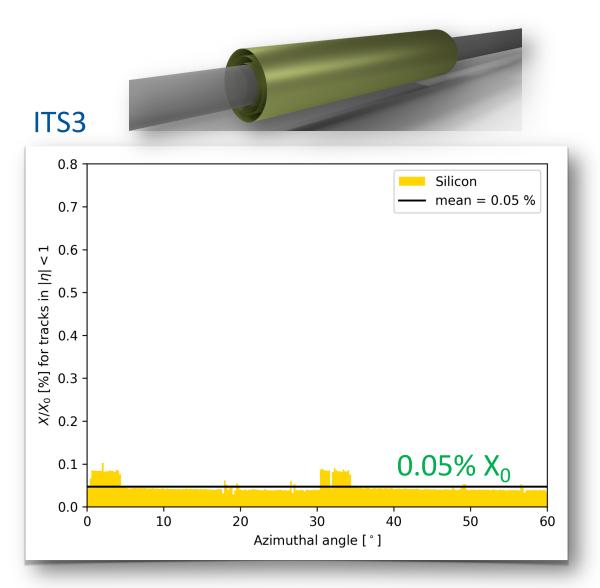

## ITS3 Layout and Requirements

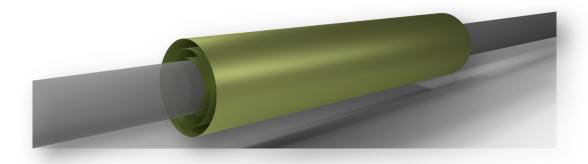

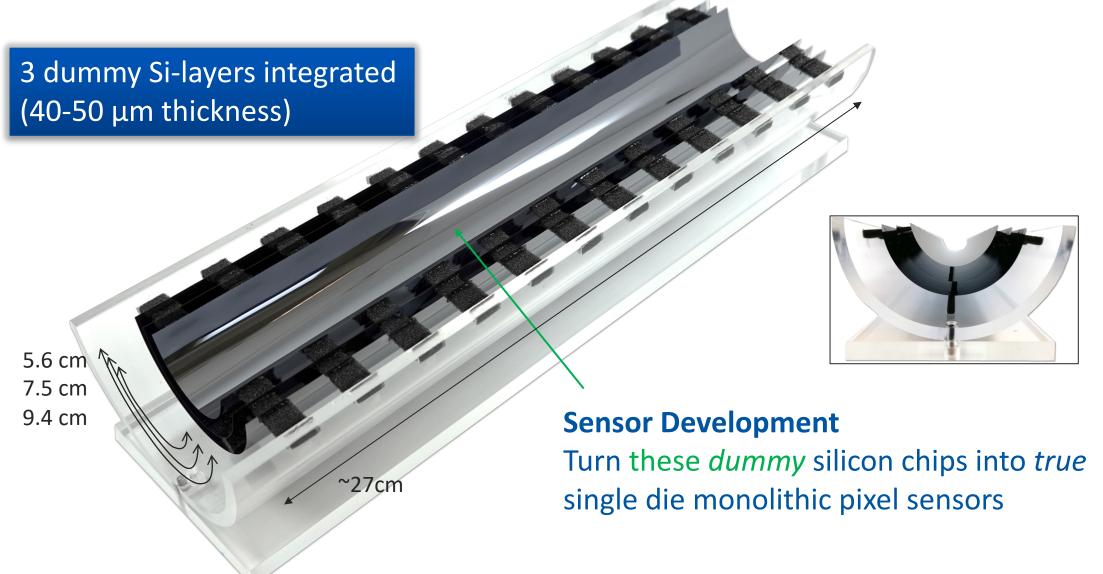

### 3 Cylindrical layers

Made with 6 curved wafer-scale single-die

Monolithic Active Pixel Sensors

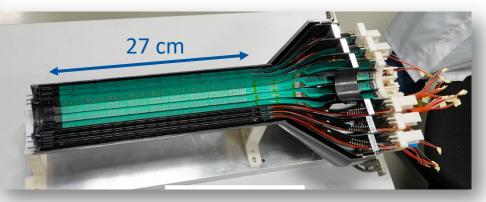

Radii 18/24/30 mm, length **27 cm**

Thinned down to <**50 μm**

Position resolution ~5 μm

-> Pixels  $\Theta(20 \mu m)$

#### Electro-mechanical integration

**No flexible circuits** in the active area

-> Distribute supply and transfer data on chip to the short edge

#### Cooling by air flow

-> Dissipate less than 20 mW/cm<sup>2</sup>

ALICE ITS3 LoI CERN-LHCC-2019-018 / LHCC-I-034

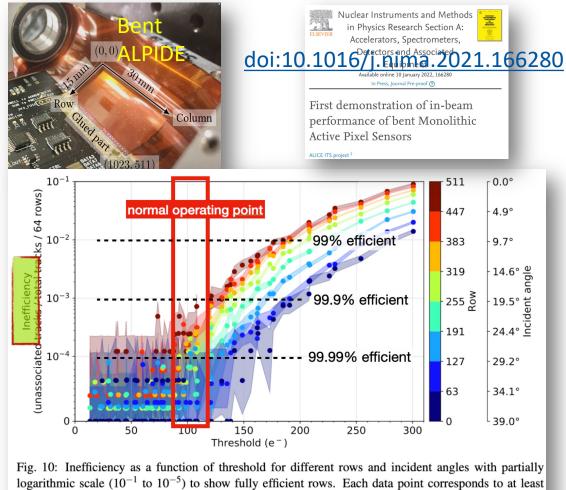

# Can Bent Sensors Actually Work?

8k tracks.

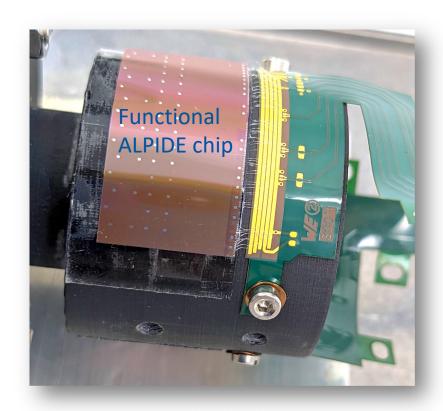

Series of beam tests with bent ALPIDE chips

Working of bent sensors demonstrated with ALPIDE

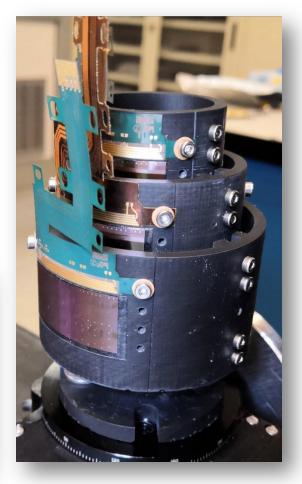

# Bending and Integrating large-thin silicon dies

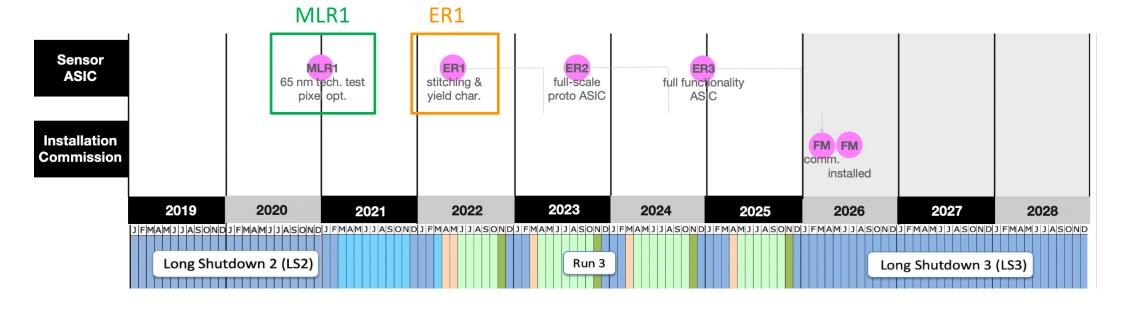

## Sensor Development Roadmap

#### Technology

TPSCo ISC 65 nm CMOS Imaging 300 mm wafers + Stitching

#### Silicon submissions

MLR1 (Q4 2020)

ER1 (Q2 2022)

# Design activities framed within **CERN EP RnD WP1.2**

Share and coordinate development and design efforts by several teams and institutes inside and outside ALICE

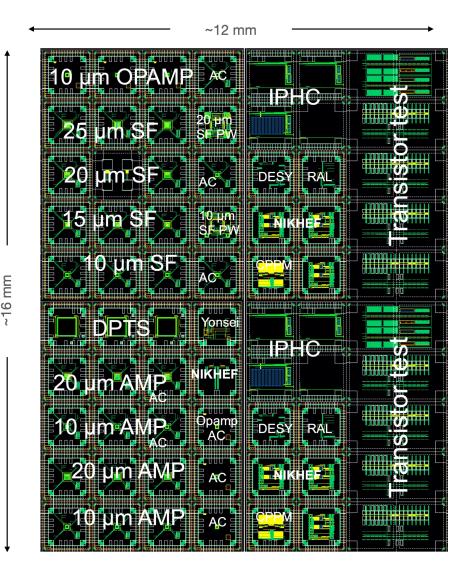

### MLR1 Submission – December 2020

### First submission in 65 nm CMOS Imaging

Learn technology features

Characterize devices

### Prototype circuits, blocks and pixel structures

$1.5 \times 1.5 \text{ mm}^2 \text{ test chips}$

## MLR1 Learnings

#### **Transistors Tests Structures**

Working as expected and similar to other 65 nm technology characterized for HEP

### Building blocks proven in silicon

Bandgap, DACs, Temperature sensor, VCO

### **Pixel Prototypes**

APTS, DPTS, CE65

Detailed characterisation ongoing

### **Process Optimisation**

Increase margins on sensing performance

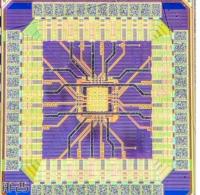

#### **APTS**

4x4 pixel matrix 10, 15, 20, 25 μm pitches Pixel variants Direct analogue readout

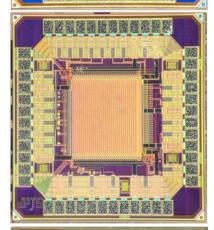

#### **DPTS**

32 × 32 pixels 15 μm pitch Asynchronous digital readout ToT information

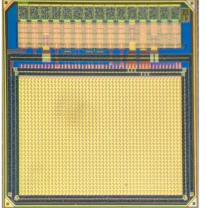

#### **CE65**

$64 \times 32$  pixels 15  $\mu m$  pitch Rolling shutter analog readout 3 pixel architectures

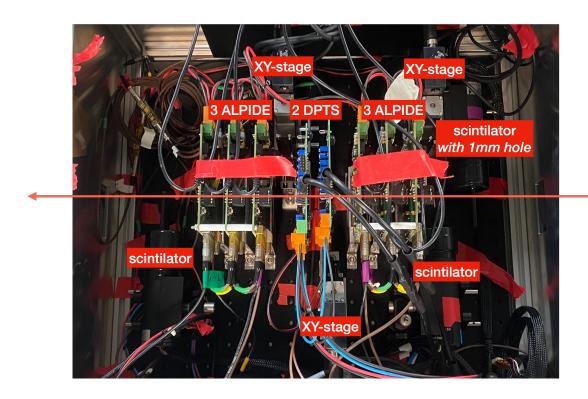

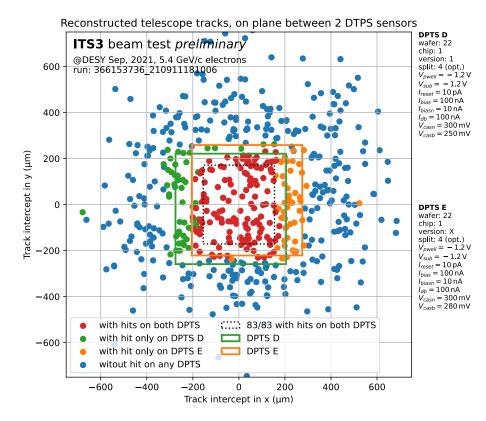

# Selected Example: Beam Tests with DPTS chips

### Detection efficiency >99.5%

Multiple beam tests

Detailed analysis ongoing, including irradiated samples

CERN EP Detector Seminar 24/09/2021

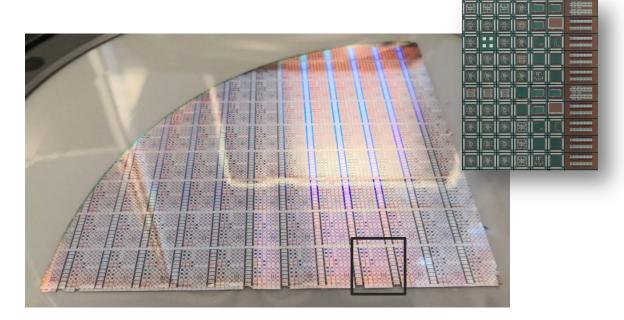

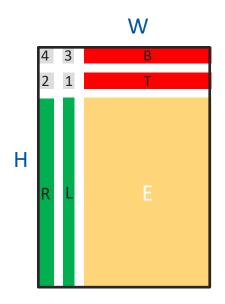

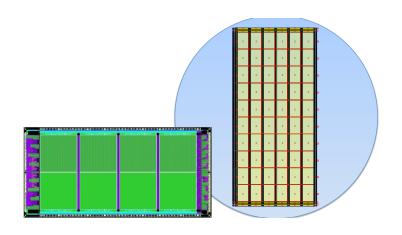

# Stitching

# Circuits on wafer $n \times W$

Design Reticle (typ. 2×3 cm)

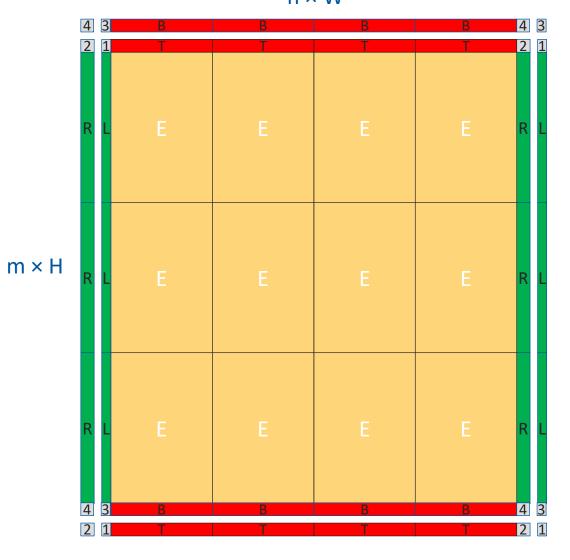

### **ER1 Submission**

Learn and prove stitching

Two large *stitched* sensor chips (MOSS, MOST)

Different approaches for resilience to manufacturing faults

### Small test chips

**Pixel Prototypes**

Fast Serial Links

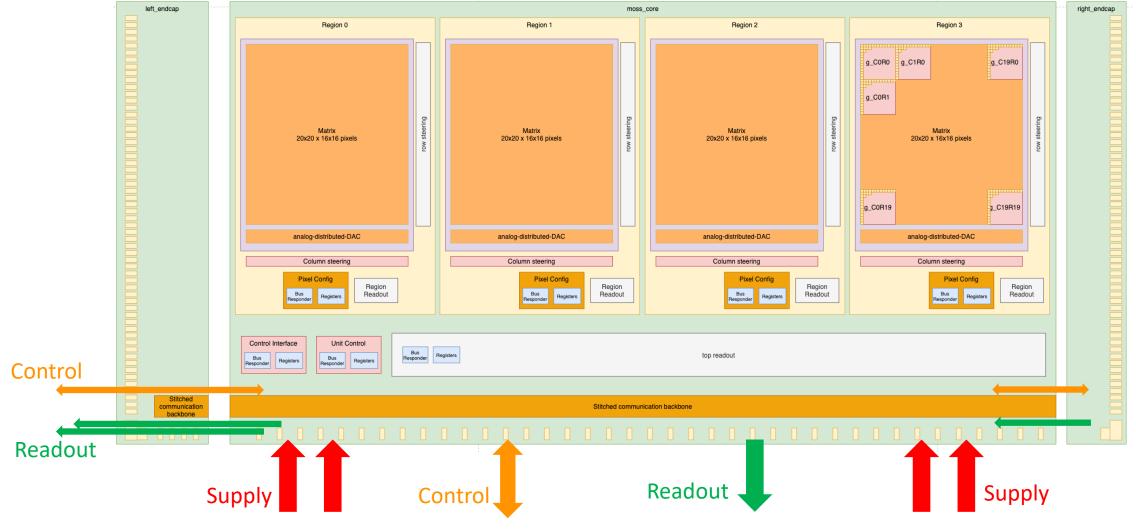

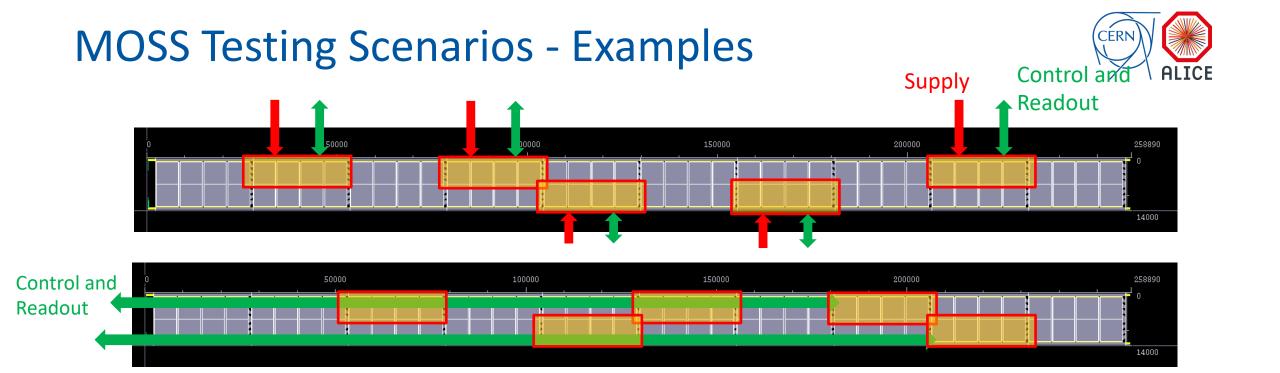

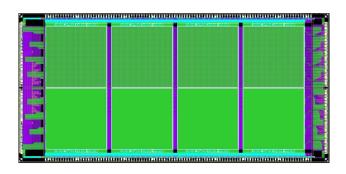

## MOSS Monolithic Stitched Sensor Prototype

#### **Primary Goals**

Learn Stitching technique to make a particle detector

Interconnect power and signals on wafer scale chip

Learn about yield and DFM

Study power, leakage, spread, noise, speed

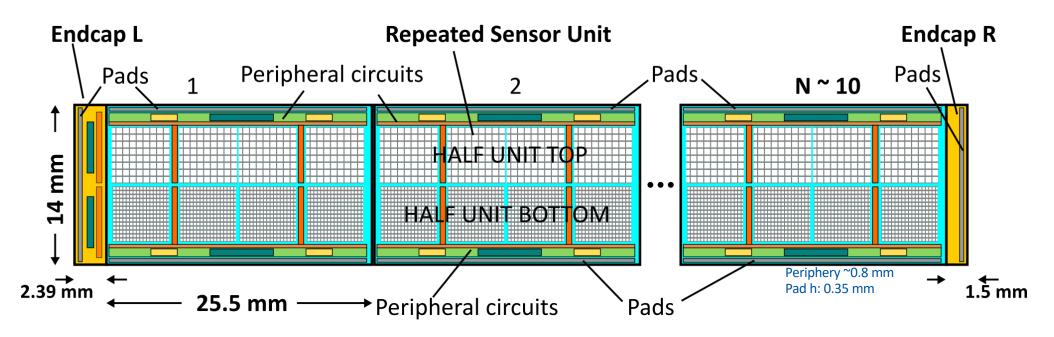

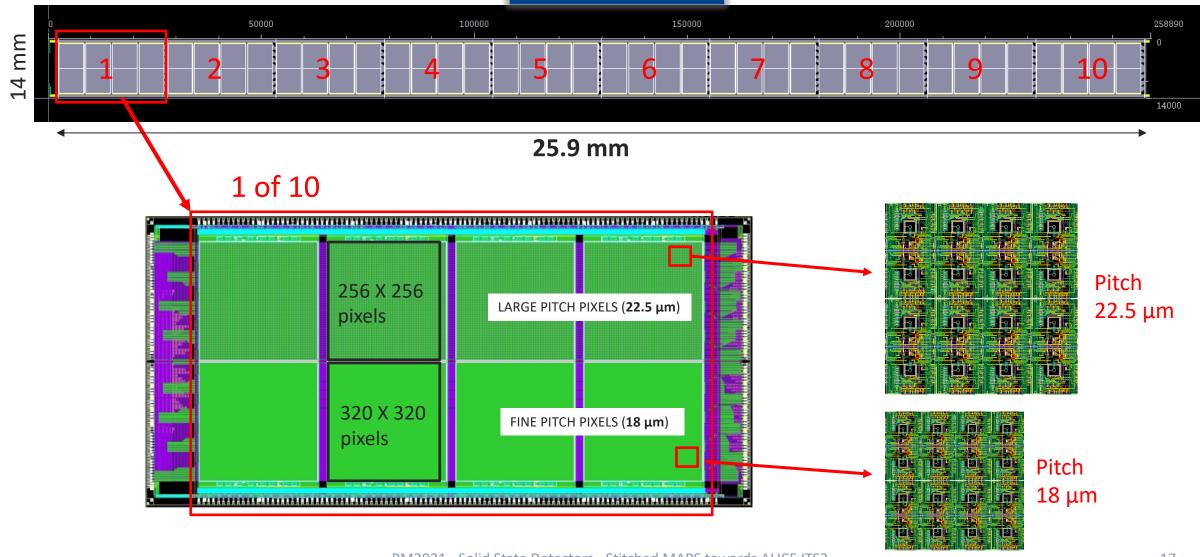

#### Repeated units abutting on short edges

Repeated Sensor Unit, Endcap Left, Endcap Right

Functionally independent

Stitching used to connect metal traces for **power** distribution and long range on-chip interconnect busses for control and data readout

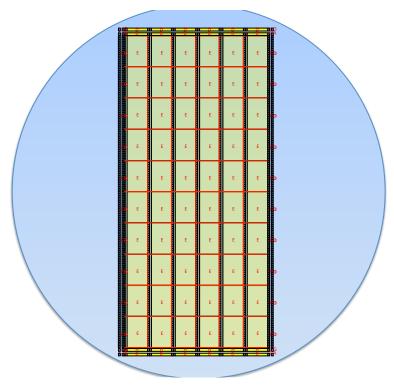

## **MOSS Layout**

### 6.72 Mpixels

### **MOSS - Half Unit**

Test the sub-units independently

Study manufacturing yield

Functional yield at half unit, block, column/row/pixel level granularity

Possible dependence on pixel pitch and layout density?

Study noise, threshold, position resolution vs pixel variants

## Summary

#### **ALICE ITS3**

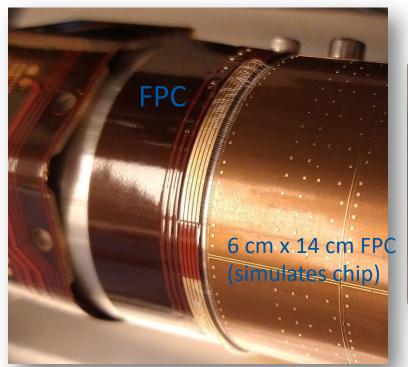

Replace 3 Inner Layers of ITS2 with **wafer scale bent** monolithic pixel sensors Proven operation of thinned sensors **bent at 18 mm** radius Built full scale mechanical prototype

TPSCo 65 nm technology validated for particle sensing Detailed characterization of MLR1 prototypes ongoing

Next: learn stitching with ER1 submission

#### MOSS chip prototype

14 mm × 25.9 mm stitched sensor chip Study yield, power and signal distribution, large pixel arrays

ALICE ITS3 is pioneering large area MAPS sensors and bending.

This is sparking the interest of many groups for other experiments and applications.

# **SPARE SLIDES**

| Pb-Pb Interaction Rate | 50 kHz                                                    |

|------------------------|-----------------------------------------------------------|

| Particle Flux          | 2.2 MHz/cm <sup>2</sup>                                   |

| TID                    | <10 kGy                                                   |

| NIEL                   | 1×10 <sup>13</sup> 1 MeV n <sub>eq</sub> cm <sup>-2</sup> |

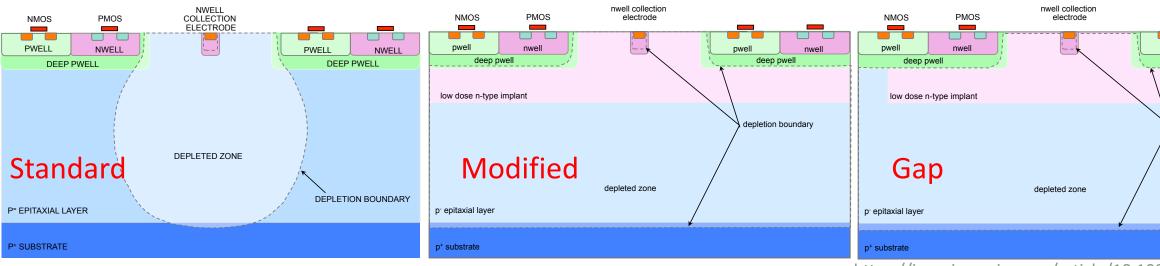

# Reduce Material Budget

### **Process modifications**

Similar optimization as in 180nm, but modifications needed even more in 65 nm for good charge collection.

(180nm)

pwell

deep pwell

depletion boundary

https://doi.org/10.1016/j.nima.2017.07.046

https://iopscience.iop.org/article/10.1088/1748-0221/14/05/C05013 (180nm)

Charge collection speed

Charge sharing

# MOSS Design Challenges

### Stitching

Significant reduction of circuit density

Long-range power distribution and signals transmission

Large number of independent power domains

Leakage currents

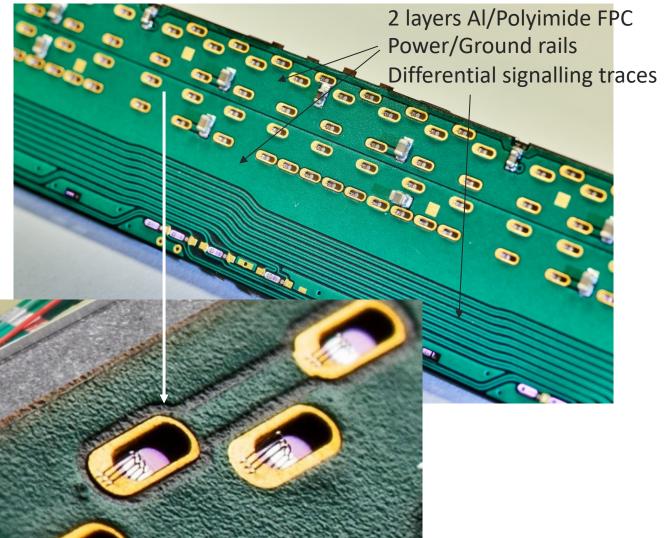

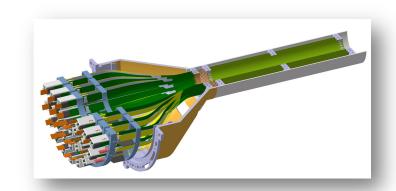

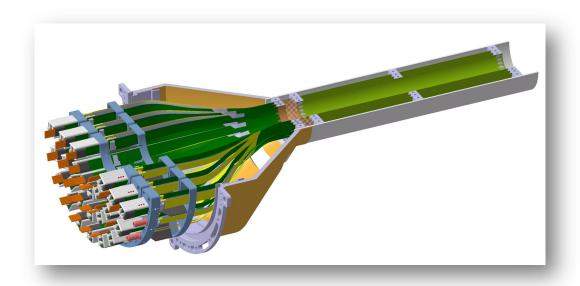

# Development of Interconnects

### Bonding on curved chips and circuits

Procedures, jigs, mandrels, integration with bonding machine

### **ITS2** Inner Barrel Stave