# SPAD Array Chips with Integrated Readout with High Fill Factor and Low Dark Count Rate at Low Temperatures

Michael Keller, Peter Fischer, Institute of Computer Engineering, Heidelberg University

## Abstract

The observation of few optical photons is a common requirement in instrumentation, as the detection of scintillation photons from liquid noble gases in dark matter search experiments. The photon sensors must in particular offer low dark count rate (DCR), high fill factor and good quantum efficiency. Commonly used SiPMs require a single photon sensitive readout for each of many channels. We propose using Single Photon Avalanche Diodes (SPADs) fabricated in a CMOS technology so that the readout circuitry can be integrated and noisy pixels can be disabled. Chips fabricated in an optimized manufacturing process reach a DCR of  $0.04 \,\mathrm{Hz}$  per  $\mathrm{mm}^2$  of active SPAD area at  $160 \,\mathrm{K}$  for typical pixels. In the latest design, the geometric fill factor is above 80% and should still be around 70% after disabling noisy SPADs. The implemented low power readout is fully data driven and provides timestamped hits with a spatial granularity of  $250 \times 200 \ \mu m^2$ . The proposed approach could provide a performant, compact, low power single photon readout for large area detectors

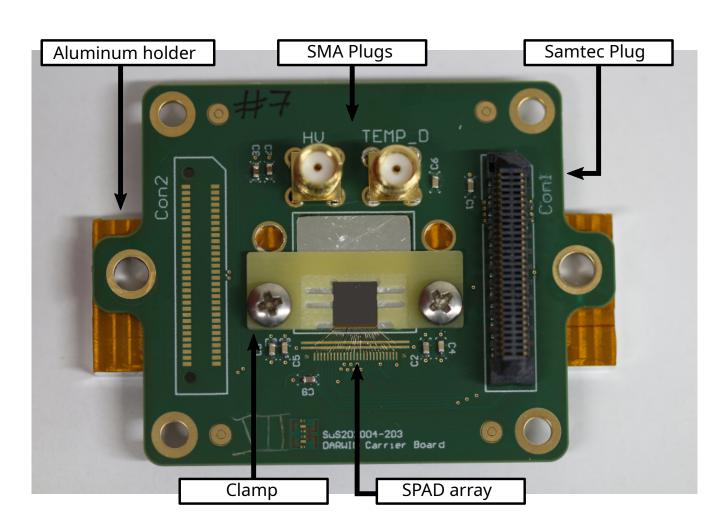

## Test Array

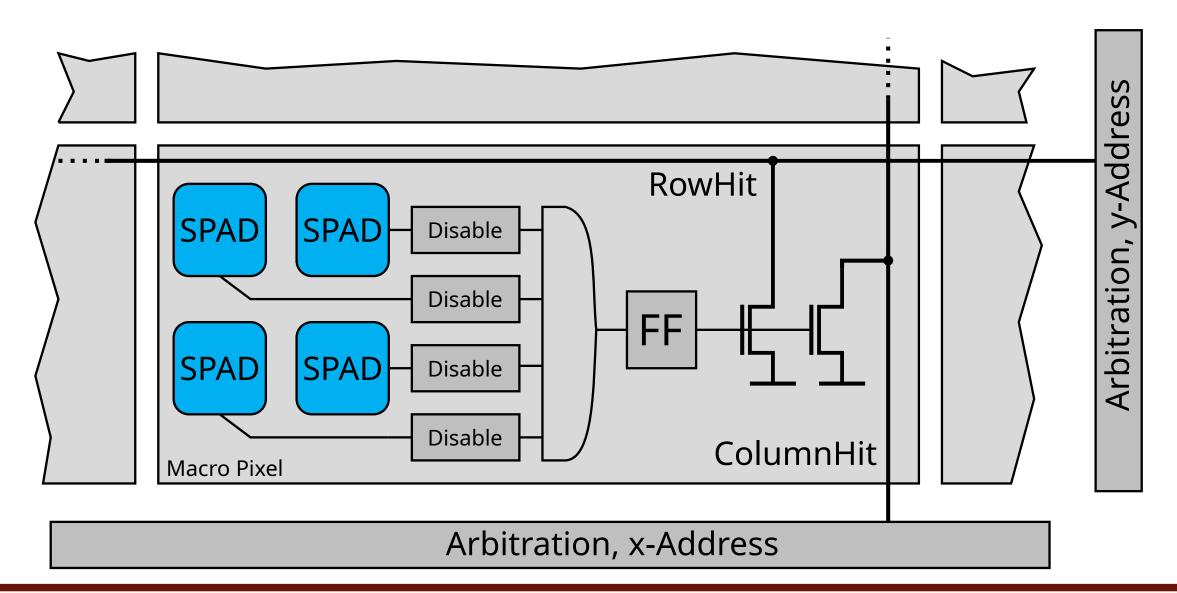

### Macro Pixel:

- High Fill Factor test structure

- Ten SPADs of different geometry to test the DCR as function of size and shape

- Only one readout electronics

- A 1-Bit hit signal is sent to periphery

- Individual SPADs can be switched off

#### **Readout:**

- 2D Array with 19 × 19 Macro Pixels.

- Low-power data driven readout architecture ( $\sim 2 \,\mathrm{m\,W}$ ).

- Hit in Macro Pixel is translated into 10bit x/y address.

- An Error is flagged on coincident hits.

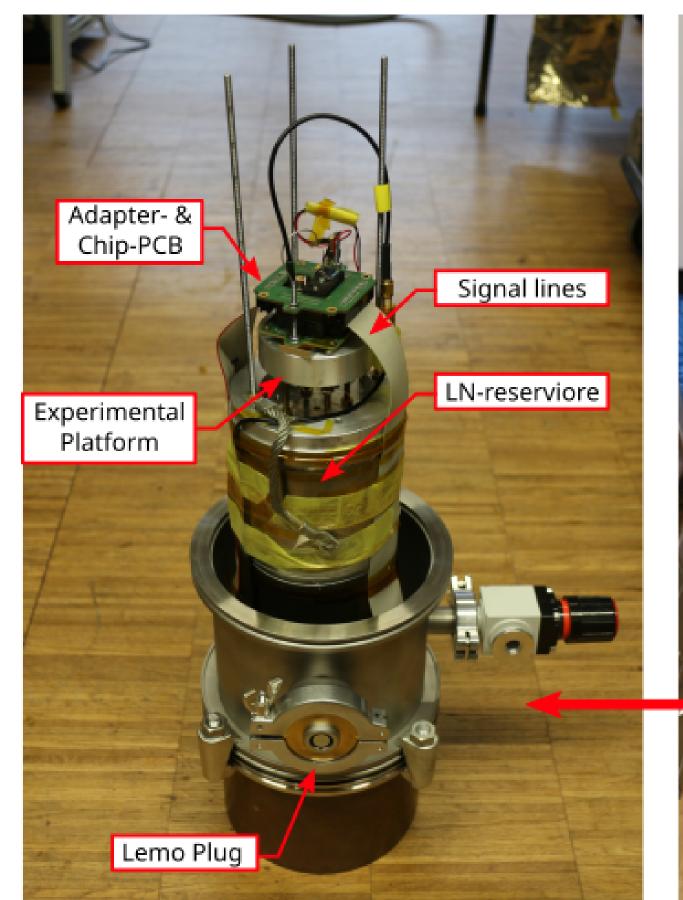

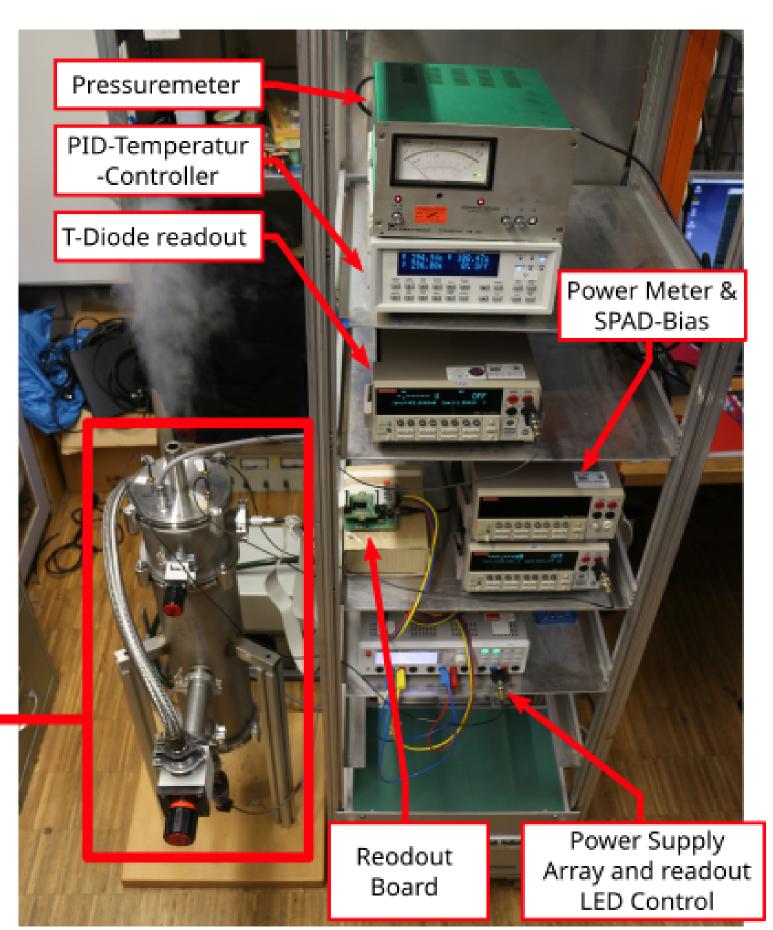

## Cryogenic Measurement Setup

- Vacuum liquid nitrogen cryostat with Temperature range  $100 \, \mathrm{K} < T < 296 \, \mathrm{K}$ .

- Temperature stability  $\Delta T = 0.1 \, \mathrm{K}$

- Fully automated measurement setup.

- Xilinx Artix 7 FPGA for array control

- Fast FTDI USB Interface for fast hit data transmission to computer

- LED mounted on adapter board for illumination

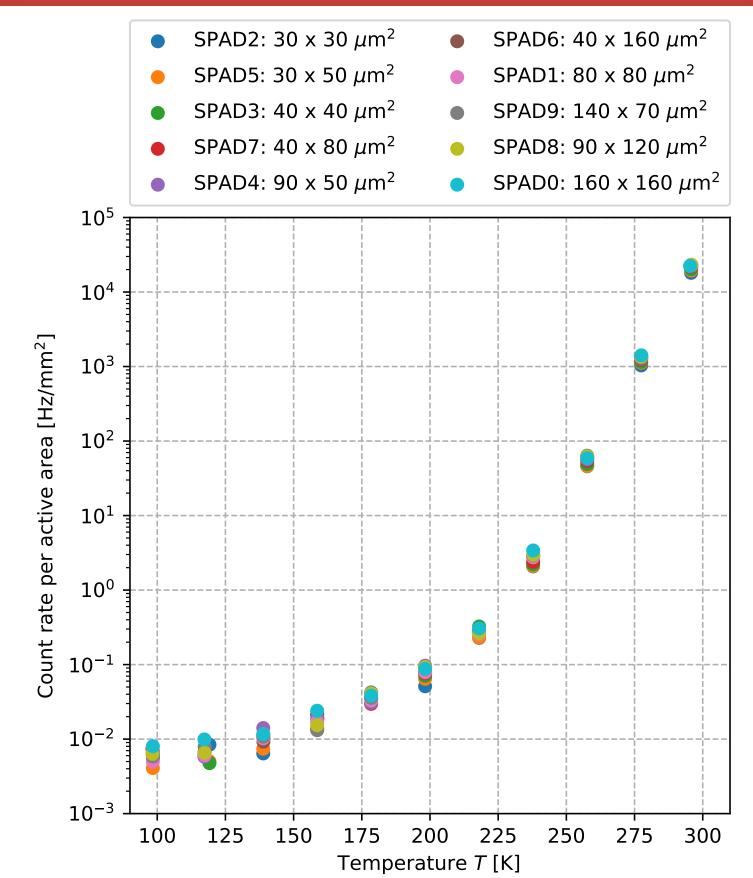

## Dark count rate

- Temperature profile of the DCR measured at  $V_{\rm Ex} = 1 \, \rm V$ .

- Two noise contributions: Thermal generation at high T, tunneling at low T.

- Thermal generation noise is dominated by charge carriers diffusing into the depletion region ( $E_A = 1.05 \,\mathrm{eV}$ ). SRH noise only affects the hot SPADs, which are excluded from the analysis.

- Electric field of the SPADs was modified to reduce the tunneling noise.

- DCR at  $T = 160 \,\mathrm{K}$  is  $0.02 \,\mathrm{Hz}$  per  $\mathrm{mm}^2$ of active area and is independent of the SPAD shape as well as size.

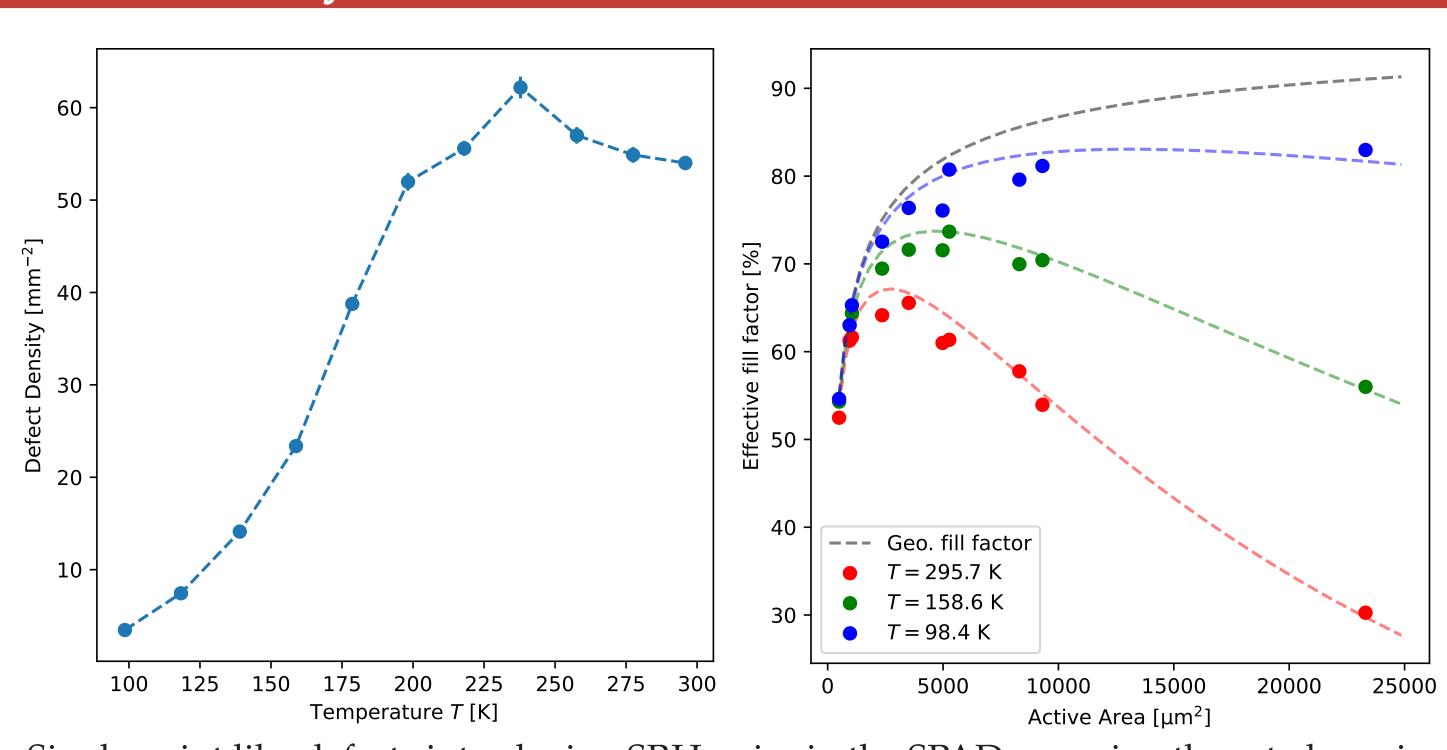

## **Defect Density**

- Single point like defects introducing SRH noise in the SPADs, causing them to be noisy.

- At low T the defect density effectively decrease as SRH falls below tunneling noise level.

- Noisy SPADs are switched off to lower the noise, reducing the active area.

- An optimal SPAD size was found where the effective fill factor after the switch off is highest. It increases with decreasing temperature.

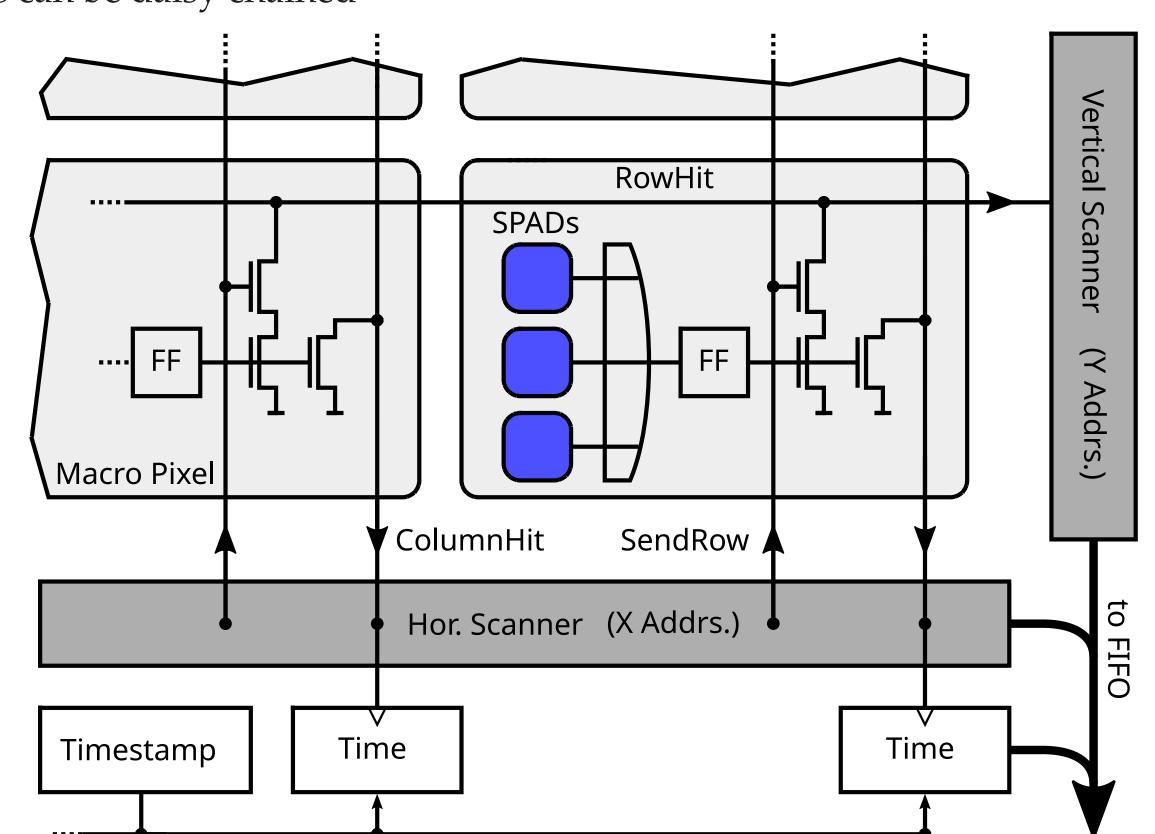

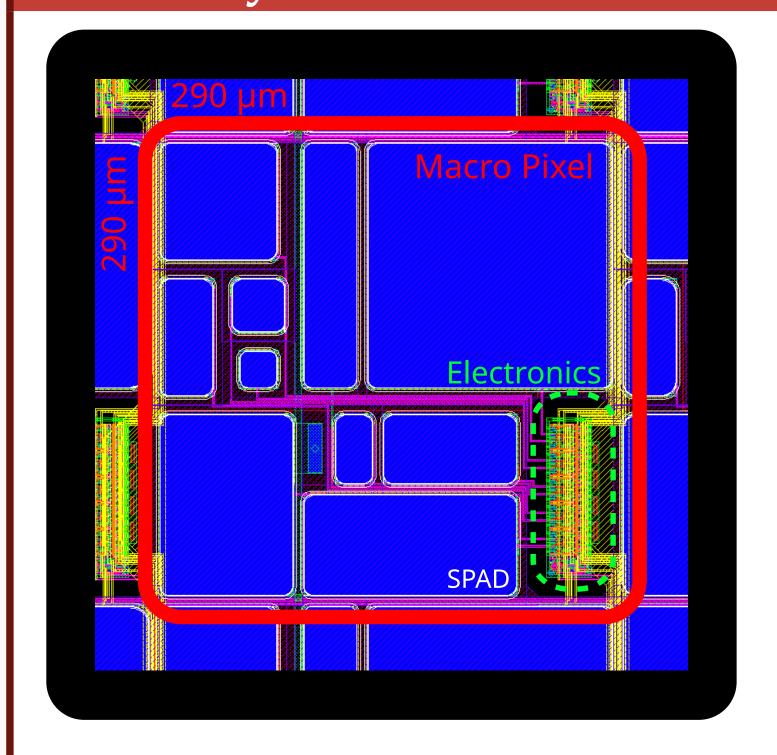

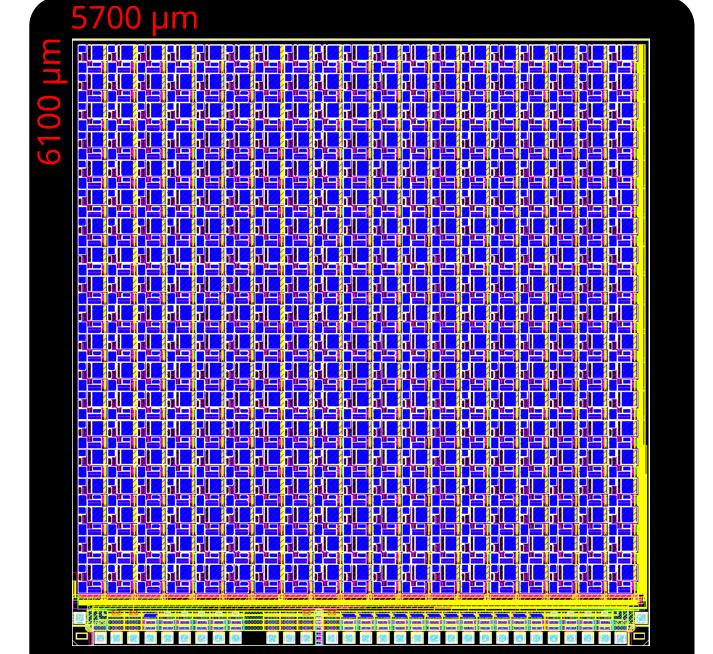

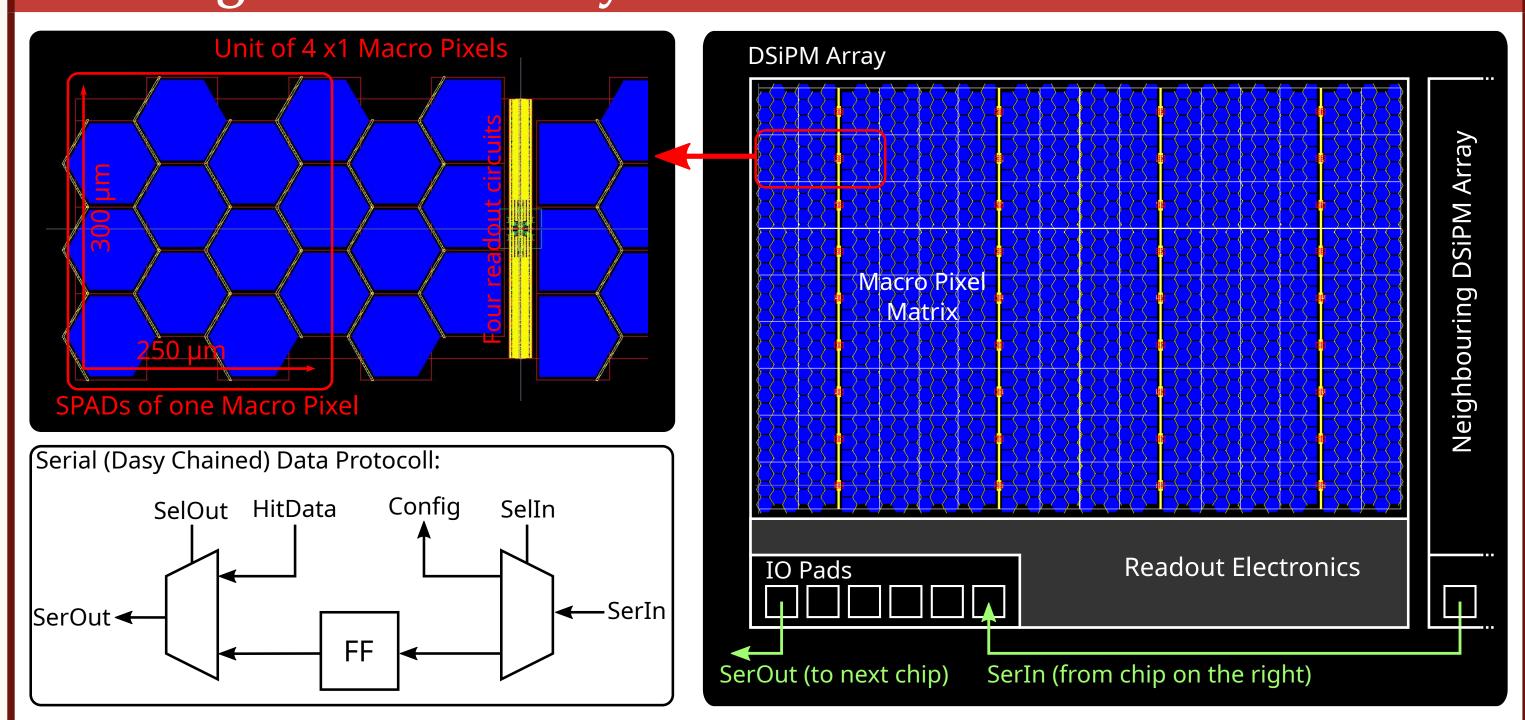

## New Digital SiPM Array

- Focus on low power and high fill factor, with geom. FF  $\approx 80\%$  and eff. FF  $\approx 70\%$

- Data driven readout architecture

- Minimal control interface with serial data protocol for hit and config data

- Arrays can be daisy chained

- Macro Pixel store hit signal, making multiple hits processable

- Asynchronous scan for hits with x/y scanner (one after the other,  $\sim 100 \, \mathrm{ns/hit}$ )

- Column wise time stamp with accuracy of  $\Delta t = 10 \, \mathrm{ns}$