### AR CADIA REPRESENTA

Advanced Readout CMOS Architectures with Depleted Integrated sensor Arrays

# ARCADIA FD-MAPS: simulation, characterization and perspectives for high resolution timing applications

Coralie Neubüser\* on behalf of the ARCADIA collaboration \*INFN-TIFPA, Trento Italy. Email: coralie.neubueser@tifpa.infn.it

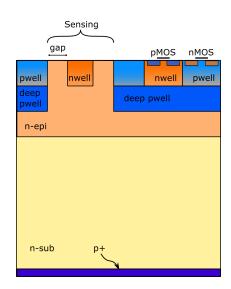

### Fully depleted substrate at low front bias → charge collection via drift

- n-in-n device

- pn-junction on backside

- depletion voltage applied through backside, only low bias voltage from top

- low-resistive epi layer delays the onset punch-through currents

- backside processing (diode + GR) for thick sensors (>  $100\mu m$ )

Main demonstrator (MD1) chip of (1.2×1.2)cm<sup>2</sup> with  $512\times512$  fully depleted monolithic pixels with  $25\mu m$  pitch.

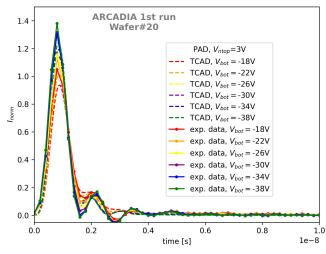

## Focused IR laser, 1GHz bandwidth oscilloscope on $(500 \times 500) \mu \text{m}^2$ pad

- Strong impact of 1GHz oscilloscope, well reproduced in simulation with digital low pass filter

- 95% charge collection in < 1.4ns in  $d_{si}$ =50 $\mu$ m

#### Variety of passive pixel matrices

- Tests of pixels with  $(10/25/50)\mu$ m pitch from different wafers in different thicknesses  $(50/100/200)\mu$ m

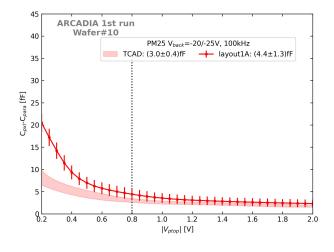

- Capacitance of single pixel of MD1 found < 5fF</li>

#### Ongoing development of MAPS for timing:

- Pad-like MAPs in 50μm pitch for chip implemented in 2nd run

- new large pixels including a charge multiplication layer