## Demonstration System of the HGTD Peripheral Electronics Board (PEB) for ATLAS Phase II Upgrade

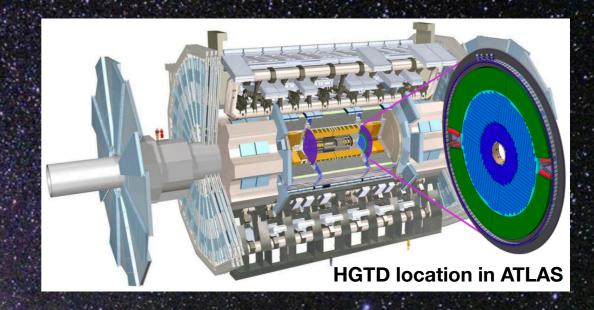

In order to mitigate the pileup effects caused by the increasing instantaneous luminosity of proton-proton collisions at HL-LHC, a High-Granularity Timing Detector (HGTD) has been proposed for the ATLAS Phase-II upgrade.

There will be several types of Peripheral Electronics Boards (PEB), which will be installed in the peripheral regions of the HGTD.

Prior to the PEB prototype, we developed the PEB demonstration system to verify many concerns in advance, such as versatile links, PCB manufacturing techniques, mechanical parameters, key chips, DAQ system, and etc.

The demonstration system consists of:

A set of hardwares, dedicated firmware and lpGBT configuration toolkit

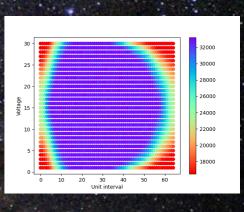

We have tested the system. Basic functions are successfully implemented. And versatile links (uplink @10.24Gbps and downlink@2.56Gbps) are successfully established as well. BERT can be achieved less than 10^-14.