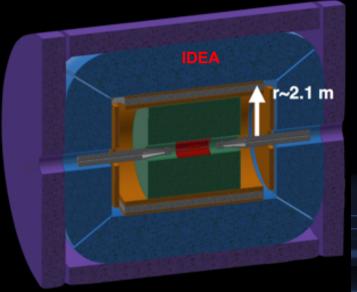

# RD\_FA Pr-2.1m Drift Chamber

F. Grancagnolo N. De Filippis

referees CSN1 11 Marzo, 2020

Super charm/tau Factory at BINP

CMD-3 at VEPP-2000

# Activity #1 2020

Cluster Counting/Timing: data reduction and pre-processing of drift chamber signals sampled at high rate.

Multi-channel version with improved peak finding algorithms.

11/03/2020

# The verified solution for a single channel

The solution consists in transferring, for each hit drift cell, instead of the full spectrum of the signal, only the minimal information relevant to the application of the cluster timing/counting techniques, i.e. the amplitude and the arrival time of each peak associated with each individual ionisation electron.

This is accomplished by using a **FPGA** for the real time analysis of the data generated by the drift chamber and successively digitized by an ADC.

A fast readout algorithm (CluTim) for identifying, in the digitized drift chamber signals, the individual ionization peaks and recording their time and amplitude has been developed as VHDL/Verilog code implemented on a Virtex 6 FPGA, which allows for a maximum input/output clock switching frequency of 710 MHz. The hardware setup includes also a 12-bit monolithic pipeline sampling ADC at conversion rates of up to 2.0 GSPS.

DRIFT CHAMBER

AMPLIFIER

ADC

FPGA

PC

God hipped

CON TO THE CONTROL OF THE CO

G. Chiarello, C. Chiri, G. Cocciolo, A. Corvaglia, F. Grancagnolo, M. Panareo, A. Pepino and G. Tassielli

The Use of FPGA in Drift Chambers for High Energy Physics Experiments

ISBN 978-953-51-3208-0, Print ISBN 978-953-51-3207-3, May 31, 2017, doi:10.5772/66853, http://dx.doi.org/10.5772/66853

AD9625-2.0EBZ Evaluation Board Xilinx ML605 Evaluation Board

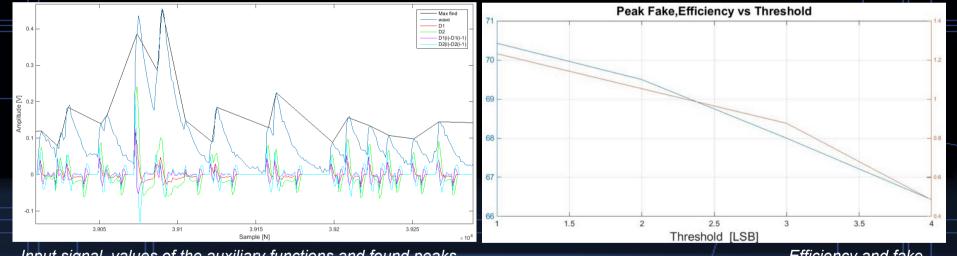

# Example: CluTim algorithm

At the beginning of the signal processing procedure, a counter starts to count, providing the timing information related to the signal under scrutiny. The determination of a peak is done by relating the i-th sampled bin to a number n of preceding bins, where n is related to the rise times of the signal peak. Once a peak is found, it is sent to pipeline memories which are continuously filled as new peaks are found. When a trigger signal occurs at time  $t_0$ , the reading procedure is enabled and only the data relative to the found peaks in the  $[t_0; t_0 + t_{max}]$  time interval are transferred to an external device

Input signal, values of the auxiliary functions and found peaks. rate

Efficiency and fake

# Finanziamento 2019 da CSN1: 2+2 Keuro

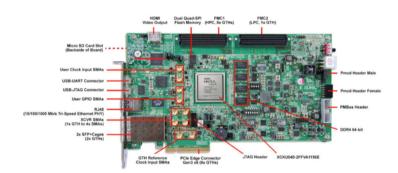

### **KIT EVAL ULTRASCALE FPGA KCU105**

- KINTEX® UltraScale™ XCKU040-2FFVA1156E

- Quadruplo generatore di clock a frequenza fissa Si5335A

- Transceiver 20 GTH

- 2 moduli SFP+ da 10Gbps

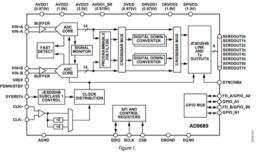

### AD9689 - 2000EBZ

- 14-bit

- Dual channel

- 2.6 GSPS

- JESD204B

- 1,55W at 2,6 GSPS

11/03/2020

## XILINX Xilinx Kintex UltraScale FPGA KCU105 Evaluation Kit

### 14-Bit, 2.0 GSPS/2.6 GSPS, JESD204B, **Dual Analog-to-Digital Converter**

- Onboard JTAG configuration circuitry to enable configuration over USB . JTAG header provided for use

- with Xilinx download cables such as the Platform Cable USB II

- Quad SPI Flash with 2 x 256 Mb of non-volatile storage

- HDMI Video output External Phy/codec device driving an HDMI Connector

- 8x GPIO user LEDs

- · 2GB DDR4 component memory (four [256 Mb x 16] devices) at 1200MHz / 2400Mbpens

- 64MB (512Mb) Quad SPI Flash

- 8Kb IIC EEPROM

- Micro SD Card Slot

- UART To USB Bridge

- 2x SEP / SEP+ cane GTX port (TX, RX) with four SMA

· Gigabit Ethernet GMII. RGMII and

- PCI Express x8 edge connecto

### differential (34 LA & 24 HA) user

defined signals)

• FMC-LPC connector (1 GTX Transceiver, 68 single-ended or 34 differential user defined

· FMC-HPC (Partial Population)

114 single-ended or 57

connector (8 GTX Transceiver

2x PMOD headers

## Data Sheet

0.975 V, 1.9 V, and 2.5 V dc supply operation

### **FEATURES**

JESD204B (Subclass 1) coded serial digital outputs Support for lane rates up to 16 Gbps per lane

- -152 dBFS/Hz at 2.56 GSPS at full-scale voltage = 1.7 V p-p

- -154 dBFS/Hz at 2.56 GSPS at full-scale voltage = 2.0 V p-p

- -154.2 dBFS/Hz at 2.0 GSPS at full-scale voltage = 1.7 V p-p -155.3 dBFS/Hz at 2.0 GSPS at full-scale voltage = 2.0 V p-p 1.55 W total power per channel at 2.56 GSPS (default settings)

SFDR at 2.56 GSPS encode 73 dBFS at 1.8 GHz An at -2.0 dBFS

59 dBFS at 5.53 GHz A<sub>IN</sub> at -2.0 dBFS full-scale voltage = 1.1 V p-p SNR at 2.56 GSPS encode

59.7 dBFS at 1.8 GHz An at -2.0 dBFS 53.0 dBFS at 5.53 GHz A<sub>IN</sub> at -2.0 dBFS

full-scale voltage = 1.1 V p-p SFDR at 2.0 GSPS encode

78 dBFS at 900 MHz A<sub>IN</sub> at -2.0 dBFS 62 dBFS at 5.53 GHz A<sub>IN</sub> at -2.0 dBFS

full-scale voltage = 1.1 V p-p SNR at 2.0 GSPS encode 62.7 dRES at 900 MHz A= at =2.0 dRES

53.1 dBFS at 5.5 GHz Am at -2.0 dBFS full-scale voltage = 1.1 V p-p

9 GHz analog input full power bandwidth (-3 dB) Amplitude detect bits for efficient AGC implementation Programmable FIR filters for analog channel loss equalization 2 integrated, wideband digital processors per channel

48-bit NCO Programmable decimation rates

Phase coherent NCO switching

Up to 4 channels available Serial port control

Supports 100 MHz SPI writes and 50 MHz SPI reads Integer clock with divide by 2 and divide by 4 options Flexible JESD204B lane configurations On-chip dither

### APPLICATIONS

Diversity multiband and multimode digital receivers 3G/4G, TD-SCDMA, W-CDMA, and GSM, LTE, LTE-A Electronic test and measurement systems Phased array radar and electronic warfare DOCSIS 3.0 CMTS upstream receive paths HFC digital reverse path receivers

### **FUNCTIONAL BLOCK DIAGRAM**

12V wall adapter or ATX

- · 8x programmable clocks

- System clocks, EMC clock, user clocks, Jitter attenuated clocks

- · 2x SMA input clocks

### Control & I/O

- 5X Directional Push Buttons

- · 1x Rotary switch

- 4X DIP Switches

- . Diff Pair I/O (1 SMA pair)

# Test da effettuare nel corso del 2020:

- Ímplementazione dell'algoritmo originario di cluster counting/timing sulla nuova FPGA, questo permetterà di migliorare la velocità di trasferimento

- Utilizzo della massima banda di trasmissione dei dati tra ADC multi canale (per adesso 2) e FPGA

- Implementazione di nuovi algoritmi di cluster counting/timing per migliorare l'efficienza e limitare il "fake rate"

- Test dell'algoritmo prima con segnali simulati e successivamente con segnali reali

- su segnali reali si possono anche implementare delle tecniche di filtraggio digitali con le features della nuova FPGA

# SiREAD chip

SiREAD: a low-cost, low power and high density System-on Chip (SoC) capable of analog signal conditioning, fast waveform sampling and integrated readout and signal processing capabilities. The SiREAD device will also have calibration and monitoring circuitry in addition to a deep sampling buffer making it suitable for large HEP experiments. Design and development of the advanced SiREAD chip is built by integrating into one SoC analog signal conditioning circuits and bias monitoring and digital readout and signal processing block capabilities (triggering, sparsification and data reduction).

Synergies: MaPMT Readout for EIC R&D

Photograph of the 64 channel SiREAD based (2x SiREAD rev.1) readout card as a building block for the 256 MA-PMT readout.

Photograph of the first generation of 256-anode 2" PMT readout for use with mRICH prototype in the Fermilab beam test facility.

## Nalu Scientific SBIR Project: ASoC

Compact, high performance waveform digitizer

| Parameter               | Spec (measured) |  |  |  |  |  |  |

|-------------------------|-----------------|--|--|--|--|--|--|

| Sample rate             | 2.4-3.2GSa/s    |  |  |  |  |  |  |

| Number of Channels      | 4               |  |  |  |  |  |  |

| Sampling Depth          | 16kSa/channel   |  |  |  |  |  |  |

| Signal Range            | 0-2.5V          |  |  |  |  |  |  |

| Resolution              | 12 bits*        |  |  |  |  |  |  |

| Supply Voltage          | 2.5V            |  |  |  |  |  |  |

| RMS noise               | ~1 mV           |  |  |  |  |  |  |

| Digital Clock frequency | 25MHz           |  |  |  |  |  |  |

| Timing resolution       | <25ps**         |  |  |  |  |  |  |

| Power                   | 140mW/channel   |  |  |  |  |  |  |

| Analog Bandwidth        | 950MHz          |  |  |  |  |  |  |

### **Key Contribution:**

- · High performance digitizer: 3+ Gsa/s

- · Highly integrated

- Commercially available

- · 5mm x 5mm die size

Very low cost to prototype and mass produce

All chips, are designed with commercial grade tools and licenses and can be sold once commercialized.

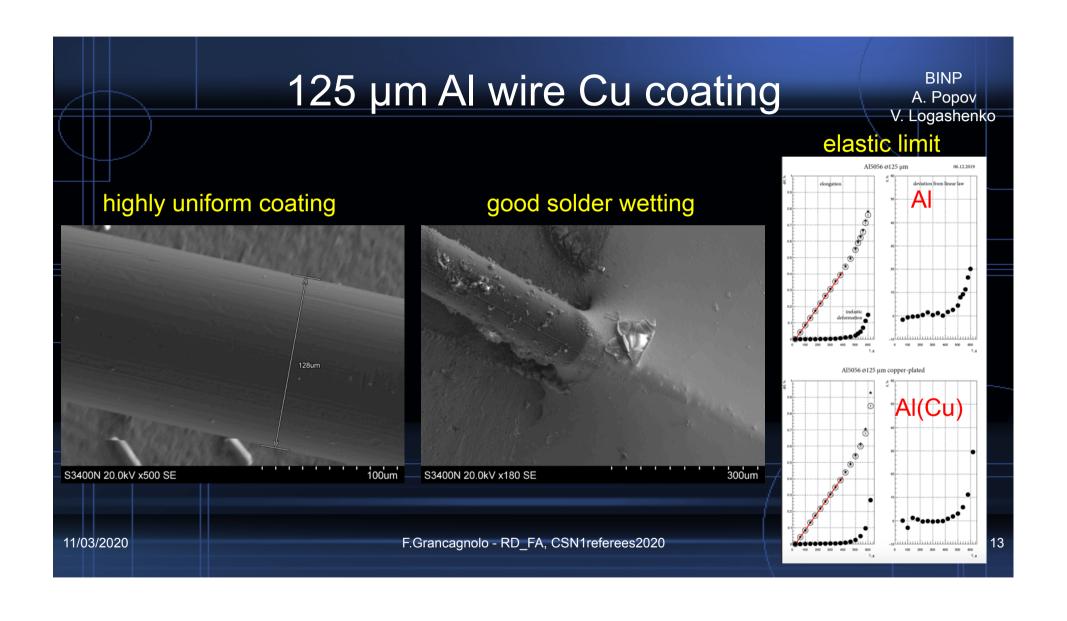

New wire materials for ultra-light drift chambers at the next generation of lepton colliders

11/03/2020

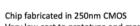

# C wire metal coating

BINP A. Popov V. Logashenko

# **HiPIMS: High-power impulse magnetron sputtering**

physical vapor deposition (PVD) of thin films based on magnetron sputter deposition (extremely high power densities of the order of kW/cm² in short pulses of tens of microseconds at low duty cycle <10%)

# Wire metal coating: BINP proposal

BINP A. Popov V. Logashenko

11/03/2020

F.Grancagnolo - RD\_FA, CSN1referees2020

11

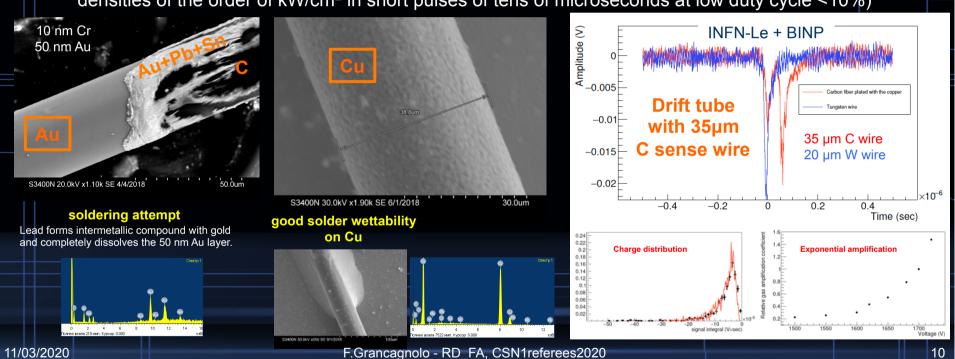

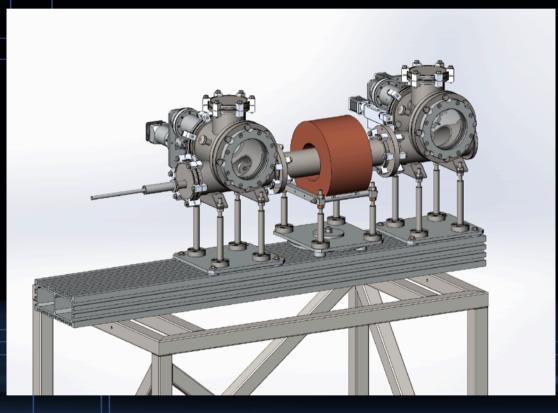

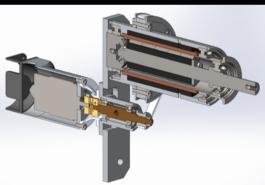

Wire metal coating: BINP real setup

11/03/2020

F.Grancagnolo - RD\_FA, CSN1referees2020

BINP

# Test da effettuare nel corso del 2020:

- Acquisto monofilamento di Carbonio su opportuna spoletta

- Procuramento di fili polimerici per studi di deposizione di rame

- Test di deposizione di metalli saldabili su polimeri, C, Al, Ti

- Test di saldatura con laser ad IR

- Test di incollaggio con colle conduttive

- Realizzazione di camerette di prova con diversi catodi per studi di ageing

- Realizzazione di un setup a Bari per condivisione test su camerette di prova

Integration in full GEANT4 simulation of drift chamber including track finding and fitting in collaboration with BINP

11/03/2020

# Activity #4 2020

Participation in WP5 of CREMLINplus

"Joint Technology Development around

SCT and Future Lepton Colliders"

Task 5.5

"Development and Design of Central Tracker for the SCT Detector"

11/03/2020

# CREMLIN P. LUS

Connecting Russian and European Measures for Large-scale Research Infrastructures

### **CREMLINplus Kick-off Workshop**

19-20 February 2020 DESY, Notkestrasse 85, 22607 Hamburg

### **Facts about CREMLINplus**

A European-Russian flagship project

- Funded under EU's Research and innovation Programme Horizon 2020

- EU's Flagship project in the EU-Russian cooperation in the domain of RI

- CEMLINplus is a Research and Innovation Action (RIA), following INFRASUPP-01-2018-2019

- Project duration: 4 years, 01.02.2020-31.01.2024

- · Budget: 25 million EUR

- Consortium: 35 partners

- · Building on "First CREMLIN Recommendations"

Collaboration with NICA

Collaboration with PIK

Collaboration with USSR

Joint technology development around SCT and future lepton colliders

Joint technology development around XCELS

Joint development of detector technologies

Access to Russian RI

Staff exchange and training for RI management

Joint long-term sustainability of RIs

Coordinator: DESY

# FAIR & JINR INR RAS; MEPH; EKUT; NPI CAS; Wigner RCP; WUT

<u>FZJ</u> & NRC KI-PNPI JINR; PTI; SPSU; HZG; TUM; CEA-LLB; ILL; UCA; MTA EK; UNIMIB: ESS

> NRC KI & ESRF DESY; European XF L; INFN

BINP & CERN

JLU; CNRS-Lu ; INFN

IAP & CEA-LIDYL

ELI-DC AISBL; Laserlab-Europe AISBL

FAIR & JINR

DESY; BINP; NRC KI-PNPI; GUF; CNRS-IPHC; UNIMIB; CERN;

ESS; INR NASU

ICISTE & DESY NRC KI; NUST MISIS

UNIMIB & NUST MISIS

DESY

NRC KI & DESY

### 5 Russian megascience projects

- NICA: Superconducting accelerator complex ("Nuclotron-based ion collider facility");

- PIK: High-flux research reactor (International Centre for Neutron Research, ICNR);

Gatchina

- USSR: Ultima Synchrotron Storage Ring; Protvino

- SCT: Lepton Collider "Super Charm-Tau Factory"; Novosibirsk

- XCELS: High power laser "Exawatt Center for Extreme Light Studies"; Nizhniy Novgorod

# WP5 Joint technology development around SCT and future lepton colliders

- Consortium BINP & CERN (coordinating partners);

and JLU; CNRS\_LAL; INFN

- Budget 2.19 MEUR

- Objectives:

- support and develop EU and Russian scientific cooperation in the SCT project

- make an example of good practice on establishing collaboration around Russian RI with extensive participation of EU institutions

- support joint EU Russian efforts on development of future lepton colliders

- increase visibility of SCT project in EU and world-wide scientific and decision-makers communities

11/

17

### **CREMLINplus Kick-off Workshop**

19-20 February 2020 DESY. Notkestrasse 85, 22607 Hamburg

# WP5: Joint technology development around SCT and future lepton colliders

Vitaly Vorobyev for the WP5 partners

### **WP5 Tasks**

- 1. Fostering internationalization and visibility of the SCT project, support of outreach activities related to SCT

- 2. Development of collider technologies and fostering synergy between SCT, CLIC, and FCC-ee collider projects

- Development of software for the design of an SCT detector

- Development and design of Inner Tracker for the SCT detector

- Development and design of Central Tracker for the SCT detector

- Development and design of Particle Identification system for the SCT detector

### Development and design of Inner Tracker for the SCT detector

- > Three options for the SCT inner tracker

- Si strips

- o Robust technology, but not optimized for lowmomentum tracks

- 2. Cylindrical μ-RWELL (INFN LNF & Ferrara)

- o Low material

- Spatial resolution better than 60 μm

- o Time resolution ~5.7 ns

- 3. TPC (BINP)

- o Best capability for low-momentum track detection

- But challenging readout and reconstruction

D5.4 M24. Status report on R&D work on Inner Tracker for the SCT detector D5.5 M44. Final report on R&D work on Inner Tracker for the SCT detector

Milestone. M42. Prototype for the SCT inner tracker based on the C-RWELL or Compact TPC

### Development and design of Central Tracker Task 5.5 for the SCT detector

- An ultra-low mass Tracking Chamber with Particle Identification capabilities (TraPld) concept (INFN Lecce)

- Low material

- Improved identification with cluster

- Synergy with MEG2 DC and the IDEA DC project for FCC-ee and CEPC

- New drift chamber for the CMD3 detector as a prototype for the SCT central tracker

D5.6 M24. Status report on R&D work on Central Tracker for the SCT detector D5.7 M44. Final report on R&D work on Central Tracker for the SCT detector Milestone, M42, Prototype for the SCT central chamber

11/03/2020

11/03/2020

**CREMLINplus Kick-off Workshop**

19-20 February 2020 DESY, Notkestrasse 85, 22607 Hamburg

19

| Task                                                                                                                                                                                                                                                   | Subtask                                                    | Subtask leader                         | М1 | M2 | МЗ | M4 | M5 | М6 | М7 | М8 | М9 | M10 | M11 | M12 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------|----|----|----|----|----|----|----|----|----|-----|-----|-----|

| 5.1. Internationalization                                                                                                                                                                                                                              | Vitaly Vorobyev                                            |                                        |    |    |    |    |    |    |    |    |    |     |     |     |

| and visibility                                                                                                                                                                                                                                         | Workshop on future SCT factories                           | Vitaly Vorobyev                        |    |    |    |    |    |    |    |    |    |     |     |     |

| and violonity                                                                                                                                                                                                                                          | Public SCT webpage development                             | TBD                                    |    |    |    |    |    |    |    |    |    |     |     |     |

| 5.2. Collider technologies                                                                                                                                                                                                                             | TBD                                                        |                                        |    |    |    |    |    |    |    |    |    |     |     |     |

| Full detector geomentry in DD4Hep (barrel)  Full detector geomentry in DD4Hep  5.3. SCT detector software  Simplified reconstruction algorithm for each subsystem  Full simulation and reconstruction of TP as inner tracker  CVMFS repository at CERN |                                                            | Andrey Sukharev                        |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        | Full detector geomentry in DD4Hep                          | Andrey Sukharev                        |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        |                                                            | Andrey Sukharev                        |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        | Full simulation and reconstruction of TPC as inner tracker | Andre Sailer                           |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        | CVMFS repository at CERN                                   | Andre Sailer                           |    |    |    |    |    |    |    |    |    |     |     |     |

| Technical Design of TPC                                                                                                                                                                                                                                | Technical Design of TPC prototype                          | Lev Shekhtman                          |    |    |    |    |    |    |    |    |    |     |     |     |

| 5.4. Inner tracker                                                                                                                                                                                                                                     | tracker Technical design of cylindrical muRWELL prototype  | Giovanni Benchivenni                   |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        | Conceptual design of the prototype                         | Franco Grancagnolo                     |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        | Mechanical design of the prototype                         | Alessandro Miccoli,<br>Alexander Popov |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        | Simulation of the prototype                                | Fedor Ignatov                          |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        | Study of the wire properties                               | Alexander Popov                        |    |    |    |    |    |    |    |    |    |     |     |     |

| PID requirements for endcup and barrel from physics  Optimized conceptual design of the PID system  Prototyping FARICH option (full ring detect)  Prototyping FDIRC option with SiPM readout (?)  Beam tests of existing prototypes (both options) (?) |                                                            |                                        |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        | Michael Dueren                                             |                                        |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        | Alexander Barnyakov                                        |                                        |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        | Michael Dueren                                             |                                        |    |    |    |    |    |    |    |    |    |     |     |     |

|                                                                                                                                                                                                                                                        |                                                            | Alexander Barnyakov                    |    |    |    |    |    |    |    |    |    |     |     |     |