# FATIC characterization (FAst Timing Integrated Circuit)

Federica Simone, Piet Verwilligen, Francesco Licciulli, Giuseppe De Robertis University of Bari & INFN Bari

Istituto Nazionale di Fisica Nucleare

UNIVERSITÀ

DEGLI STUDI DI BARI

DO MORO

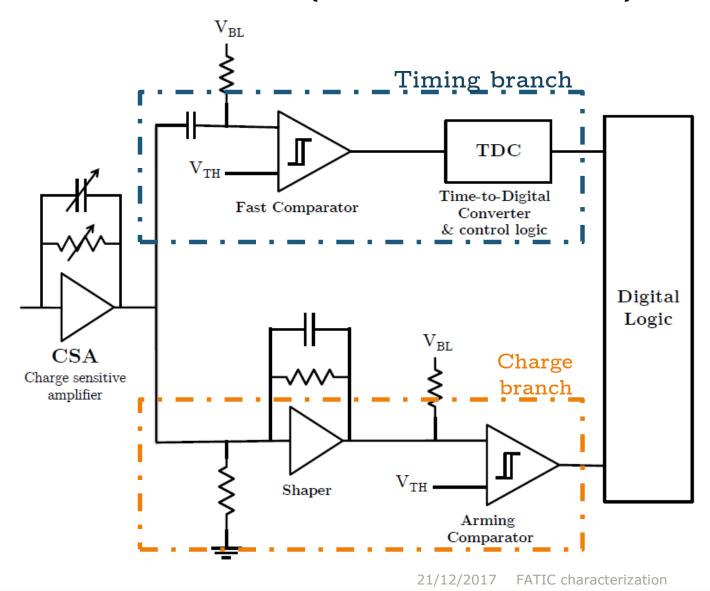

## Schematic (single channel)

| CSA                                                            |                                   | TDC               |                            |

|----------------------------------------------------------------|-----------------------------------|-------------------|----------------------------|

| Peaking time*                                                  | 7.3 ns                            | Resolution        | 5-bit fine / 16-bit coarse |

| Time jitter*                                                   | 300 ps @ 1 fC input charge        | Reference Clock   | 320 MHz                    |

| ENC*                                                           | $18.2e^{-*Cin} (pF) + 235.5e^{-}$ | Time resolution   | 100 ps                     |

| Current Cunsuption*                                            | 1.3 mA                            | Shaper            |                            |

| Signal Polarity                                                | positive & negative               | Peaking time      | 100 ns                     |

| Gain                                                           | High gain mode: $50 \text{mV/fC}$ | Fast Comparator   |                            |

|                                                                | Low gain mode: $10 \text{ mV/fC}$ | Threshold         | [0 - 76.5]ke-, step 300e-  |

| *simulation in high gain mode w/ $\mathrm{Cin}=15~\mathrm{pF}$ |                                   | Arming Comparator |                            |

|                                                                |                                   | Threshold         | [0 - 58.65]ke-, step 230e- |

Table 1.1: FATIC features

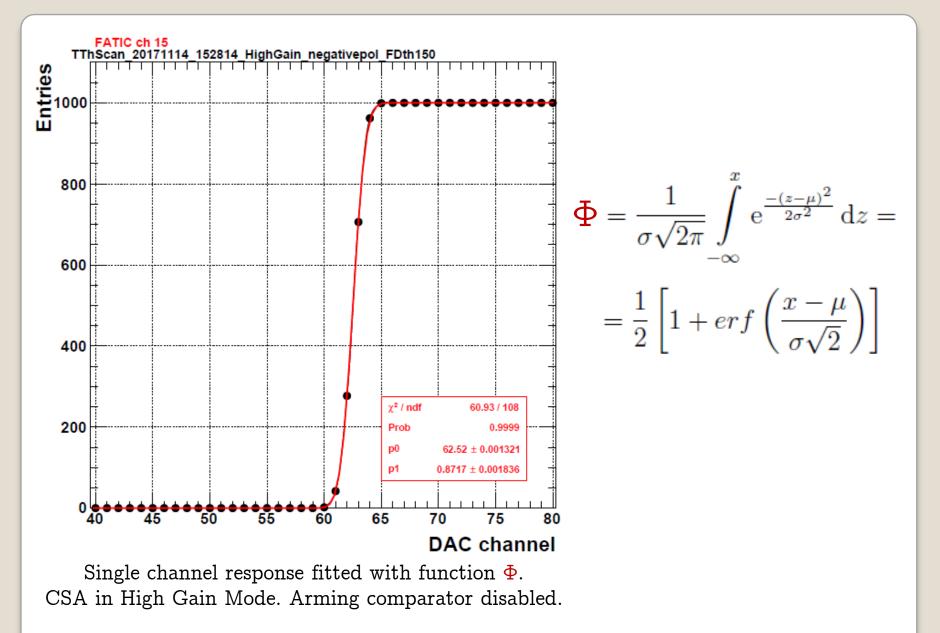

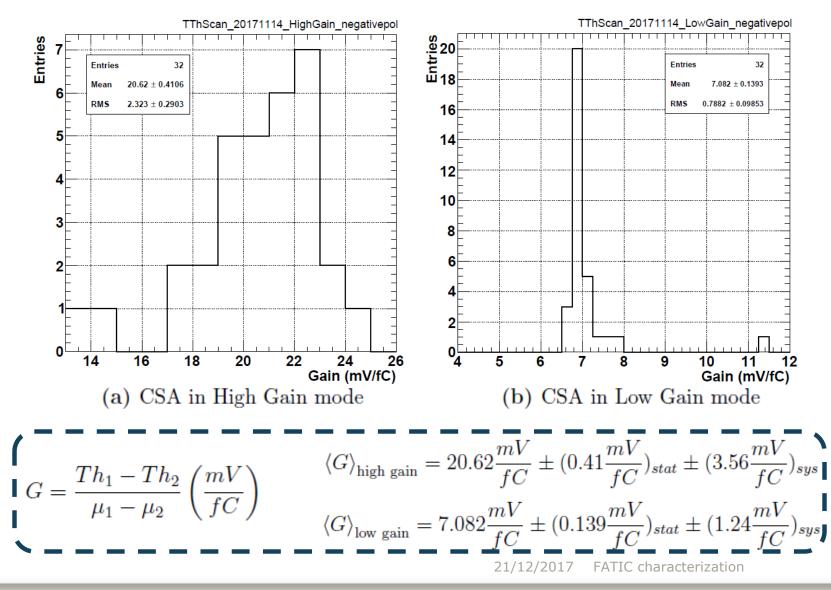

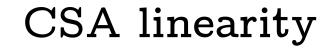

#### CSA Gain

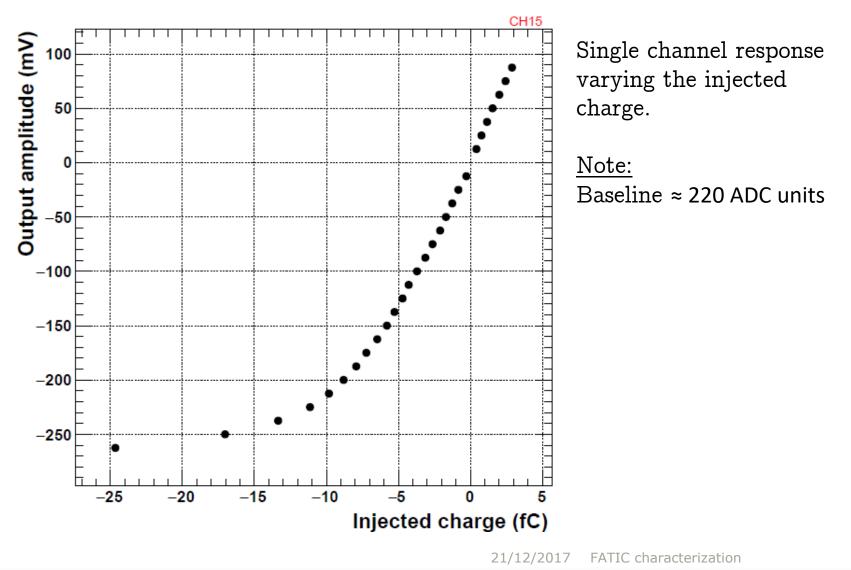

#### Arming comparator

$$\begin{split} \sigma_{\text{timing}} &= 1.026 \pm 0.045\\ \sigma_{\text{arming}} &= 0.841 \pm 0.032 \end{split}$$

% ENC<sub>reduction</sub> = [ $\sigma_{\text{timing}} - \sigma_{\text{arming}}$ ] /  $\sigma_{\text{timing}} \approx 18\%$

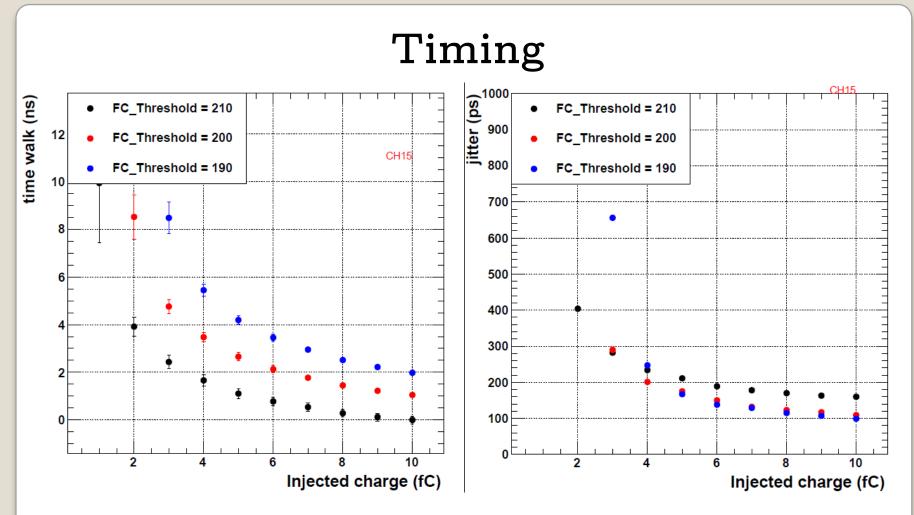

- Input trigger and the fast-OR signal sent to the scope

- Average delay = time walk

- Delay std deviation = time jitter

### Upgrade ideas for FATIC v.2

- Internal circuit for threshold matching

- Investigate CSA gain (lower than expected)

- Symmetric dynamic for positive and negative signals