### STATUS OF FAST TRACKER (FTK) AND FUTURE HARDWARE TRACKER FOR THE TRIGGER (HTT)

Alberto Stabile

## STATE-OF-THE-ART: THE FTK SYSTEM

### The whole FastTraKer (FTK) system stores one billion (10<sup>9</sup>) patterns

- 8 Mpatterns per board (128 boards)

- 128 kpatterns per chip (64 AM chips / board)

- A pattern is composed by 18 bits × 8 words

#### Pixels Major concerns: & SCT FTK \*\*\*\* Data high pattern density RODs Formatter Iarge silicon area Cluster Core Crate I/O signal congestion at board $45^{\circ}+10^{\circ}$ in $\phi$ $8\eta$ - $\phi$ towers DO DC Finding AM AM 2 PU / tower level (solution: 2 Gbit/s serial TF 100 kHz links) Event HW НW PU PU Rate Maximum power limited by ΔIJΧ cooling (because we are fitting SSB (Second Stage Fit) 8192 AMchips in 8 VME crates): Track Data 250 W per AM board FLIC ROB Raw Data ≩ FTK ROBs झHLT <sup>1</sup>A. Andreani et al., $\$ AMchip04 and the processing unit ROBs ►Processing prototype for the FastTracker," IOP J. Instr. 7 (2012) C08007

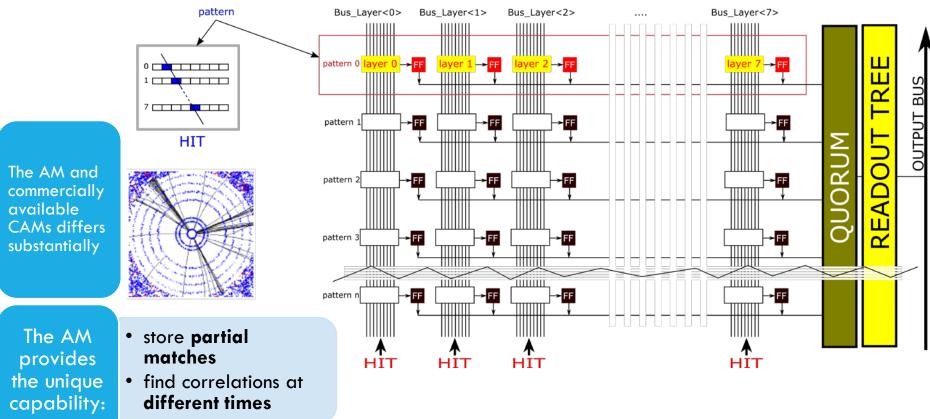

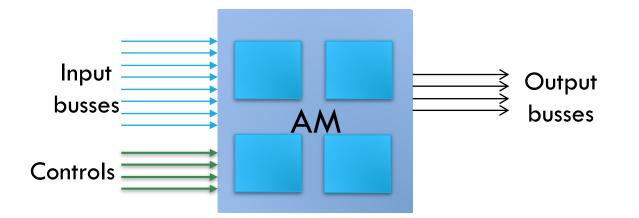

## THE AM CHIP ARCHITECTURE

For each bus and for each pattern there is a small **CAM cell array (layer x)**

- It compares its own content with all data received. If it matches a memory is set (FF)

- The partial matches are analyzed by Quorum logic the and compared to the desired threshold

- A readout encoder (Fischer Tree) reads the matched patterns in order

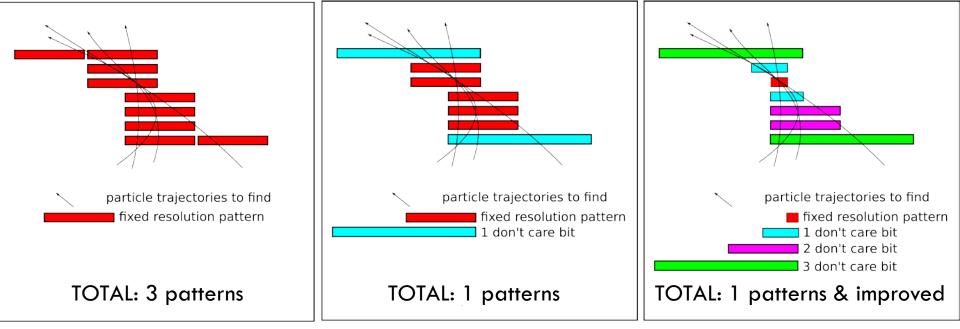

## VARIABLE RESOLUTION

Smart approach: consists in performing pattern matching at reduced and variable resolution first, and then to refine matching resolution using a FPGA.

• A "don't care" bit is used to increase the pattern recognition efficiency at different resolutions.

#### At high efficiency: number of fakes, required patterns, and power consumption decrease.

23/11/2017

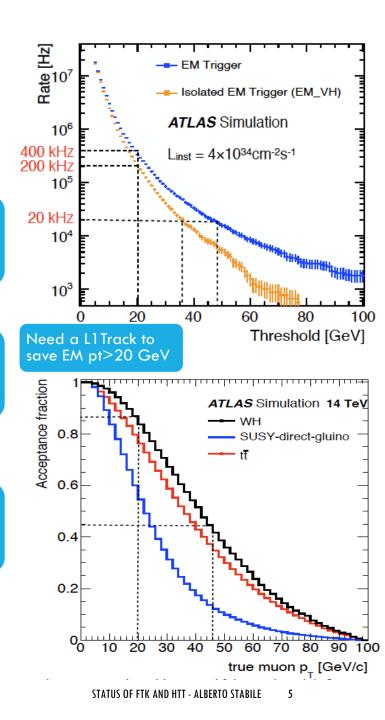

## HL-LHC REQUIREMENTS

# Big challenges from phase-Il conditions

• Pileup 140 (max 200)

Track Triggers are a crucial piece of the phase-II upgrade plan

- ATLAS: L1Track and L2 upgrade

- CMS: L1Track Trigger is the baseline

## Goal: evolve the system design to phase-II environment

- AM chip R&D

- Fully exploit ATCA potentialities

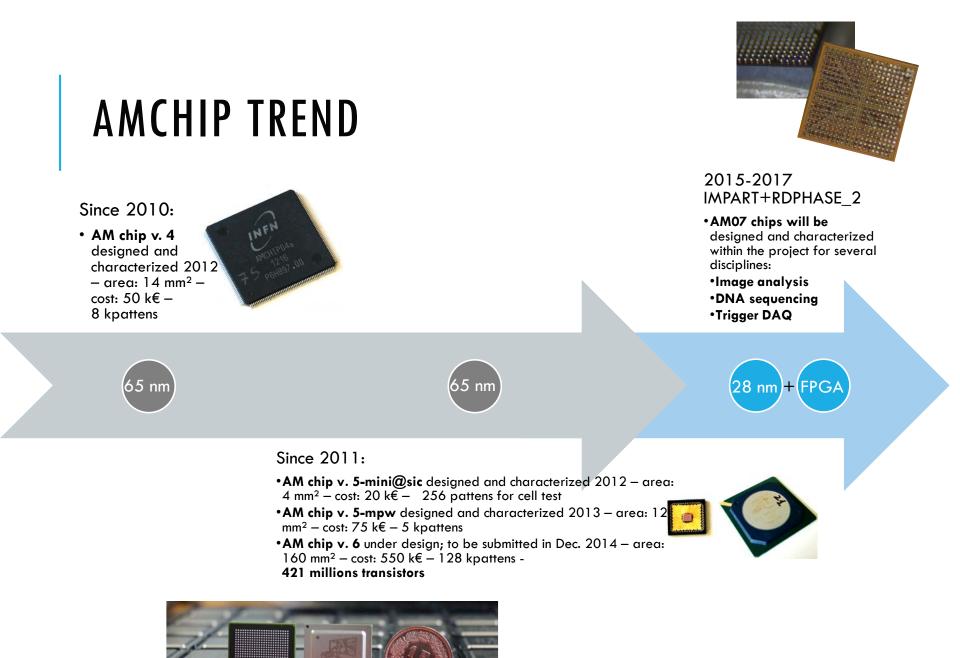

## AMCHIP DESIGN COMPLEXITY VS CPUS

| Chip name                                 | Transistor count | Year | Brand  | Technology | Area                |

|-------------------------------------------|------------------|------|--------|------------|---------------------|

| <u>Core 2 Duo</u> Conroe                  | 291,000,000      | 2006 | Intel  | 65 nm      | 143 mm <sup>2</sup> |

| <u>Itanium 2</u> Madison 6M               | 410,000,000      | 2003 | Intel  | 130 nm     | 374 mm <sup>2</sup> |

| <u>Core 2 Duo</u> Wolfdale                | 411,000,000      | 2007 | Intel  | 45 nm      | 107 mm <sup>2</sup> |

| AM06                                      | 421,000,000      | 2014 | AMteam | 65 nm      | 168 mm <sup>2</sup> |

| <u>Itanium 2</u> with 9 <u>MB</u> cache   | 592,000,000      | 2004 | Intel  | 130 nm     | 432 mm <sup>2</sup> |

| <u>Core i7</u> (Quad)                     | 731,000,000      | 2008 | Intel  | 45 nm      | 263 mm <sup>2</sup> |

| Quad-core <u>z196<sup>[20]</sup></u>      | 1,400,000,000    | 2010 | IBM    | 45 nm      | 512 mm <sup>2</sup> |

| Quad-core + GPU <u>Core i7 lvy Bridge</u> | 1,400,000,000    | 2012 | Intel  | 22 nm      | 160 mm <sup>2</sup> |

| Quad-core + GPU <u>Core i7 Haswell</u>    | 1,400,000,000    | 2014 | Intel  | 22 nm      | 177 mm²             |

| AM09                                      | 1,684,000,000    | 2019 | AMteam | 28 nm      | 150 mm²             |

| Dual-core <u>Itanium 2</u>                | 1,700,000,000    | 2006 | Intel  | 90 nm      | 596 mm²             |

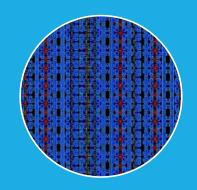

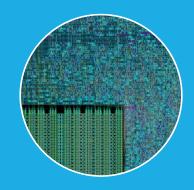

### **DESIGN METHODOLOGY**

More repetitive parts have been design "by hand" with a full custom approach

More complex logics have been design with automatic tools based on standard cells (synthesis, place & route)

MIXED APPROACH

organistika (tempo en la constructiva en la constructiva en la constructiva en la constructiva en la constructi La constructiva en la constructiva e

|   | 41081 0 1000 00 00 00 00 00 00 00 00 00 00 0 |  |

|---|----------------------------------------------|--|

|   |                                              |  |

|   |                                              |  |

|   | 이 아이는 지수는 것으로는 것으로 두 두 두 두                   |  |

|   | 김 않은 것은 것은 것 같은 것 같은 것                       |  |

| 객 |                                              |  |

|   |                                              |  |

|   |                                              |  |

|   |                                              |  |

|   |                                              |  |

|   |                                              |  |

|   |                                              |  |

|   |                                              |  |

|   |                                              |  |

|   |                                              |  |

|   |                                              |  |

### Standard cells

### Full custom

### More complex logics

More repetitive

parts

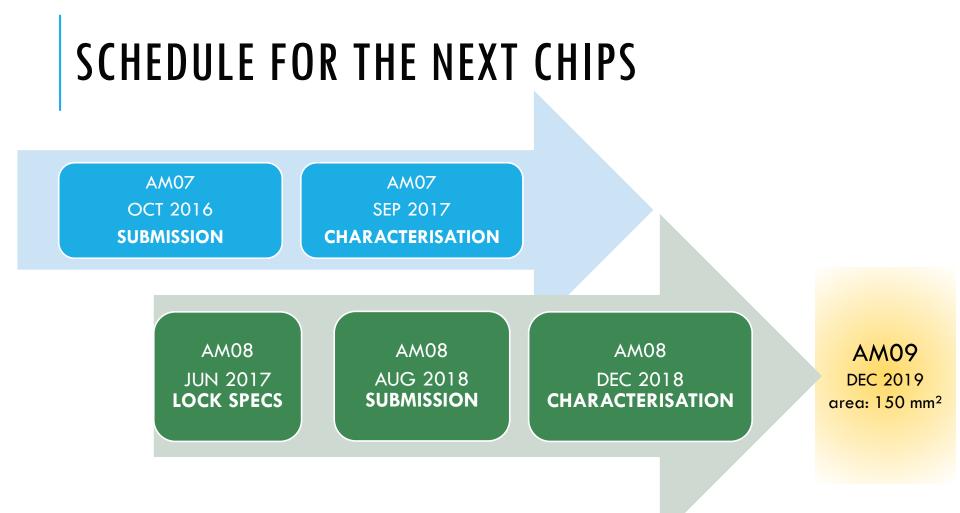

### AM09 COMPLEXITY

AM09 will be one of the most complex chips designed within CERN collaboration

### Comparison rate:

about 30 peta comparisons per second per chip

### **MULTI-CORE ARCHITECTURE**

### Chip will be composed by few cores

#### Outputs could be merged or independed

• Choice depending on required output bandwith

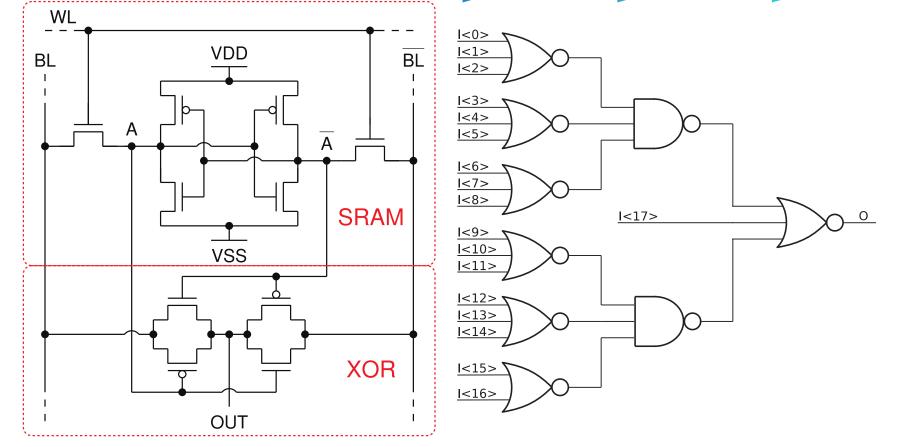

Based on the previous 65 nm XORAM cell Based on the XOR boolean function, instead of the NAND and NOR functions

Is made of a 6T SRAM cell connected to a 6T-XOR gate

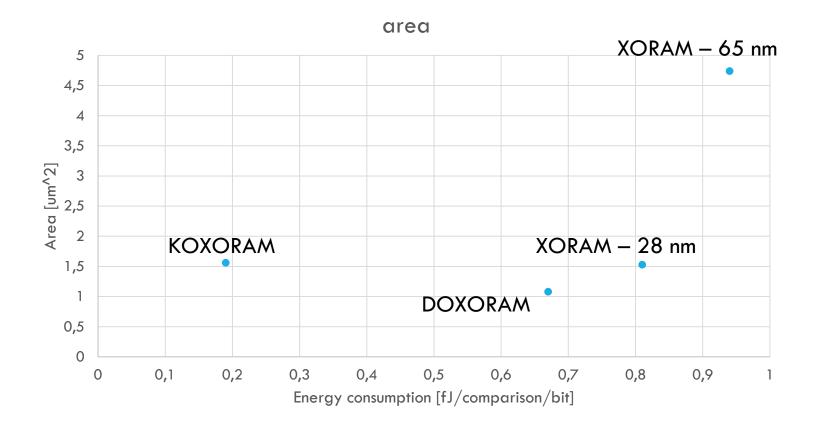

### NEW OPTIMIZED CELLS

With similar power save methods we designed two new cell tech:

Italian Patent: A. Annovi, L. Frontini, V. Liberali, A. Stabile, "MEMORIA CAM", UA2016A005430

> In this week INFN will decide for the internationalization

### **FULL CUSTOM CELL:** ENERGY CONSUMPTION VS AREA