PAUL SCHERRER INSTITUT

# A low mass pixel detector upgrade for CMS

Hans-Christian Kästli, PSI

RD09 Conference September 30 - October 2, 2009 Florence, Italy

# Outline

- Scope of upgrade

- New Barrel Design

- New End Disk Design

- Detector Module Changes

- Changes to the readout chip

- Design

- Tests

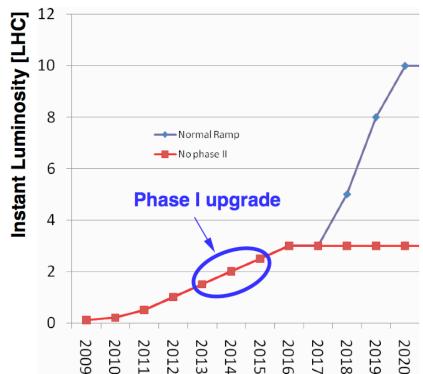

# LHC upgrade plans

By 2014:

~2xLHC luminosity

Upgrades in (longer) shutdown

Consequences for CMS:

- Most subdetectors min. changes

- Replace pixel system (rad damage)

By 2018:

- ~10xLHC luminosity

- very long shutdown

- replacement of complete (CMS) Tracker

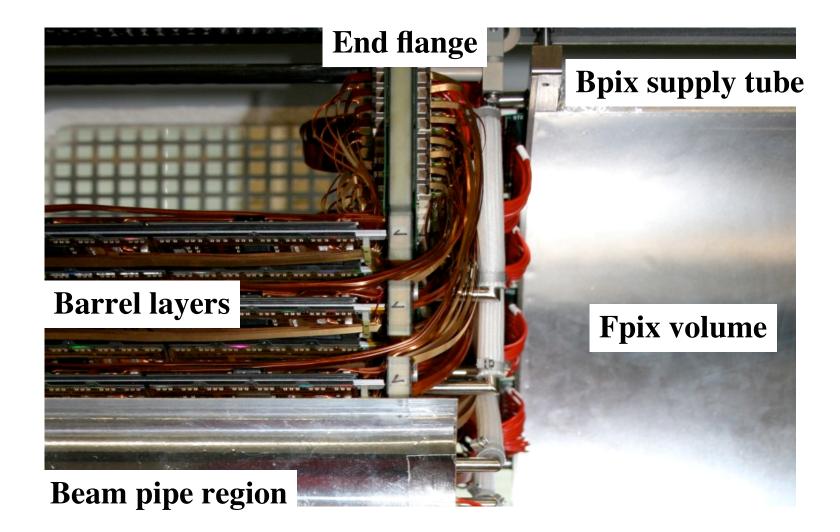

## CMS Pixel System

- Designed for fast insertion (beam pipe bake out)

- Will be done in regular shutdown

- Can be replaced by improved system

## **Constraints and Requirements**

Same/better performance:

- less inefficiency at high rates

- reduce material effects

Have to use existing services:

- Cooling pipes, cabling, fibers

- power supplies, readout hardware

Stay in old envelope

Leave system unchange as much as possible:

- keep ROC core untouched

- $\rightarrow$  minimise recovery time in competetive physics situation

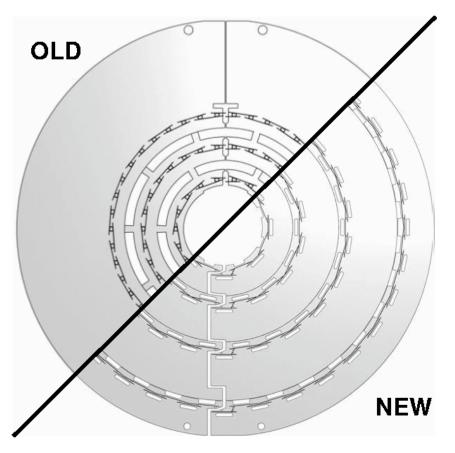

### Mechanics of Barrel

Add 4<sup>th</sup> layer :

- layers @ 39,68,109 & 160 mm

- beam pipe clearance 4 mm

- 8 modules along z (1216 total)

- 'ultra' light support structure

CO<sub>2</sub> based cooling system

- $\rightarrow$  more robust (standalone) tracking

- $\rightarrow$  better connection to strip tracker

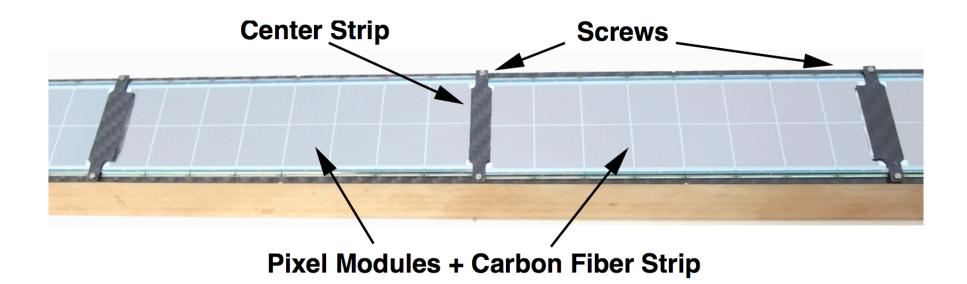

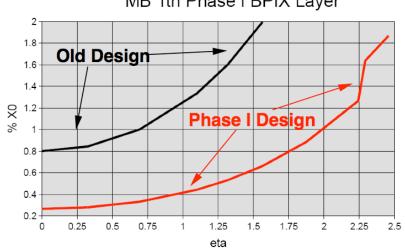

## Prototype

Layer 1 prototype:

- 200  $\mu m$  carbon fiber

- 4mm Airex foam

- Stainless steel tubes:

- 1.5 mm OD, 50µm wall

- Tube bends: 1.8mm OD, 100μm wall

- tested: ~100 bar & -10°C..10°C

- Factor >3 gain in material budget

→4 layer system will have half of MB of old 3 layer system

MB 1th Phase | BPIX Layer

**CMS Pixel Upgrade**

# CO<sub>2</sub> cooling

Advantages:

- long cooling lines ~ 5m

- no manyfolding needed

- very small tubes

→big MB reduction

BUT:

- system with relatively high pressures (~60 bar @ room temperature)

- CMS cooling tubes ok up to 40 bar

- $\rightarrow$  special star tup/safety

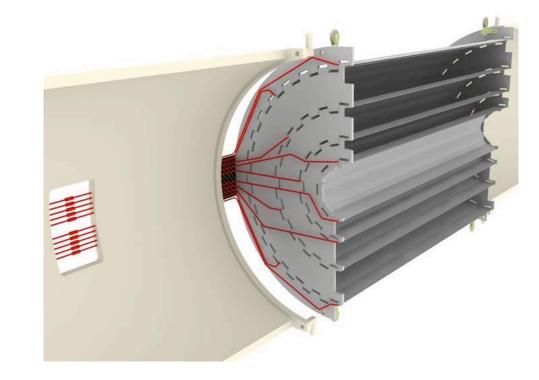

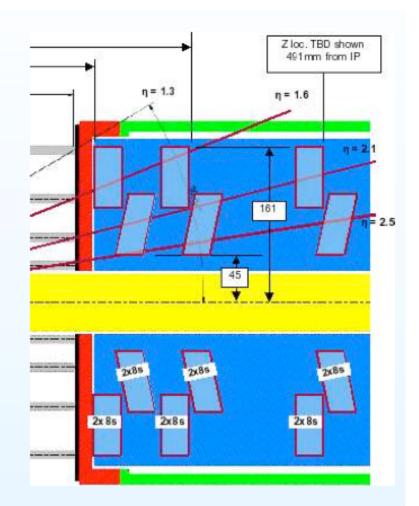

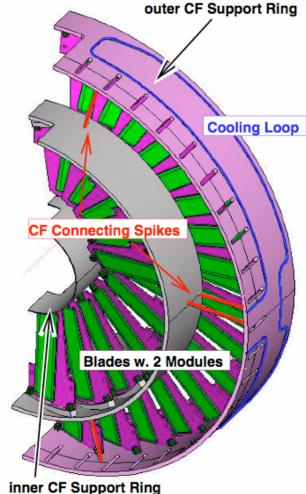

### Mechanics of Disks

- 3 + 3 discs @ barrel ends

- Each disc consists of:

- 2 half discs

- inner & outer ring of modules

- inner ring tilted by 12°

- 4 point coverage up to  $\eta$ = 2.5

- very small gap ~  $\eta$ = 1.3

## Mechanics of Disks

Inner & outer ring of blades

CO<sub>2</sub> tubes embedded in half disk support:

- support cylinder:

- Carbon carbon

- Grooves for cooling tube

- Stainless steel tube:

- 1.8mm OD, 100µm wall

#### Blades:

- all identical

- Rotated by 20° radial

- Tilted by 12° (inner ring)

- individually replaceable

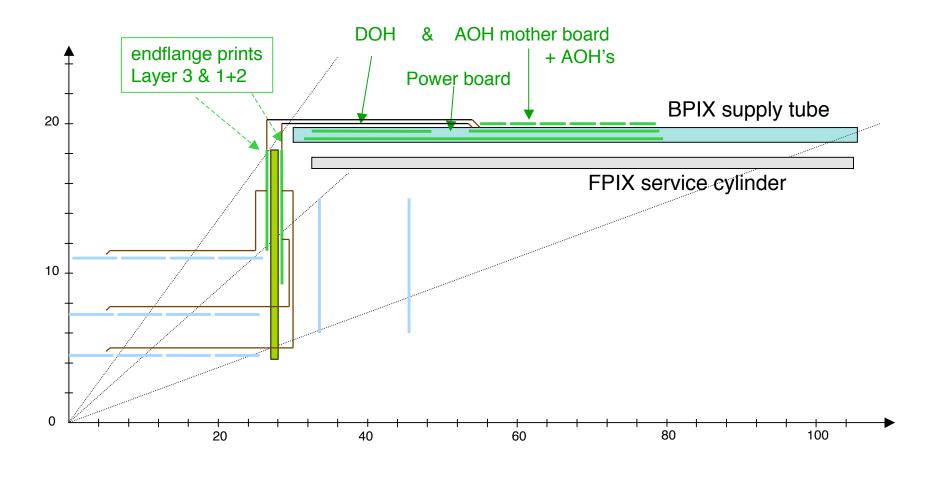

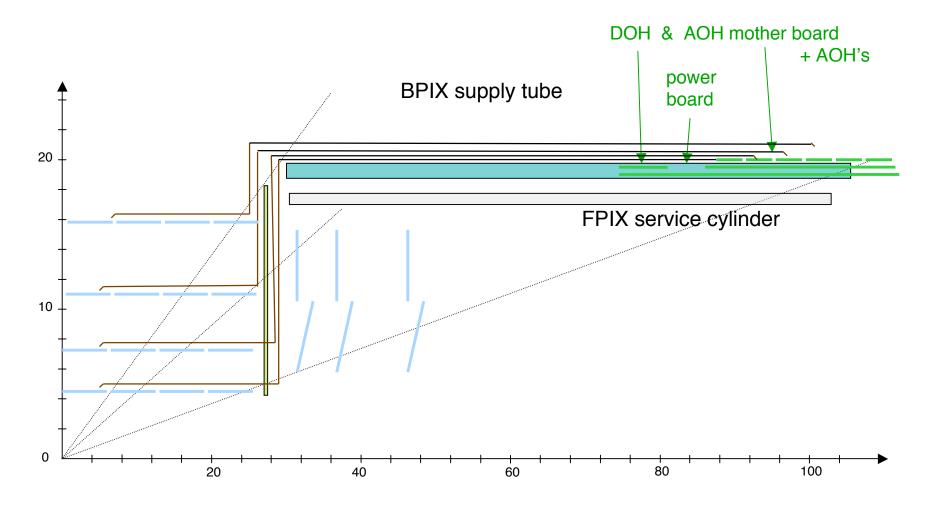

#### Supply Tube (+Z)

**CMS Pixel Upgrade**

**CMS Pixel Upgrade**

| <b>CMS</b> Pixel | Upgrade |

|------------------|---------|

|------------------|---------|

| <b>CMS</b> | <b>Pixel</b> | Up  | grade |

|------------|--------------|-----|-------|

| 01120      |              | ~ r | 8     |

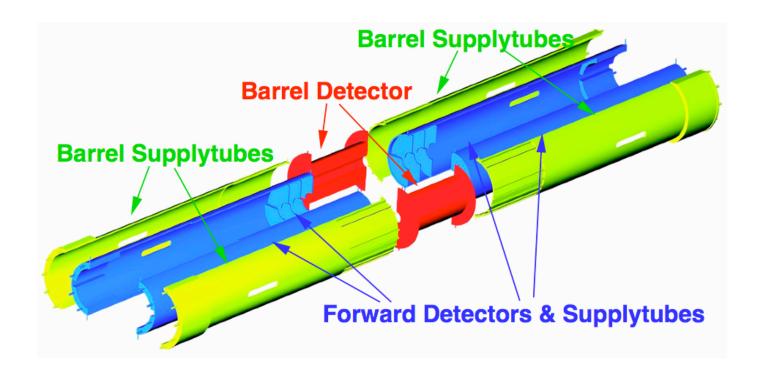

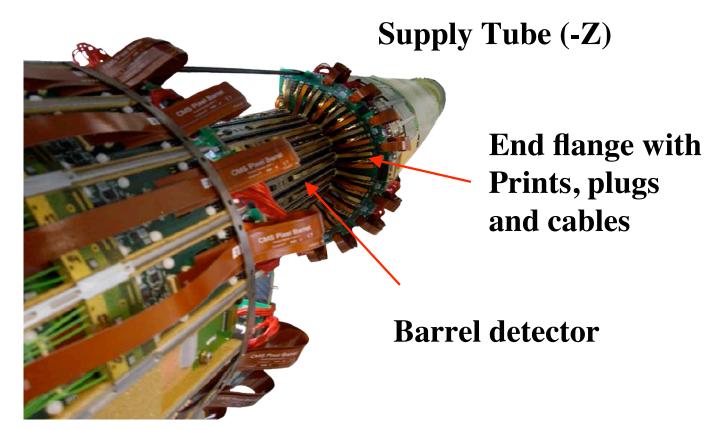

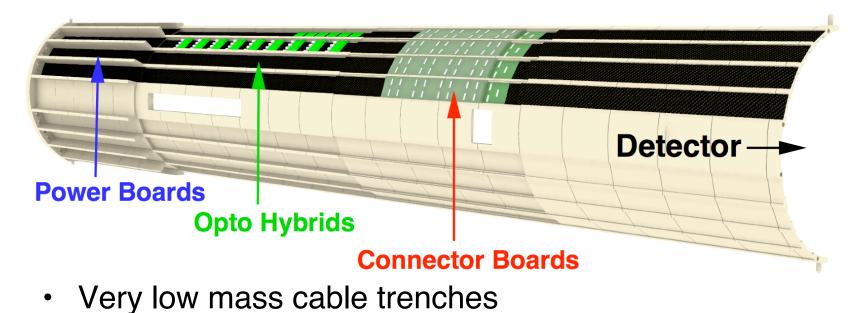

# New Supply Tube

- Module connectors:

- Layer 3+4 outside

- Layer 1+2 inside

- New opto hybrids

- 2:1 DC/DC converters

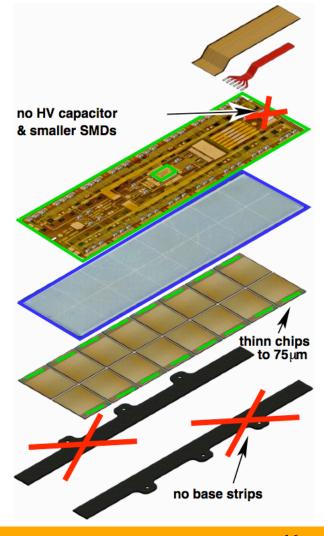

# Module Design Changes

One design(barrel +endcap) Based on present barrel module Changes:

- No basestrips

→Better cooling contact

- ROC:

- − thickness  $175\mu m \Rightarrow 75\mu m$

- HDI:

- No HV-capacitor

- Miniaturize SMD-components

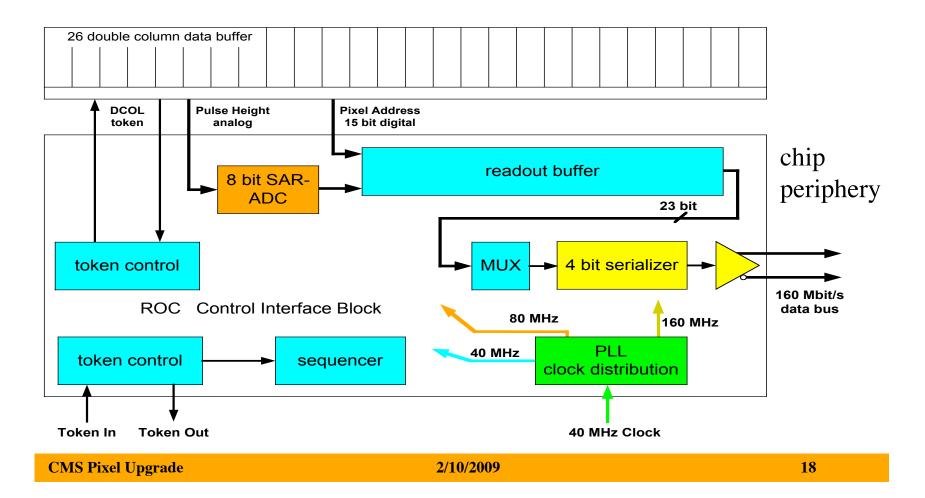

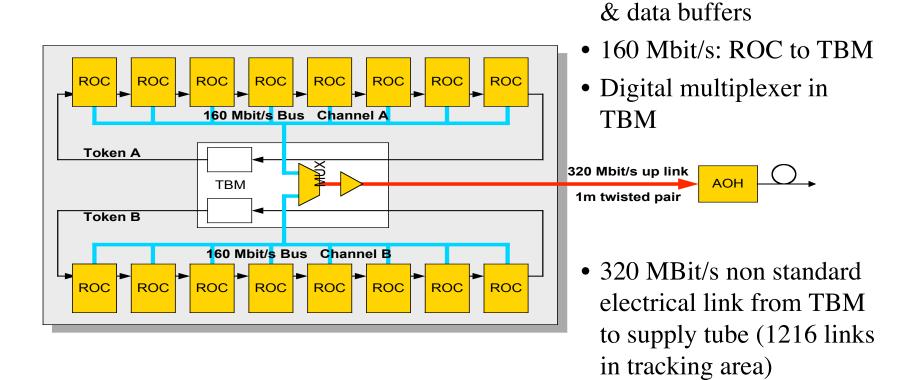

# Changes in the ROC

- Larger data buffers to cope with higher rates

- Digital readout links at 160 Mb/s

- Now 2x analog link at 40 MHz in layer 1&2

- Very low power electrical link of O(1m)

- ADC on chip operating at 80 MHz

- Now analog transmission of pulse height information

- New readout buffer stage to reduce dead time

- PLL to provide 80/160 MHz

## Changes in the ROC

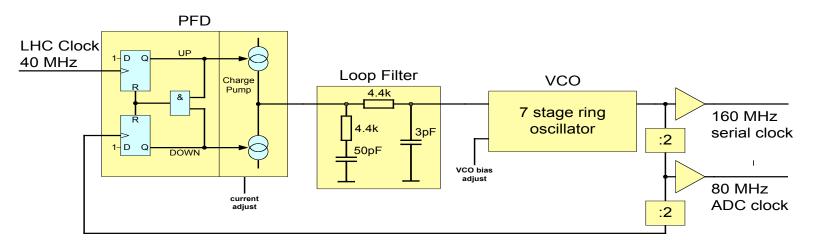

# Frequency Multiplier PLL

Technical Data:

- 250 nm ASIC Design

- Reference input: 40 MHz

- Outputs: 80 MHz (ADC), 160 MHz (serializer)

- No external components needed (includes loop filter, capacitors)

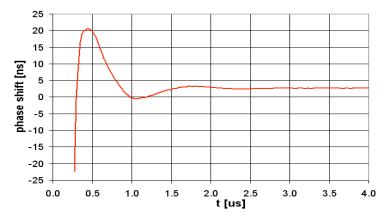

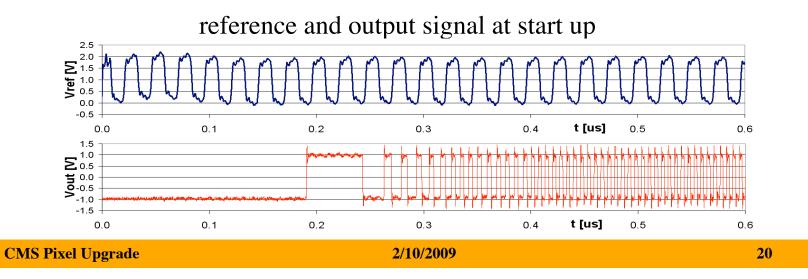

## PLL Results

Test results:

- PLL locks for 10 ... 75 MHz reference frequency

- Supply current: 720  $\mu A$

- Lock time: 3 us

- Jitter < 30 ps

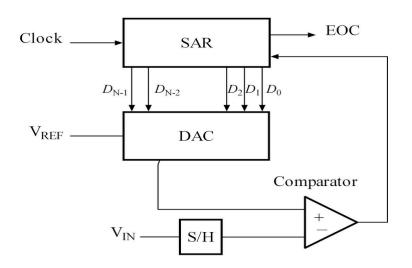

# 8-bit ADC: design

- Successive approximation 8 bit ADC with S&H

- Clock frequency: 80 MHz

- Conversions time: 8 clock cycles

- Prototype designed and under test

- Results:

- Works well up to 40 MHz

- Good linearity

- But: is unstable at 80 MHz

- $\rightarrow$  good diagnostic possibilities

- $\rightarrow$  could reproduce in simulation by adding parasitics

- $\rightarrow$  are about to understand problem

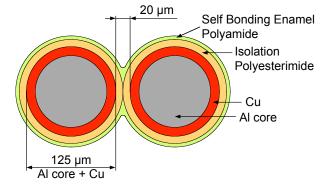

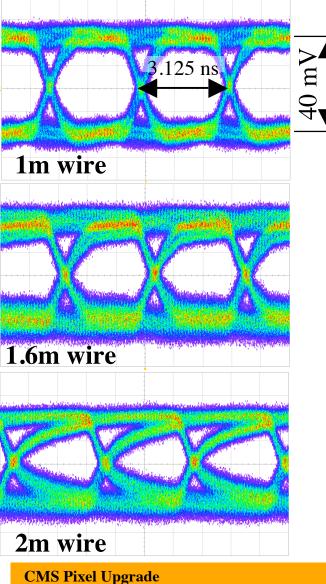

## Electrical Low Power Data Link

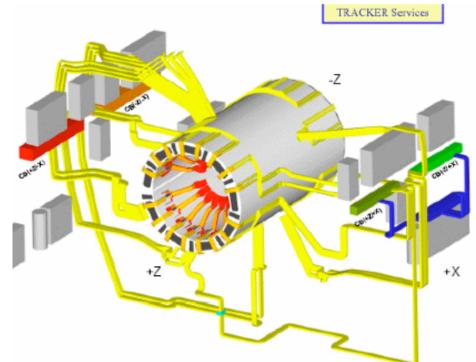

- 1216 Up links from module to outside the tracking area

- 320 MBit/s over 1 m

- Unshielded micro twisted pair cable (125 μm wire diameter, low mass)

- Low power differential driver and receiver (LCDS)

- Bundled with power and control wires to one module cable

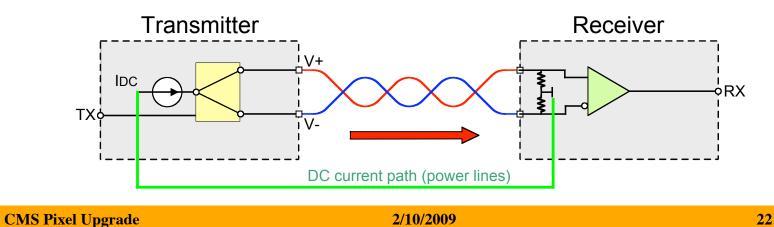

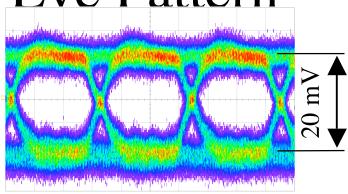

## Results: Eve Pattern

- Wire length: 1 m

- 320 Mbit/s

- Minimal amplitude: 20 mV (+/- 10mV)

- +/- 500 mV DC offset between driver and receiver

- Bit error rate < 10e-12 (different condition)

- Crosstalk: -27 dB

- Power consumption / link: 4mW (12 pJ/bit)

# Conclusion

New improved design for CMS pixel detector shown

•4 barrel layers and 3 disks

Huge reduction in material budget

•Factor 3 per barrel layer

•Factor 2 per disk

•Largest gain due to CO<sub>2</sub> cooling

Large extra savings by moving material out of tracking volume Status:

•Barrel: Design finished

•Prototype for layer 1 mechanics built

•Prototype for supply tube in production

•Disks: Design advanced

•ROC: all new cells prototyped and tested.

•ADC needs more work

•TBM (module controller chip): need new design of uplink part •Core unchanged.

**Target date for insertion: 2014**

CMS Pixel Upgrade

# Backup Slides

## Digital Readout Overview

• 320 Mbit/s optical fibres

• ROC with digital readout

#### New module mounting