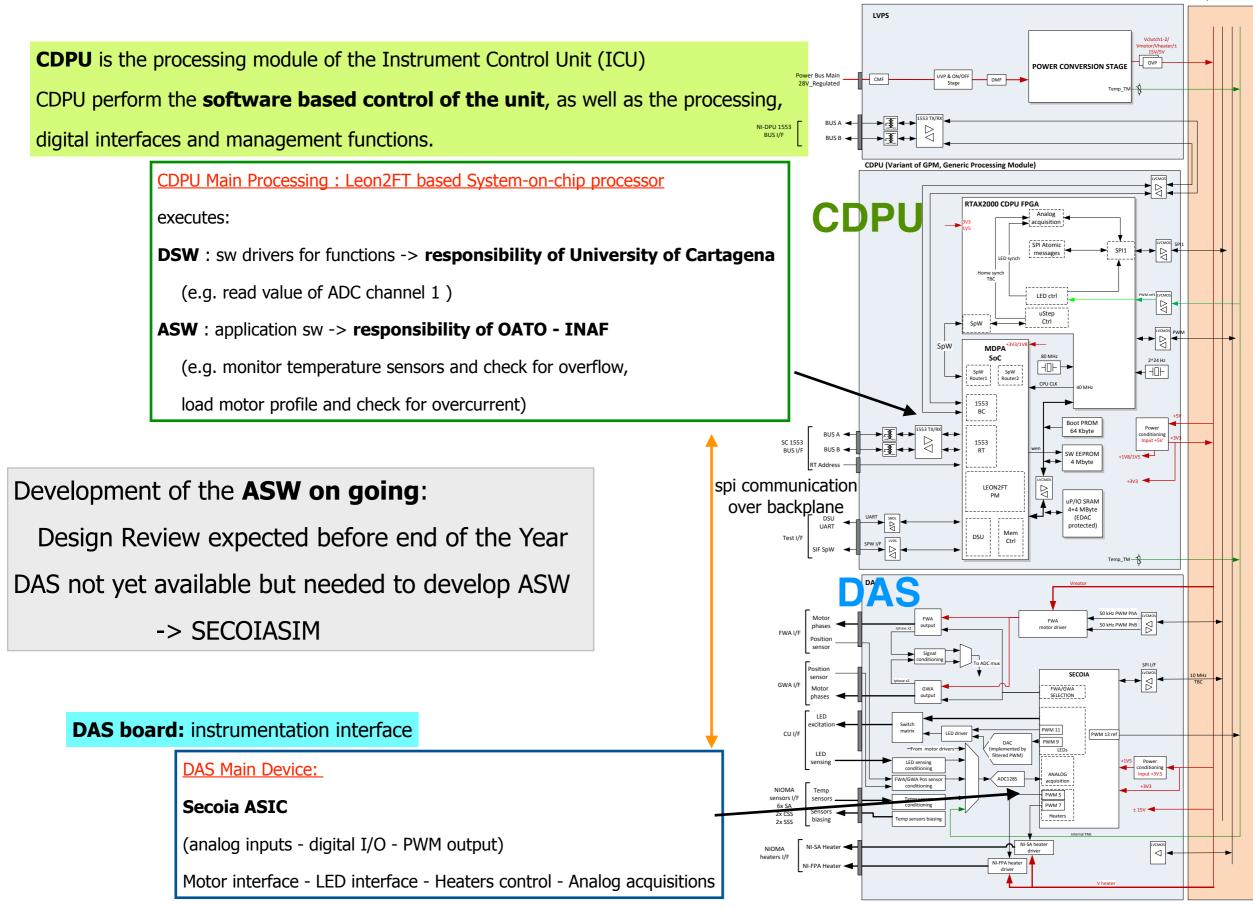

# **Instrument Control Unit Overview**

Backplane

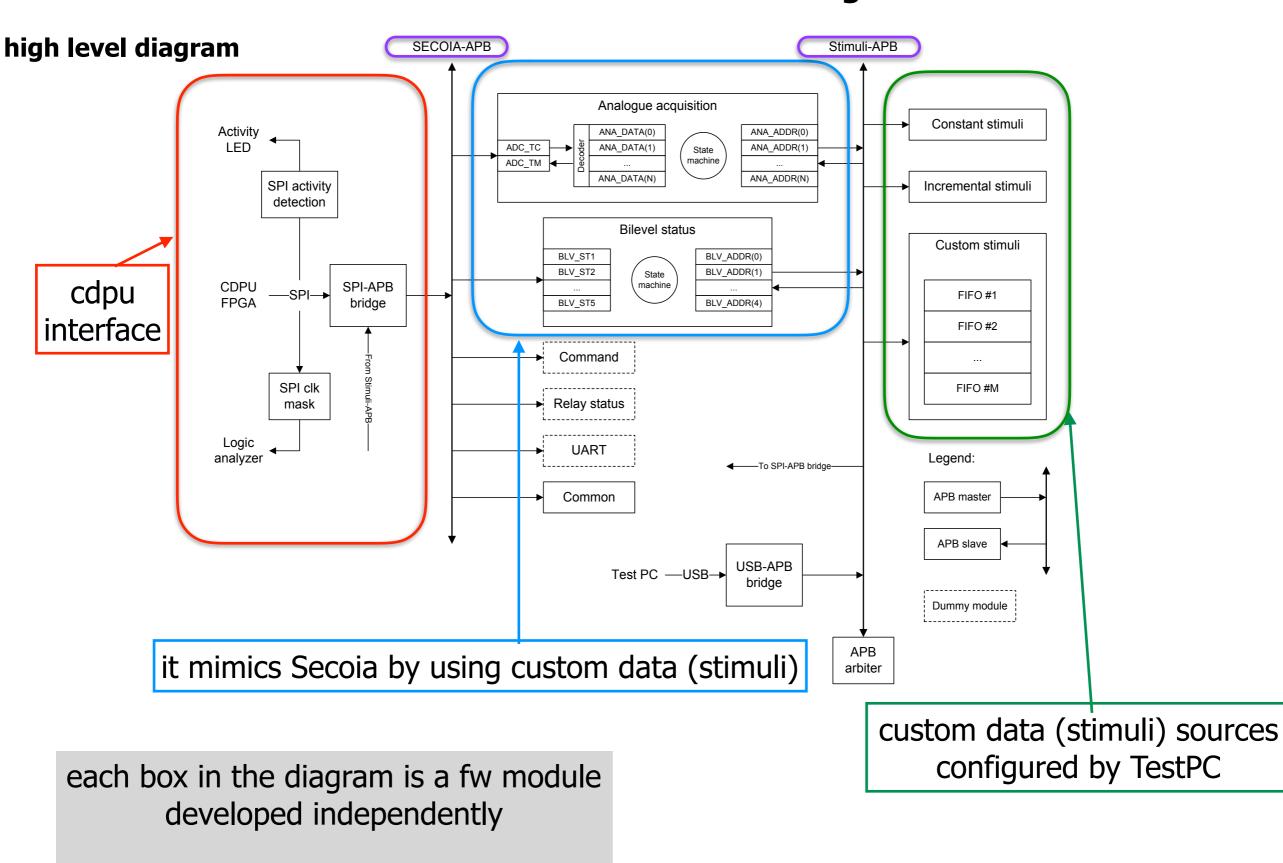

### SecoiaSim Project : a FPGA-based Secoia Simulator

SecoiaSim : hardware simulator for SECOIA (only a subset of functionalities) implemented with FPGA Developed for DSW test , it will be used also to support the ASW development and test

**Coordination** of the project is a **UPCT** (University of Cartagena) responsibility; **joined** by UAH (Alcala') and **INFN - Bologna**

**Firmware design** shared between UPCT - **INFN-Bologna** - UAH Software test & developed by UPCT

adapter

It is implemented on the FPGA (Xilinx Spartan 3A) - based module hosted into the **ICU-EBB Setup Board** (part of the ICU test bench delivered by CRISA) **USB** Fpga esentation is provided logic analyzer Date: 29/04/2016 specification document Setup Board Page: 7/38 Power supply EBB2 SVM bus Power connector 1553 RT (A) Power CDPU 1553 RT (B) SPI ckplane Setup-/ GPM 1553 RT Addr FPGA Discrete JTAG I/F (not in FM) Setup motherbo Reset Reset Test I/F DPU board button bus 1553 BC (A) Reset ã Aux board \_\_ button 1553 BC (B) 5 WMs reset Eclipse Setup-FPGA USB RS-232 programming GRMON SW USB DataFeeder CDPU-FPGA USB Test PC FlashPro programming USB Logic SW DAS-Monitor Analyzer Test generator CDPU TestAnalyzer USB 553-USB SVM/DPU simulator

### specification document SecoiaSim - FW design

Page: 9/38

Modules are connected using APB bus

## **SecoiaSim - Status and Plan**

Started in April '16, planned to be ready beginning of July **Version 1.0 delivered on July16th**

One **test bench** available in Spain devoted to DSW test **2 in Italy** for ASW test: 1 in OATO, **1 in Bologna** 1 additional FPGA-based mezzanine available in Bologna for dedicated development fw upgrade

#### **INFN** involvement:

- implementation of about 1/3 of the VHDL modules (done!)

- participation in the overall code review (done!)

- constant collaboration and consultation with UPCT on design refinement, bug fixing, design update (on going)

- supply of the GIT repository (Baltig) both for fw and sw

### Status: Italian test stands are operational and ready

### **Future Activities:**

(support) collaboration with OATO on both developing ASW test cases and properly configuring of the SecoiaSim

implementation of additional features peculiar to ASW test (for instance: generation of correct/wrong data answering to a given motor profile)

improve fw performance (if needed after test cases definition): (for instance: using the available DDR3 memory to inject a long data sequence)