# Richieste di Servizi di Base BESIII Elettronica e Calcolo

on behalf the ₩5Ⅲ group ...and a bit of

### BESIII – Italy Collaboration

#### Activities of the group

- data analysis

- analysis internal referral

- support computing production

- data taking shifts

- CGEM-IT

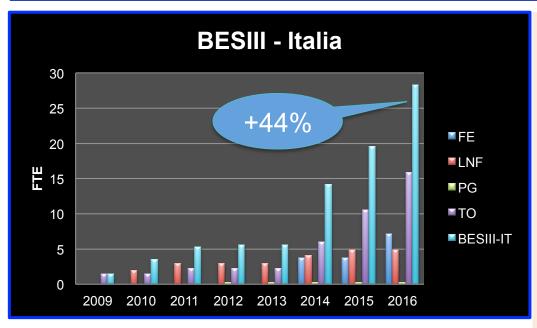

## The Italian Collaboration (FE, LNF, PG and TO)

- 28 FTE (was 6 FTE in 2013)

- 30 authors (~6% of the total)

- 41 physicists + technologists

- about 7% of the authors

#### Responsibility roles

- Executive Board (M. Maggiora)

- Chair Nominating committee (M. Maggiora)

- Speakers Bureau (F. Bianchi)

- Tech Board (G. Cibinetto)

- Director of IHEP-INFN Joint Laboratory (M.Maggiora)

#### **RISE H2020 CGEM Project**

Coordinator (M. Maggiora)

Il supporto dei servizi è di vitale importanza per l'impegno che la collaborazione italiana ha assunto nel progetto CGEM e nel computing.

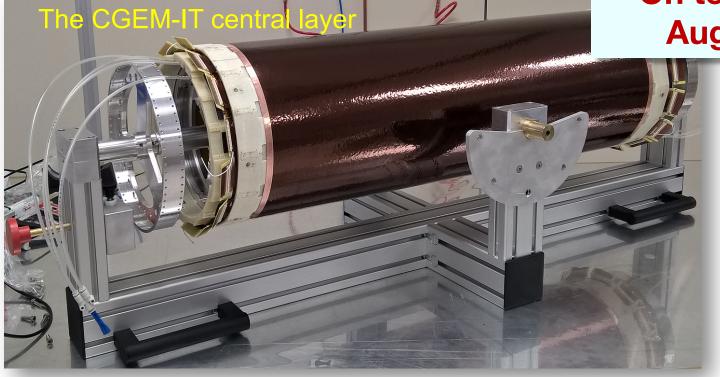

### The CGEM-IT Detector

The detector is ready and has been turned on.

HV test were successful!

Construction validated!

On test beam in August 2016

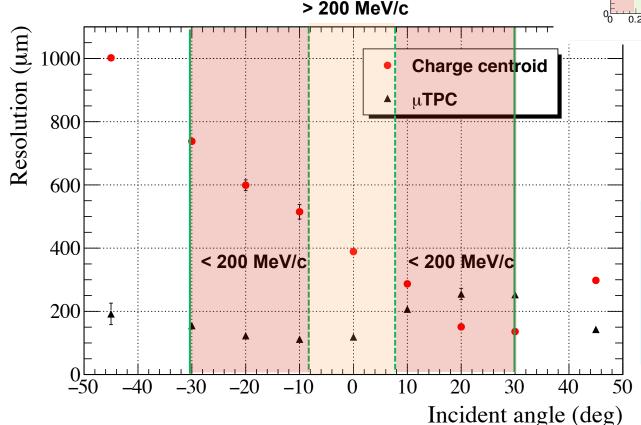

### μTPC results with 1 Tesla magnetic field

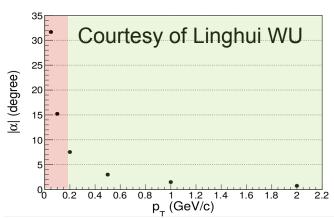

Expected entrance angle at the outer radius of CGEM-IT (primary vertex particles)

- ✓ Rohacell instead of honeycomb (lighter)

- ✓ Jagged-strip readout

- ✓ Analog readout (and not digital)

- ✓ µTPC mode

The relevant angle for the azimuthal spatial resolution is the entrance angle of the particles which are bent by the magnetic field.

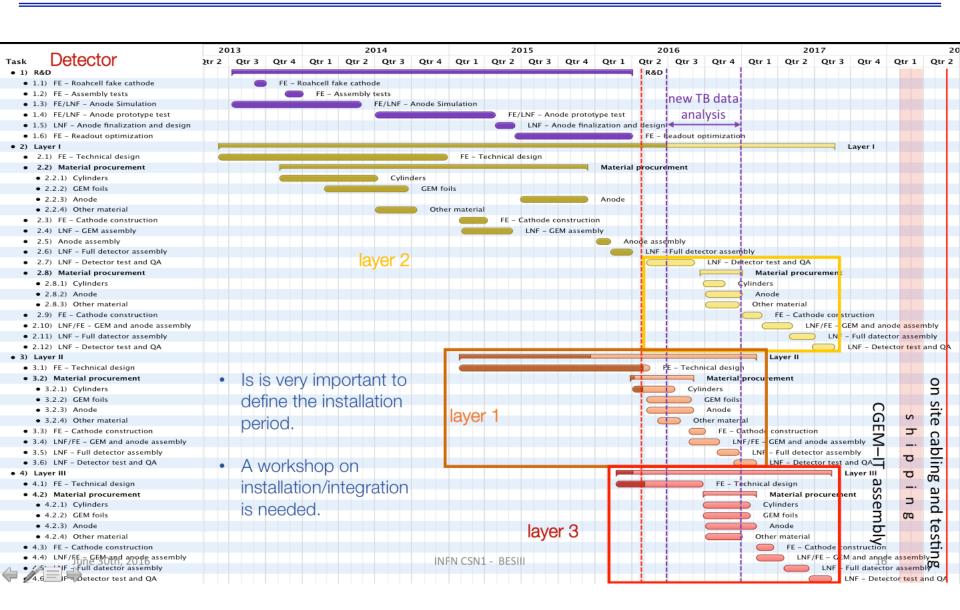

### The Schedule

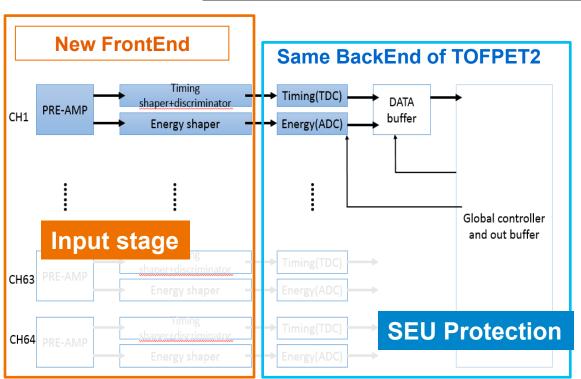

#### Achievements on CGEM ASIC development

The new ASIC for CGEM has been developed in the VLSI Lab

#### **Designers:**

H.S. Li, C.Y. Leng, J.Y. Chai (IHEP)

#### **Technical Advisors:**

A. Rivetti, M. Rolo (INFN)

- New FrontEnd adapted for GEM signals

- TOFPET2 BackEnd, developed for PET application, has been used

- ♦ UMC 110 nm

- ♦ 64 channels

- Charge measured by an ADC

### 1<sup>st</sup> foundry submission done in May 2016

### CGEM ASIC Schedule 2016

✓ Development of PCB (Mignone), FPGA and LABVIEW programs (post-doc Alekseev + Wheadon + student Gertosio) to test the ASIC are ongoing

They should be completed within July 2016

- ✓ Bonding of the ASIC in August (depending on delivery)

- ✓ ASIC bench test will start end of August, should be completed within October 2016

- ✓ ASIC validation with one CGEM layer (impact of long strips → 100 pF capacitance) at LNF end of October 2016

- ✓ 2<sup>nd</sup> foundry submission (if needed) no later than December 2016

#### CGEM ASIC Schedule 2017

- Change of PCB e FPGA programs (if needed) to test the ASIC within March 2017

- ➤ Bonding and Bench test of the 2<sup>nd</sup> ASIC (if needed) expected from April 2017

- Complete the design and the integration of the final ASIC in May 2017

- ASIC engineering run in May 2017

- Development of compact on-detector PCB (Mignone) within July 2017

- Bonding of ASIC (160 chips on 80 PCB) in July-August 2017 (depending on delivery)

- Final test of all the ASICs with the PCB within September 2017

- ASIC validation on the full CGEM detector with cosmics at LNF within end 2017

In order to fullfil the commissioning of the CGEM detector at IHEP Final ASIC engineering run should be NO LATER than June 2017

### Manpower for CGEM ASIC development

#### Man Power required to Torino Electronics Lab in 2017

- > 4 months x 1 FTE (M. Mignone)

- Change (if needed) on PCB for 2<sup>nd</sup> ASIC prototype (1 month)

- Development compact on-detector PCB (3 months)

- > 2 months x 1 FTE (Technician for bonding -160 chips)

- 2 months x 1 FTE (Technician to support final ASIC test)

- > **25% or more** (M. Rolo)

- Change (if needed) on 2<sup>nd</sup> ASIC prototype

- Development and integration final ASIC

Richieste 2017

#### BESIII Computing Activities @ INFN-TO

- cloud infrastructure at INFN-TO Computing Center:

- first cloud infrastructure optimised for scientific computing in an INFN Section (not taking into account CNAF)

- virtualised: VMs, farms, full Tier-2 Grid infrastructures, LANs

- INFN ⇔ IHEP bandwidth:

- optimised to ~ 1Gb/s

- INFN-TO production cloud provides to BESIII, since 2014:

- 2KHS06 (~ 200 cores) and 20 TB net reserved for BESIII

- shared access to 0.7KHS06

- fully transparent Tier-2 Grid Infrastructure, accessible by IHEP

- direct submission to CE, contestualisation via CVMFS

- job submission in VMDIRAC: full elasticity (VM birth & death)

- full interoperability within BESIII distributed computing

### BESIII Computing Activities @ INFN-TO

- fair-share access to ReCas Infrastructure(s) at INFN, since 2015:

- multi-experiment GRID Infrastructure

- 200 cores reserved to BESIII

- 30 TB storage dedicated to BESIII

- fair-share access to more resources

INFN contribution to BESIII has doubled in 2015 w.r.t. 2014 We are asking for 500 more core in 2017!

### (not only) BESIII Computing Activities @ INFN-TO

- INFN proxied IHEP in H2020:

- BESIIICGEM has been funded, it includes joint cloud R&D

- VLDATA has not been fundend, it included joint cloud R&D

- working together lead to a real testbed dedicated to cloud R&D

- room for future H2020 activities and applications

- cloud testbed at INFN-TO Computing Center:

- full cloud production infrastructure replicated to perform "wild" R&D on cloud computing

- 64 cores dedicated cores, since 2014; 72 more dedicated cores deployed in 2015

- 12 TB storage dedicated, 20 TB more from local fair-share use

- full access (root priviledges) by IHEP-CC Center staff

- R&D on: laaS, cloud bursting, monitoring tools, DIRAC, VMDIRAC, ... INFN contribution to IHEP is expected to grow even more in 2017.

#### Outreach

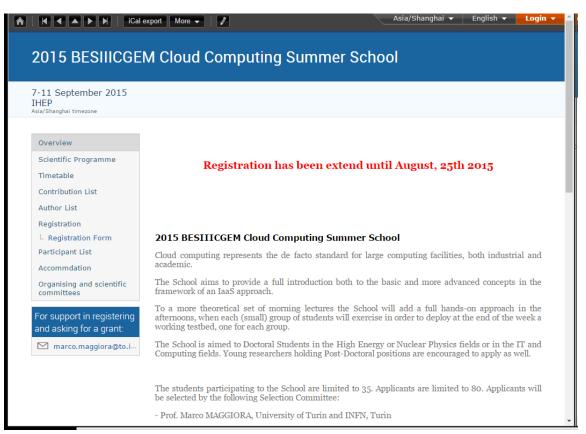

#### **Doctoral School on Cloud Computing**

✓ 9/2015 Doctoral Summer School, organized by IHEP and INFN (TO-CdC)

@ IHEP, Beijing

√ 7/2016 Doctoral Summer School, organized by IHEP and INFN (TO-CdC).

@ SDU, Jinan

#### BelleII Computing Activities @ INFN-TO

- cloud infrastructure at INFN-TO Computing Center:

- VMs and templates needed to run BELLEII simulations on the cloud tesbed are operative

- interfacing of the cloud infrastructure with BELLEDIRAC are in progress

- INFN-TO production cloud can provide to BELLEII in 2017:

- cores reserved for BELLEII (discussion in CSN1 expected soon)

- local storage reserved for BELLEII (idem)

- contestualisation via CVMFS

- job submission in VMDIRAC: full elasticity (VM birth & death)

- full interoperability within BELLEII distributed computing

- B2CT: a set of tools for deploying cloud micro-sites, small replica of the TO infrastructure

### Manpower for joint BESIII and BelleII Computing

- ✓ INFN-TO is providing a crucial contribution to BESIII and IHEP

- ✓ INFN-TO can very soon provide a crucial contribution as well to BELLEII and KEK

- Man Power required to Torino Computing Center in 2017:

- > 3 months x 1FTE (S. Bagnasco)

- 3 months x 1FTE (L. Gaido)

- 4 months x 1FTE (S. Lusso)

Richieste 2017

- maintenance production cloud infrastructure

- ♦ R&D on monitoring and elasticity, using IHEP and INFN testbeds

- R&D on monitoring and elasticity, using INFN testbeds interfaced with KEK

- ♦ R&D cloud bursting, using IHEP and INFN testbeds

- outreach: Doctoral Schools on Cloud Computing

|   | /  | 1                   |

|---|----|---------------------|

|   | IN | N                   |

| 1 | /  | di Fisica Nacionale |

#### DOMANDA DI UTILIZZO DEI SERVIZI DI BASE

| Septone di Torno      |               |                |             |         |                            |   |

|-----------------------|---------------|----------------|-------------|---------|----------------------------|---|

| Data della richiesta: |               |                | entro di    | $\Box$  | nuova richiesta            |   |

| 27-Giu-2016           | TecnologicoLE | :lettronica Ca | alcolo      | 믜       | richiesta di continuazione | * |

| Esperimento:          |               | Res            | sponsabile  | loca    | le Marco Maggiora          |   |

| BESIII                |               | Respons        | abile dell' | attivit | a' Simonotta Marcollo      |   |

#### Descrizione dettagliata dell'attivita' richiesta

#### Obbiettivo

Sviluppo del layout analogico dell'ASIC delle CGEM e integrazione con backend TOFPET2-like e test di un ASIC con tecnologia UMC .11um che sarà utilizzato come chip di readout della CGEM dell'apparato sperimentale di BESIII. Attualmente per BESIII è in corso lo sviluppo di un nuovo ASIC partendo da un disegno già esistente. Il primo prototipo è stato sottomesso in fonderia a maggio 2016, è stato fatto un nuovo disegno per la parte analogica che doveva essere adattata ai segnali della CGEM. Invece, per la parte digitale è stato utilizzato il layout già sviluppato dal gruppo di Lisbona per il TOFPET-2, aggiungendo la protezione per SEU.

Il prototipo, sarà disponibile ad agosto 2016 e in questo periodo si sta lavorando alla PCB e alla stazione di test con FPGA per il controllo del chip. Nei prossimi mesi 2016 questo primo prototipo sarà sottoposto a un test di funzionamento e caratterizzazione e

| PLANNING     |   |   |          |   |          |          |          |          |          |   |   | MILESTONES |            |                                                                                                        |  |  |

|--------------|---|---|----------|---|----------|----------|----------|----------|----------|---|---|------------|------------|--------------------------------------------------------------------------------------------------------|--|--|

| Subattivita' | G | F | М        | Α | М        | G        | ∟        | Α        | S        | 0 | N | D          | Data-mese  | Descrizione                                                                                            |  |  |

|              |   |   | <b>✓</b> |   |          |          |          |          |          |   |   |            | 31-Mar-20  | Disegno seconda (eventuale) PCB di test e bonding ASIC                                                 |  |  |

|              |   |   |          |   |          |          |          |          |          |   |   |            | 0 · 20     |                                                                                                        |  |  |

|              |   |   |          |   | <u> </u> | <b>✓</b> | <b>~</b> |          |          |   |   |            | 31-Lug-20  | Disegno PCB finale on-detector                                                                         |  |  |

|              |   |   |          |   |          |          |          |          |          |   |   |            | 0 . Lag 20 |                                                                                                        |  |  |

|              |   |   |          |   |          |          | <b>~</b> | <u>~</u> |          |   |   |            | 31-Aug-20  | Bonding ASIC finali (160 chips su 80 PCB)                                                              |  |  |

|              |   |   |          |   |          |          |          |          |          |   |   |            | or Aug 20  |                                                                                                        |  |  |

|              |   |   |          |   |          |          |          | <b>✓</b> | <b>✓</b> |   |   |            | 30-San-20  | Collaudo di tutti i 160 ASIC finali con PCB finale e elettronica readout finale e parte del rivelatore |  |  |

|              |   |   |          |   |          |          |          |          |          |   |   |            | 30-3ep-20  | Sistrollica readout limite o parte del livelatore                                                      |  |  |

|                   | •        |             |                                   |        |                  |              |        |   |  |  |

|-------------------|----------|-------------|-----------------------------------|--------|------------------|--------------|--------|---|--|--|

| Tecnici e tec     | nologi a | attualmente | Richieste di supporto tecnico per |        |                  |              |        |   |  |  |

| INFN              |          |             | ALTRI ENTI                        |        |                  | l'anno:      | 2017   |   |  |  |

| Nome              | mesi/U   | Ente        | Nome                              | mesi/U | Tipologia        | N.           | mesi/U |   |  |  |

| Marco Mignone     |          | •           | •                                 |        | Tecnici mecc. /  | elettr/CdC   | 3      | 8 |  |  |

|                   |          |             |                                   |        | Disegnatori me   | eccanici     |        |   |  |  |

|                   |          |             |                                   |        | Microsaldatori   |              |        |   |  |  |

|                   |          |             |                                   |        | Tecnologi prog   | ett. mecc.   |        |   |  |  |

|                   |          |             |                                   |        | Tecnologi eletti | ronici/CdC   |        |   |  |  |

| Manuel Da Rocha F |          |             |                                   |        | Tecnologi micro  | oelettronica | 1      | 3 |  |  |

#### Note:

Per completare il progetto dell'ASIC è necessaria l'esperienza di Manuel Da Rocha Rolo già consolidata in altri progetti e in particolare nel TOFPET e nel primo prototipo dell'ASIC per le CGEM.

Inoltre, è necessario un tecnico elettronico per le modifiche alla PCB per il test del chip (eventuale secondo prototipo) e per lo sviluppo della PCB per il chip finale (PCB compatta on-detector). Per questo lavoro è necessario il contributo di Marco Mignone, che ha un'esperienza consolidata in progetti analoghi e che attualmente sta già lavorando alla PCB del primo prototipo di ASIC. E' necessario anche il lavoro di un tecnico per il bonding del chip (eventuale secondo prototipo) e per i 160 chips finali. Inoltre, per il supporto al collaudo del chip si chiede che venga assegnato Francesco Rotondo

#### DOMANDA DI UTILIZZO DEI SERVIZI DI BASE

Responsabile dell'attivita'

| Data della richiesta:<br>25/06/2016 | Lab.<br>Tecnologico | Lab.<br>Elettronica | Centro di    | <b>√</b> |          | richiesta          |   |

|-------------------------------------|---------------------|---------------------|--------------|----------|----------|--------------------|---|

| 23/00/2010                          | rechologico_        | Elettronica         | Calcolo      |          | richiest | a di continuazione | ✓ |

| Esperimento:                        |                     |                     | Responsabile | e loca   | ale      | Marco Maggiora     |   |

Simonetta Marcello

BESIII e BELLEII

Marco Maggiora Marco Maggiora

#### Descrizione dettagliata dell'attivita' richiesta

L'attivita' in continuazione descritta nelle note, in considerazione dell'integrazione dei due esperimenti BESIII e BELLEII, richiede uno sforzo di coordinamento nella persona di Stefano Bagnasco, dei quali si richiede il 30% (3mu), e di supporto nelle persone di Stefano Lusso, di cui si richiede il 40% (4mu), e di Luciano Gaido, di cui si richiede il 30% (3mu). L'infrastruttura cloud di sezione per quanto riguarda BESIII e' pienamente operativa ed in produzione dal 2013, ed esporta un Tier-2 gLite a BESIII che risulta essere tra i piu' efficienti della Collaborazione. L'IHEP si e' inoltre rivolta a noi per essere

rappresentata nella partecipazione alle attuali e future call europee in ambito cloud computing, che costituisce uno dei WP del progetto BESIIICGEM approvato nell'ambito delle call H2020-RISE. Si prevede nell'immediato una significativa attivita' di ricerca ambientata sulla nostra infrastruttura e sulle infrastrutture di testbed create nel 2014 in CdC ed all'IHEP. Questa attivita' ha portato all'allestimento di una Scuola di Dottorato per il Cloud Computing organizzata da INFN-TO e dall'IHEP a settembre 201

|              | PLANNING |   |   |   |   |   |   |   |   |   |   |   |           | MILESTONES                                                                                         |  |  |

|--------------|----------|---|---|---|---|---|---|---|---|---|---|---|-----------|----------------------------------------------------------------------------------------------------|--|--|

| Subattivita' | G        | F | М | Α | М | G | L | Α | S | 0 | N | D | Data-mese | Descrizione                                                                                        |  |  |

| I fase       |          | ✓ |   |   |   |   |   |   |   |   |   |   |           | B2CT/B3CT (tools automatizzati di deployment di<br>micrositi cloud per BELLEII e BESIII) operativi |  |  |

| II fase      |          |   |   |   |   | ✓ |   |   |   |   |   |   | Wai-2017  | micrositi ciotal per dececci e de sinj operativi                                                   |  |  |

| III fase     |          |   |   |   |   |   |   |   |   | ✓ |   |   | Giu-2017  | VMDIRAC operativo per BELLEII                                                                      |  |  |

|              |          |   |   |   |   |   |   |   |   |   |   |   | Giu-Zu i  |                                                                                                    |  |  |

|              |          |   |   |   |   |   |   |   |   |   |   |   |           | VMDIRAC operativo in modo integrato per BESIII<br>e BELLEII                                        |  |  |

|              |          |   |   |   |   |   |   |   |   |   |   |   | DIC-2017  | e DELLEII                                                                                          |  |  |

|              |          |   |   |   |   |   |   |   |   |   |   |   |           |                                                                                                    |  |  |

|              |          |   |   |   |   |   |   |   |   |   |   |   |           |                                                                                                    |  |  |

| Tecnici e tec    | nologi a | attualment | Richieste di supporto tecnico per |        |                 |              |    |        |  |

|------------------|----------|------------|-----------------------------------|--------|-----------------|--------------|----|--------|--|

| INFN             |          |            | ALTRI ENTI                        |        | l'anno:         |              |    |        |  |

| Nome             | mesi/U   | Ente       | Nome                              | mesi/U | Tipologia       |              | N. | mesi/U |  |

| Stefano Bagnasco | 3        |            | '                                 |        | Tecnici mecc. / | elettr/CdC   |    |        |  |

| Stefano Lusso    | 4        |            |                                   |        | Disegnatori me  | eccanici     |    |        |  |

| Luciano Gaido    | 3        |            |                                   |        | Microsaldatori  |              |    |        |  |

|                  |          |            |                                   |        | Tecnologi prog  | ett. mecc.   |    |        |  |

|                  |          |            |                                   |        | Tecnologi elett | ronici/CdC   | 3  | 10     |  |

|                  |          |            |                                   |        | Tecnologi micro | oelettronica |    |        |  |

#### Note:

La sezione di Torino ospita un'infrastruttura cloud per il calcolo scientifico, prima ad essere operativa nello scenario INFN nazionale se si esclude il CNAF. Il nuovo approccio permette il completo disaccoppiamento dell'infrastruttura fisica da quella virtuale, dove quest'ultima puo' in modo trasparente ospitare il middleware grid esponendo le risorse con le specifiche richieste dagli ambienti di simulazione, analisi e ricostruzione delle diverse Collaborazioni.

Finanziata da DG1, da ALICE, da BES3, da BELLE2 ed in futuro da altri esperimenti, nel 2015 ha richiesto uno sforzo di coordinamento nella persona di Stefano Bagnasco, dei quali si era richiesto il 20% (2mu), e di supporto nella persona di Stefano Lusso, di cui era richiesto il 30% (3mu).