### ATLAS Pixel R&D Projects Meeting Bologna 14th-15th March

# HVR\_CCPD: Hybridization

#### A. Gaudiello

INFN & Università di Genova

(Summary of the work done in Genova, Milano and Trento)

March 14 2016

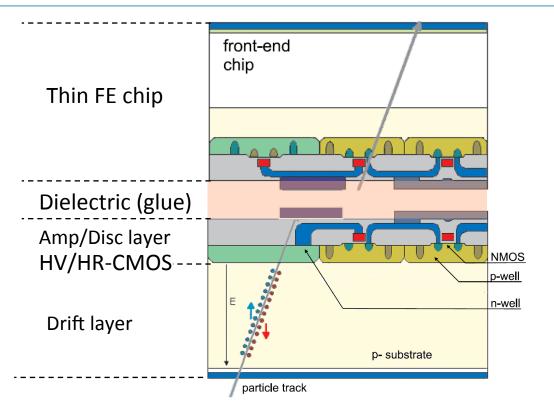

The new 65 nm front-end chip, being developed by RD53 Collaboration, will be compatible with  $50 \times 50 \ \mu m^2$  or  $25 \times 100 \ \mu m^2$  pixel size sensors.

The smaller pixel sizes imply up to five times the bump density used in the current ATLAS Insertable B-Layer modules and consequently an order of **120** k pixels per chip.

In next slides will be shown some studies done on:

capacitive coupling for CMOS

#### **Basic process**

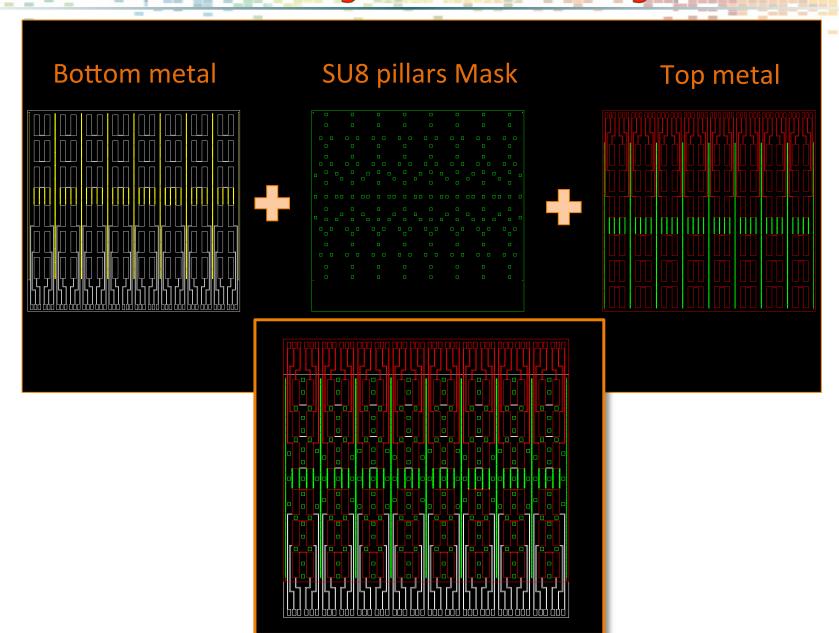

Spin SU-8 photoresist Pattern pillars by mask

Glue deposition

Align & pressure

R/O CHIP

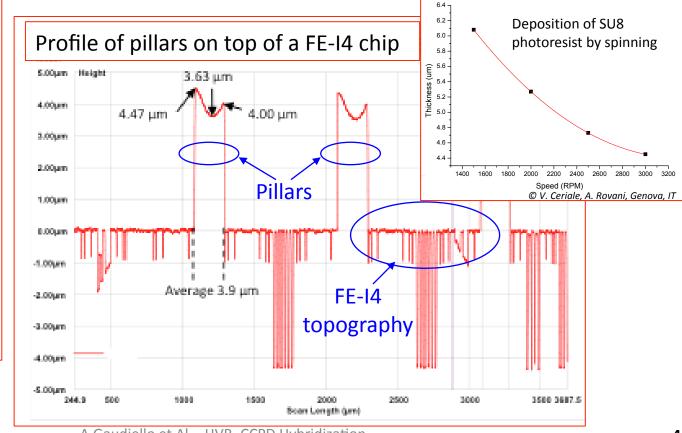

Deposition of SU8 photoresist by spinning

In 2014 and mid 2015 test on "in-house" hybridization

Successful single chip assemblies and learnt on glue and SU8 deposition (spacers)

Now systematic test on large chips (FE-I4 size) and wafer process for pillars

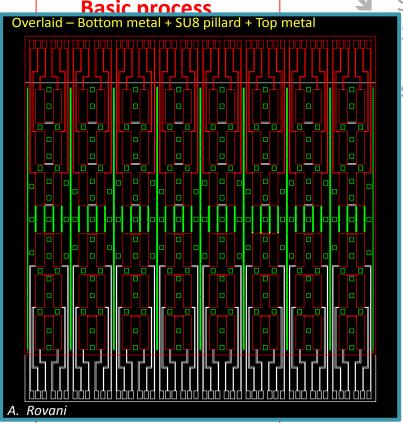

#### **Basic process**

Spin SU-8 photoresist Pattern pillars by mask

Glue deposition

Align & pressure

R/O CHIP

Deposition of SU8 photoresist by spinning

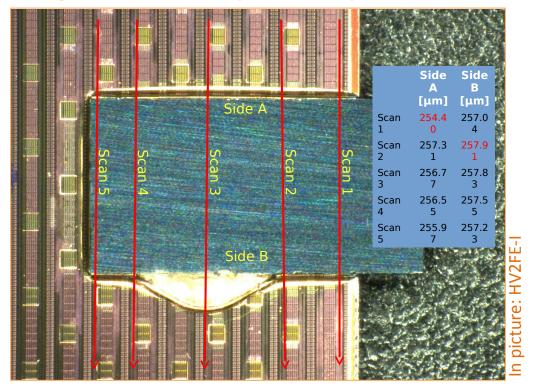

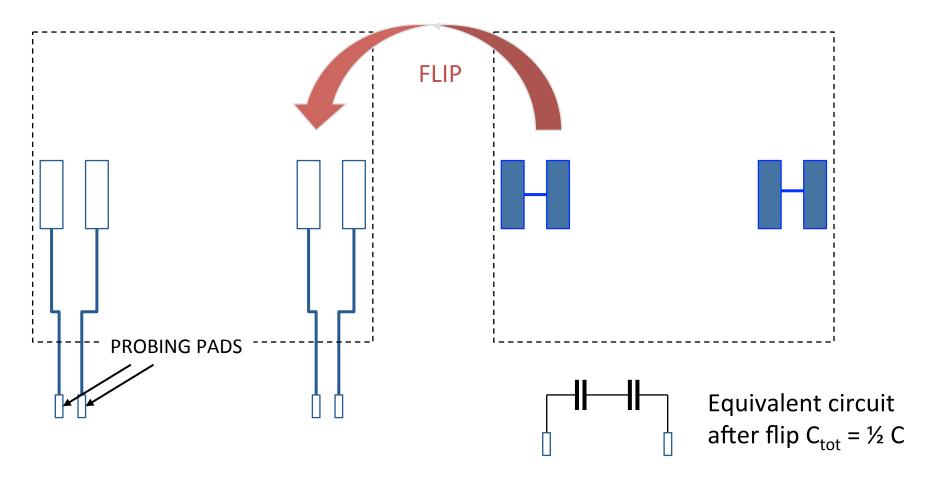

#### Procedure for Controlled Glue Thickness

- Deposit uniform layer of SU8 photoresist on R/O chip wafer (or single chip) by spinning tune for 5  $\mu$ m layer by controlling RPM speed

- Pattern pillars using lithographic process

In 2014 and mid 2015 test on "in-house" hybridization

Successful single chip assemblies and learnt on glue and

SU8 deposition (spacers)

stematic test on large chips (FE-I4 size) and wafer process for pillars

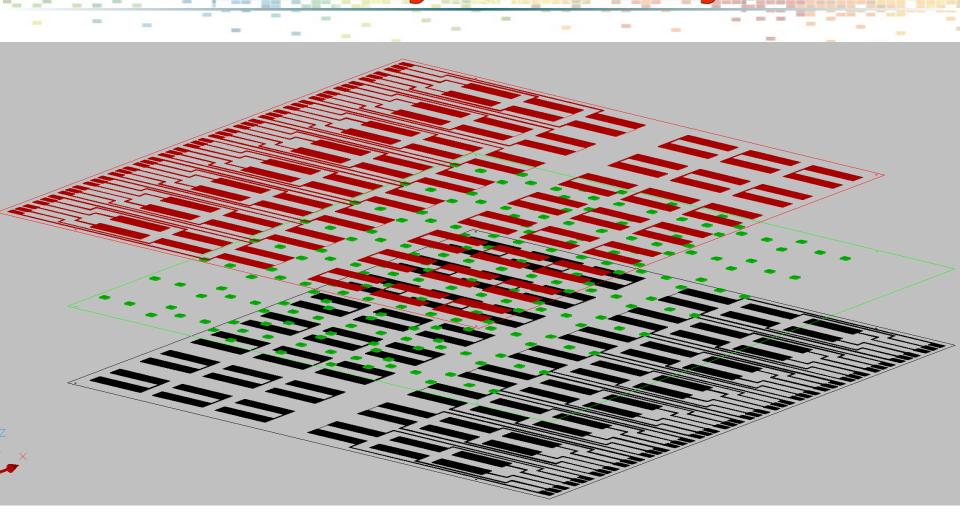

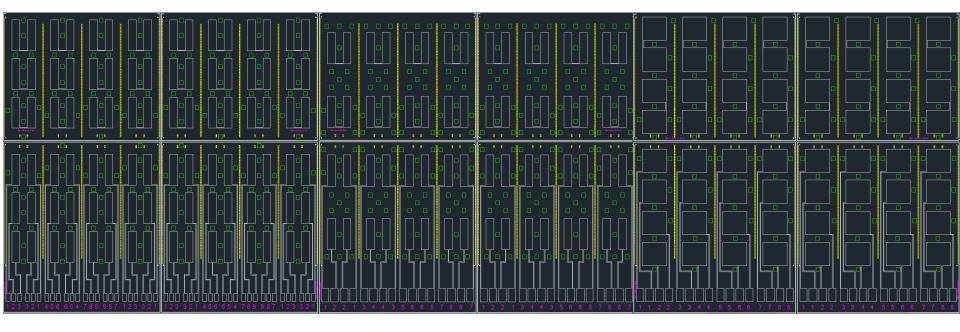

A batch of dummy wafer produces at FBK (Trento) with capacitive structures to test uniformity of glue thickness layer 6-inch wafers, 24-32 capacitors (3-7 pF) per chip

photoresist by spinning

#### **Basic process**

Spin SU-8 photoresist Pattern pillars by mask

Glue deposition

Align & pressure

DETECTOR CHIP R/O CHIP

Deposition of SU8 photoresist by spinning

In 2014 and mid 2015 test on "in-house" hybridization

Successful single chip assemblies and learnt on glue and SU8 deposition (spacers)

Now systematic test on large chips (FE-I4 size) and wafer process for pillars

A batch of dummy wafer produces at FBK (Trento) with capacitive structures to test uniformity of glue thickness layer 6-inch wafers, 24-32 capacitors (3-7 pF) per chip

The 6 wafers are at Selex together with pillar deposition mask – also 10 blank wafer provided to Selex to test SU8 spinning and photolithography – measurements of pillar uniformity will be done in Genova

PTA in Grenoble has been contacted for pillar deposition

Flip-chip at Genova and other labs – thermal/UV glue curing

(preliminary studies done)

Test pillar and glue process on dummy wafers/chips

Design a 6-inch wafer with FE-I4 size dummies – place 32 (24) capacitors of 1 (2) mm<sup>2</sup>

to test glue thickness uniformity over all surface

#### **Different Layouts**

#### **DESIGN 1**

48 capacitors 3.6 fF @  $5\mu$  dielectric ( $\varepsilon_r = 3.8$ )

#### **DESIGN 2**

32 capacitors

3.6 fF @ 5 $\mu$  dielectric ( $\epsilon_r$  = 3.8) ~7 fF @ 5 $\mu$  dielectric ( $\epsilon_r$  = 3.8)

#### **DESIGN 3**

24 capacitors

## Conclusions

### **Capacitive Couplings:**

- ✓ Good results of tests done on first lab prototypes

- ✓ Dummy wafers for FE-I4 size tests produced

- ✓ Measurements will start as soon as the dummies will return from Selex