### Dose Profiler electronics status

Giacomo Traini, Adalberto Sciubba

Pisa, INSIDE meeting

20/01/2016

## Outline

BASIC32 test completed!!!

Summary of test procedure and results

What are next step for the read-out system development

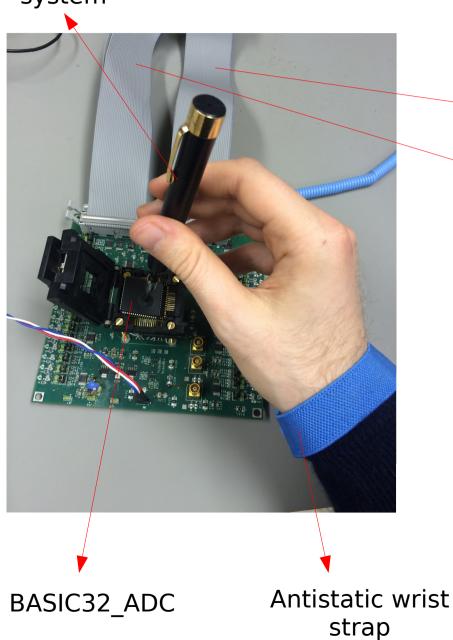

## **Test Setup**

Vacuum pick-up system

Plugged to V1495

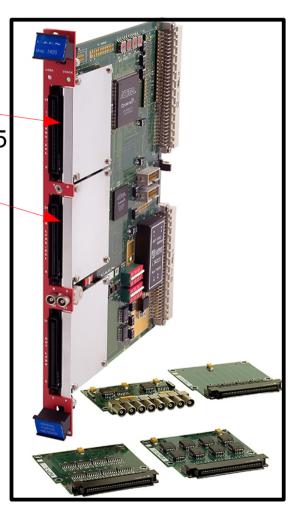

CAEN V1495: includes an FPGA that provides ASIC Configuration and DAQ 3

## Test procedure

Goal: check the functionality of BASIC32\_ADC

- Write and read configuration

- Pedestal acquisition: external trigger mode check

- Voltage offset DAC: we change bit of configuration, measuring the corresponding voltage at the input channels with an external ADC

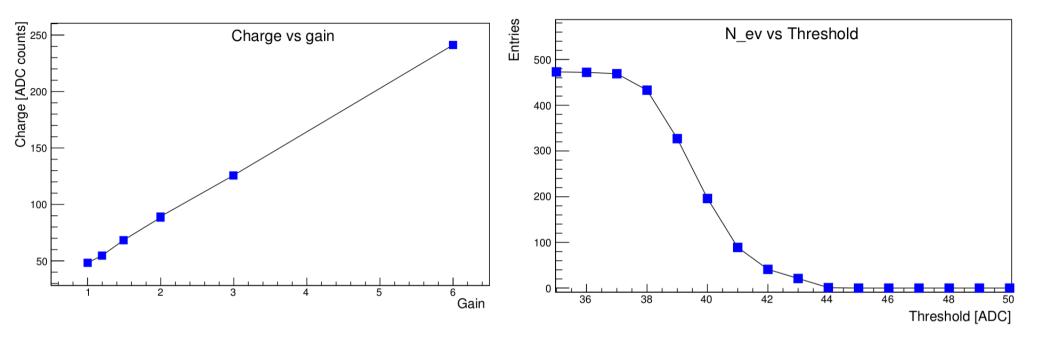

- Gain: we inject a fixed charge signal through a capacitance on the board, measuring charge vs gain

- Threshold DAC: we inject a fixed charge signal through a capacitance on the board, measuring the rate vs threshold

- Read-out time window

- Clock max frequency

## Results

- 6 BASIC show problems on voltage offset

- 3 BASIC shows problems on gain configuration

- 1 BASIC shows problems on read-out

- 1 BASIC show problems on setting configuration

- 150 BASIC can be used with clock up to 10 MHz

# 9 BASIC32\_ADC have been excluded from the front-end electronics of the tracker

# BASIC with only offset malfunctioning can be still used for calorimeter

108 BASIC32\_ADC have been delivered to realize 16+2 front-end board for the tracker

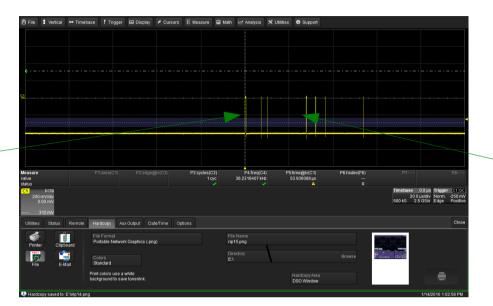

## Basic bad features: retriggering

"Afterpulses"

#### • All BASIC32 ADC affected

Primary internal

trigger pulse

- Depends on set threshold and set damping time of CSA

- It probably derives from an undesired internal coupling between input channels and trigger signal

#### **SOLUTION**

- Tracker: max gain needed, plan coincidence reduce effect

- Calorimeter: high light yield, we can reduce gain

# What happens now?

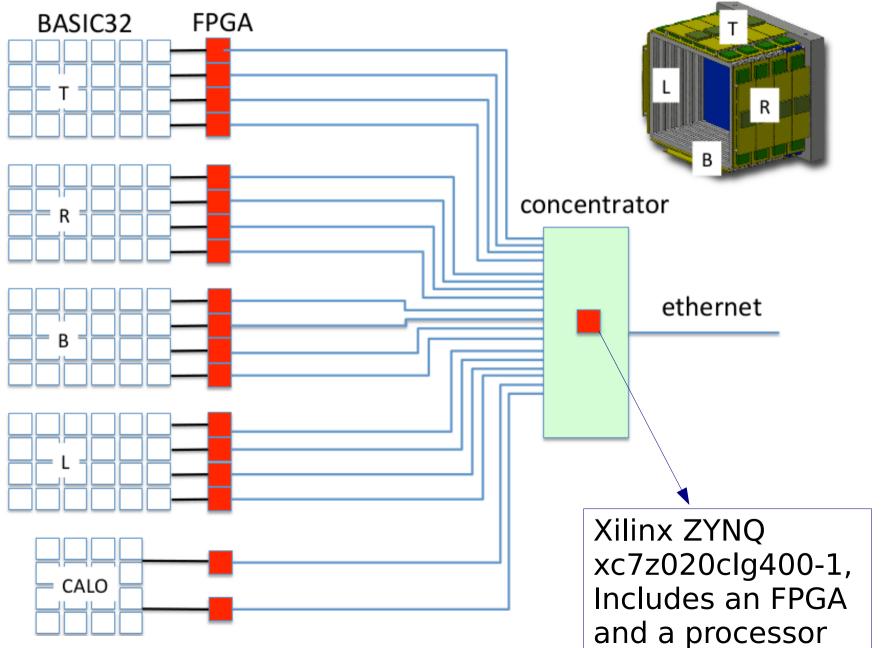

## Read-out system development

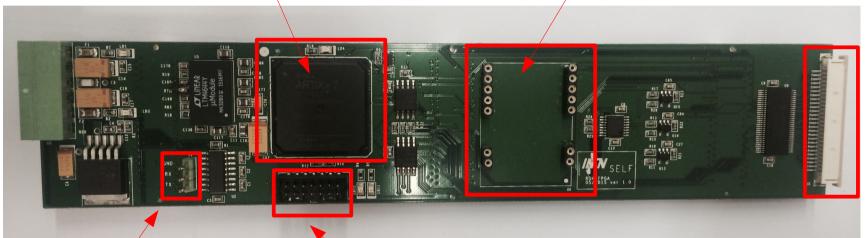

## FPGA board

FPGA Xilinx Artix-7 XC7A50T-1FGG484C

HV supply slot

SPI interface

JTAG connector (firmware)

Used for the test of the board with Raspberry Pi, a dedicated interface board will be produced

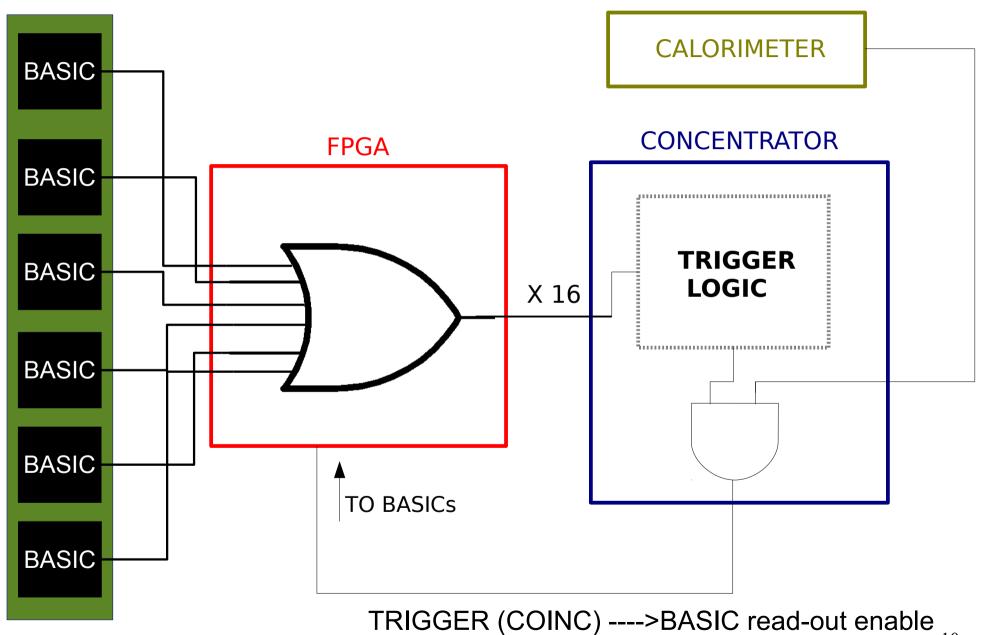

## Trigger scheme

X 16 (tracker + absorber)

10

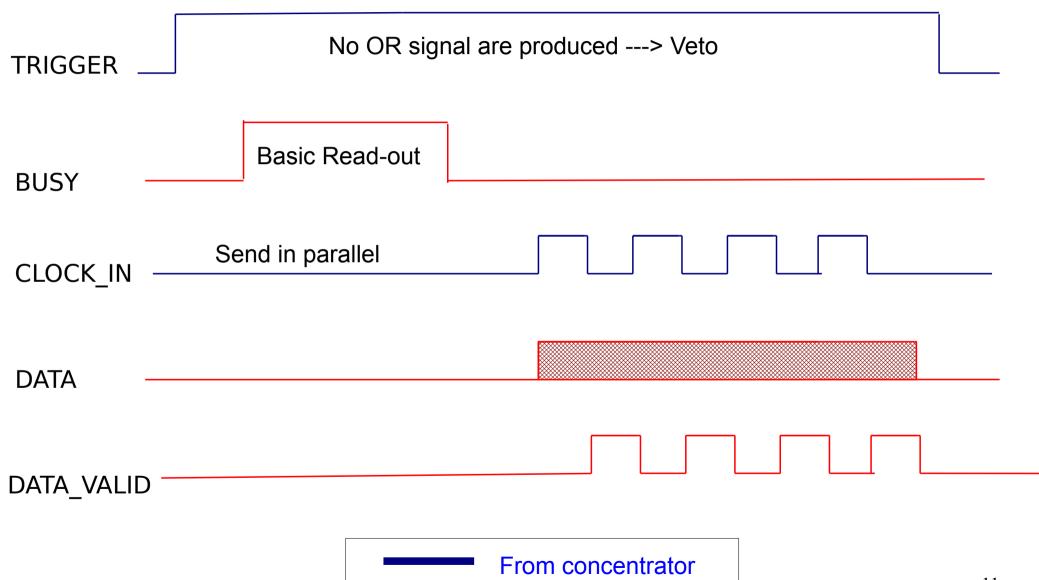

## Read-out process

From FPGA

# So my job in the next months will be...

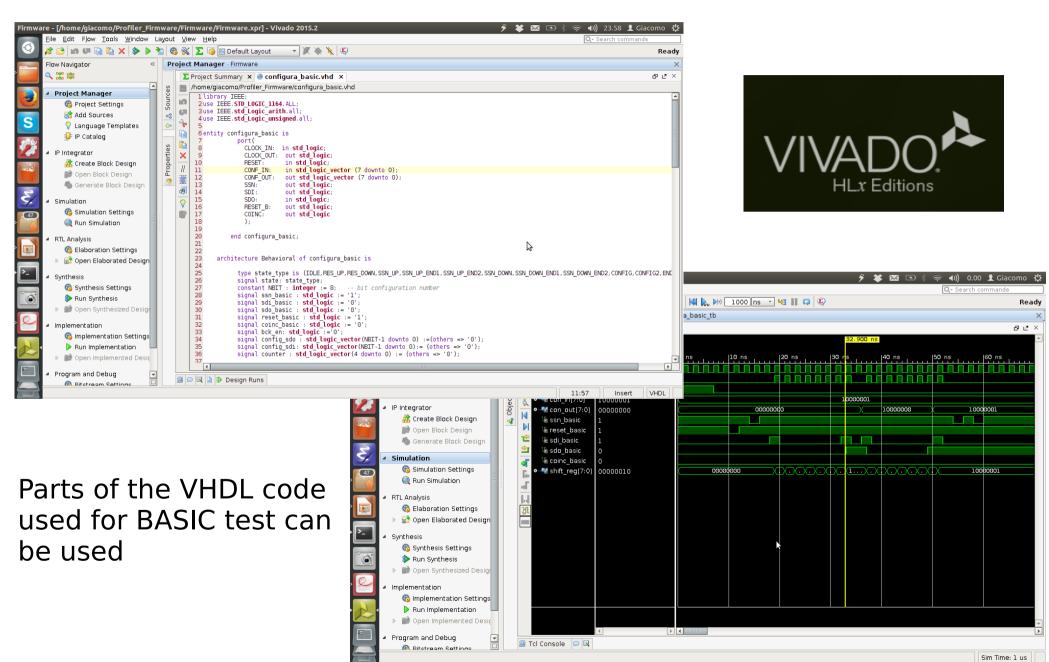

## ... programming the firmware

## Thank you for the attention