# Operational Experience with the ATLAS Pixel detector

Kerstin Lantzsch (Universität Bonn) on behalf of the ATLAS Collaboration

Pixel 2016, Sestri Levante, 05.09.2016

### Outline

### ATLAS Pixel Detector

- LHC performance and roadmap

- Detector parameters and upgrades

#### Operations

- Intrinsic limitations

- Operational challenges

#### Performance

### Outlook

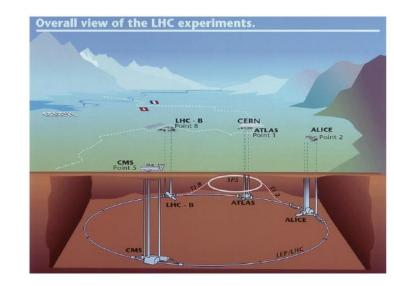

### LHC/ATLAS

#### LHC – Large Hadron Collider

design vs. 2016 conditions

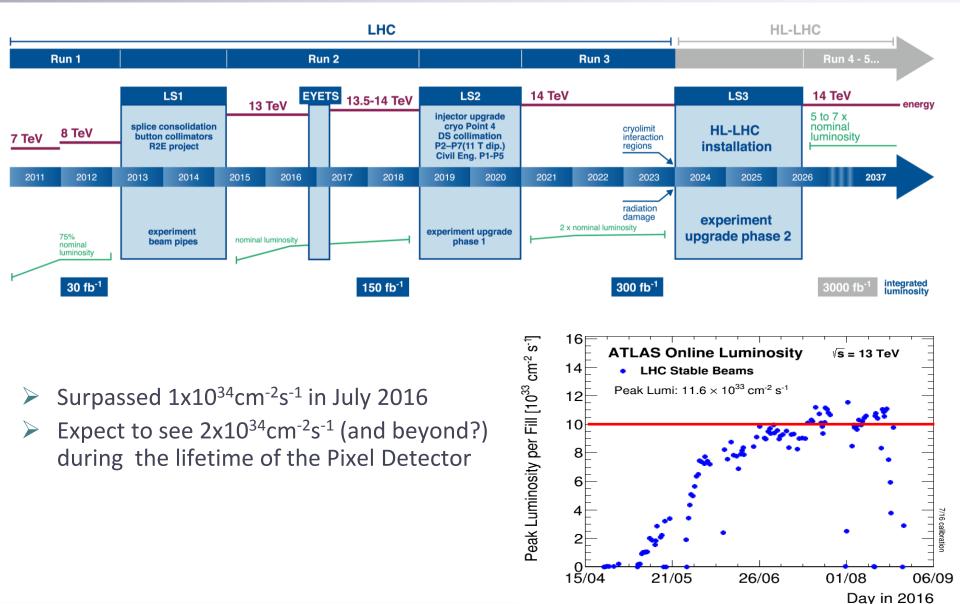

- 7 TeV nominal beam energy (6.5 TeV)

- > 1x10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup> nominal luminosity (1.2x10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup>)

- 2808 proton bunches per beam (2220b)

- 25 ns bunch spacing/40 Mhz

- First Long Shutdown (LS1) 2013/14 with repairs and upgrades to the accelerator and the experiments

#### ATLAS

#### Multi-purpose detector designed to

- Investigate the TeV scale

- Search for the Higgs boson

- Search beyond the standard model

- Supersymmetry, Mini-black holes, Leptoquarks, Extradimensions

- Make precision measurements of SM

#### Kerstin Lantzsch (University of Bonn)

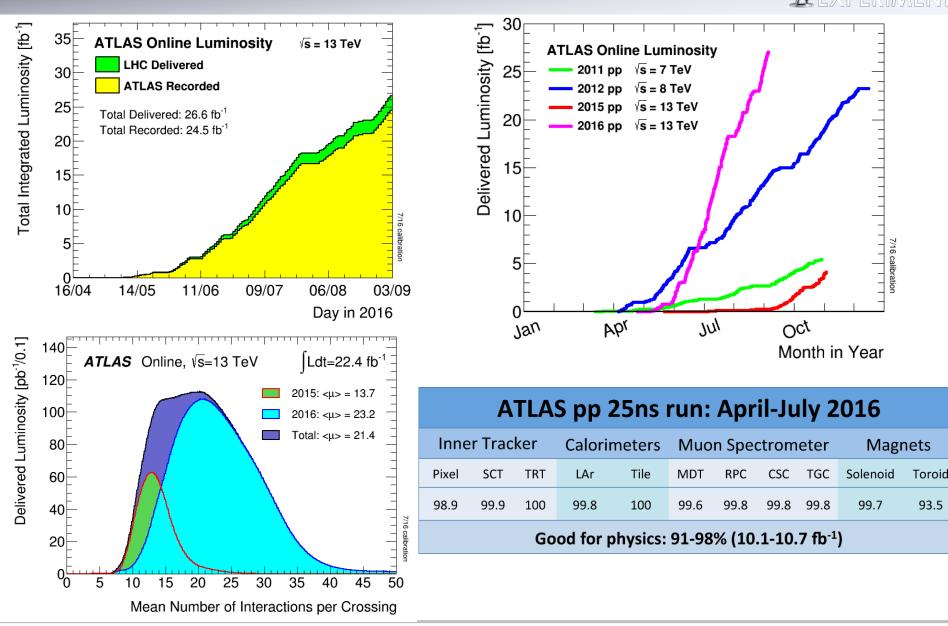

### LHC & ATLAS performance 2016

### LHC roadmap

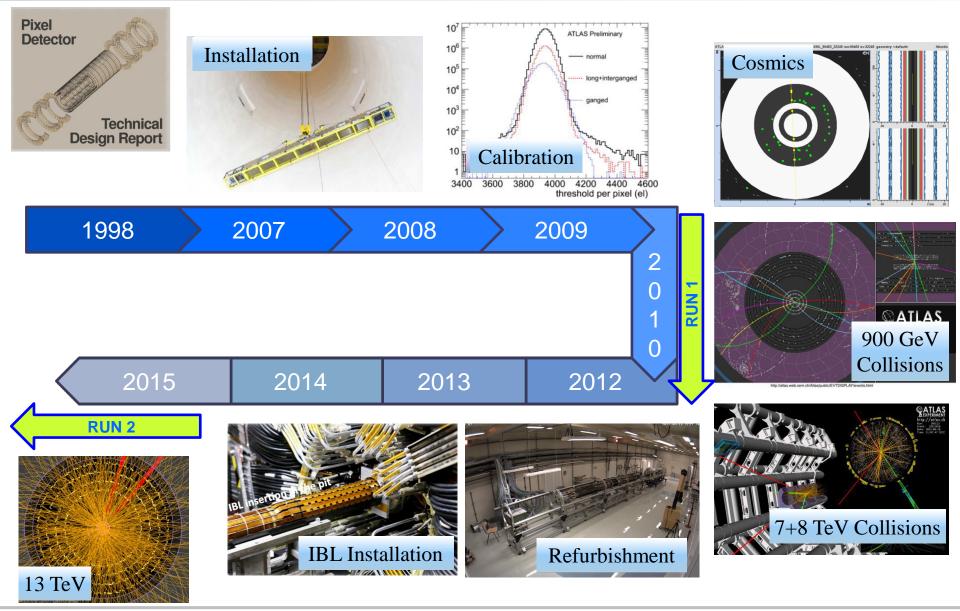

### Pixel Timeline

05.09.2016 ATLAS Pixel

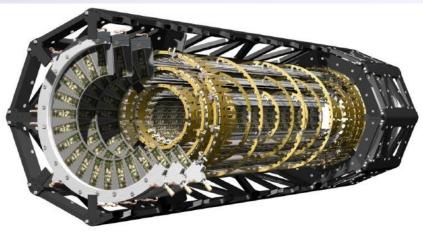

### The ATLAS Pixel Detector – before LS1

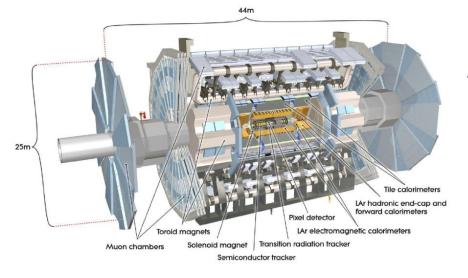

#### > 3 hit-system for $|\eta| < 2.5$

- 3 barrel layers

- 3 disks per end-cap

- > Resolution in r- $\phi$  < 15  $\mu$ m

- > 1744 modules, 80M readout channels

- Innermost barrel layer at 50.5 mm

- Radiation tolerance 500 kGy / 10<sup>15</sup> 1MeV neq cm<sup>-2</sup>

- Evaporative C<sub>3</sub>F<sub>8</sub> cooling

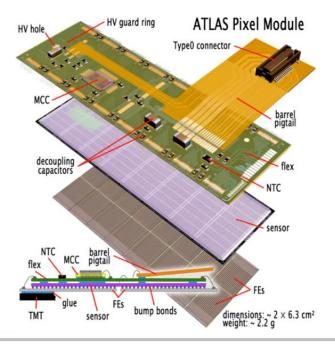

#### Sensor

- 250 µm thick n-on-n sensor

- > 47232 (328 x 144) pixels

- Typical pixel size 50 x 400 μm<sup>2</sup>

#### Readout

- 16 FE chips, 2880 pixels each

- Zero suppression in the FE chip, MCC builds module event

- Data transfer 40 160 MHz depending on layer

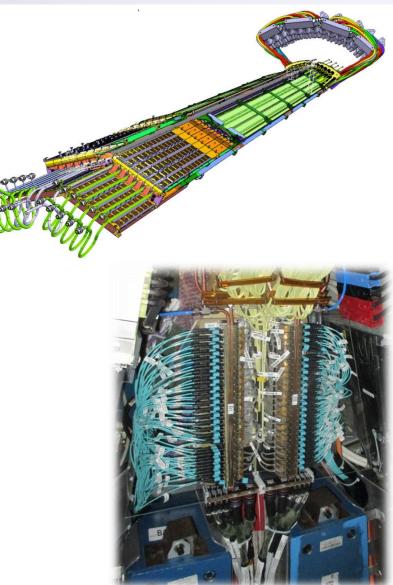

### LS1 upgrades: nSQP

**Pixel Detector extracted during LS1**

# Motivation for new Service Quarter Panels (LS1):

- Move on-detector opto-electrical transceivers (optoboards) to a serviceable location

- Allow later Layer 1 readout speed upgrade to 160 Mbit/s (add second line for Layer 1 modules data lines)

- While detector is on the surface: repair all accessible failures

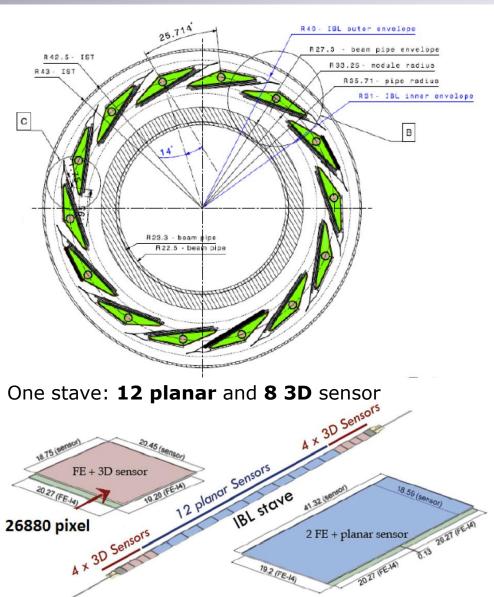

# LS1 upgrades: IBL

#### IBL a new inner most layer:

- With a new reduced beam pipe radius

- 14 staves inside a 10mm radius envelope

- New detector: sensor, FE, readout, cooling

#### Why?

- B-layer aging was anticipated

- Improvement of the tracking performance

**ATLAS** EXPERIMENT

05.09.2016 ATLAS Pixel

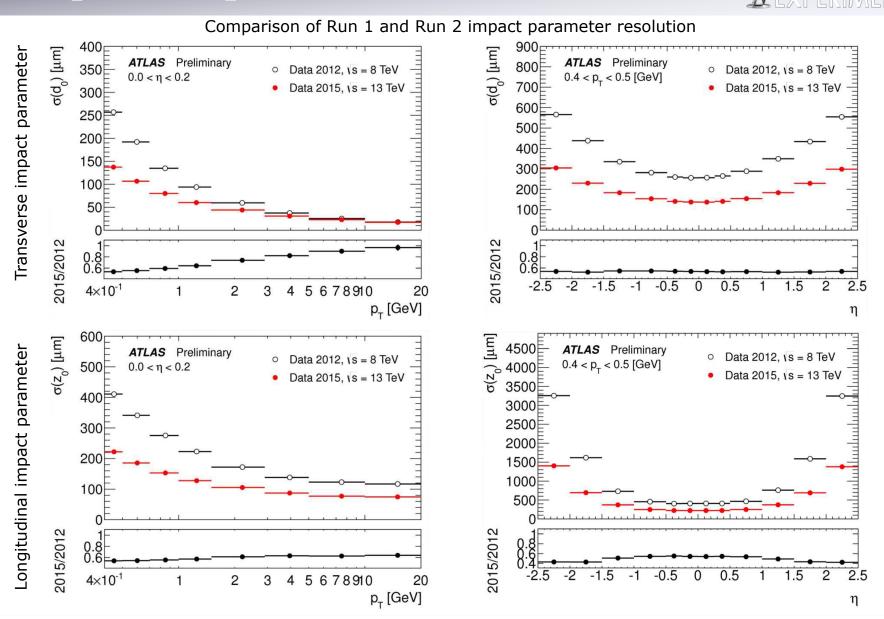

### Improved performance with IBL

05.09.2016 ATLAS Pixel

#### Kerstin Lantzsch (University of Bonn)

### **Detector** Calibration

Number of pixels

10<sup>7</sup>

10<sup>6</sup>

10<sup>5</sup>

10

$10^{3}$

10<sup>2</sup>

102000

2500

3000

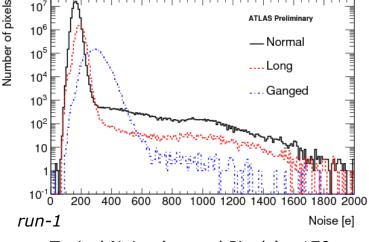

#### Performance is partly related to the detector calibration

#### **Typical Threshold/Noise**

Threshold: 3500 e Dispersion  $\sim$ 40 e-Module by module variation: few e<sup>-</sup>

3500

4000

Typical Noise (normal Pixels)= 170 e-

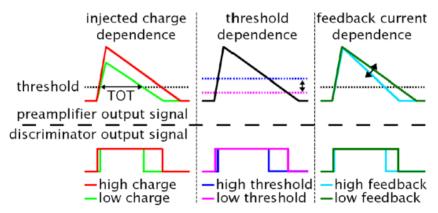

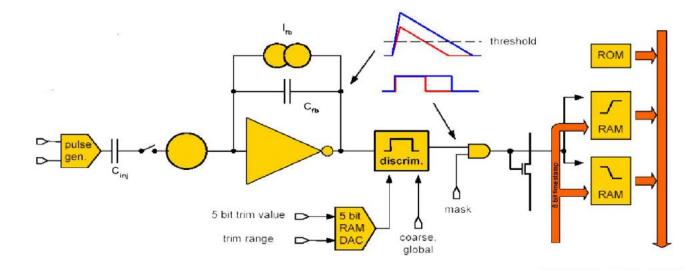

#### Time-over-threshold (ToT):

length of discriminator signal

- Measurement of the *deposited charge*

- Used to extrapolate analogue hit position

- ➢ Preamplifier-rise time can shift low ToT hits into the next time bucket (BC) → "Timewalk"

- Mechanism to recover time walked hits ("ToTdoubling"): copy low ToT hits to the previous BC for readout

- ToT usually tuned pixel by pixel to 30 BC @ 20ke

#### *ToT depends on: charge, threshold, feedback current*

ATLAS Preliminary

— Normal

.... Ganged

.... Long

4500

5000

550

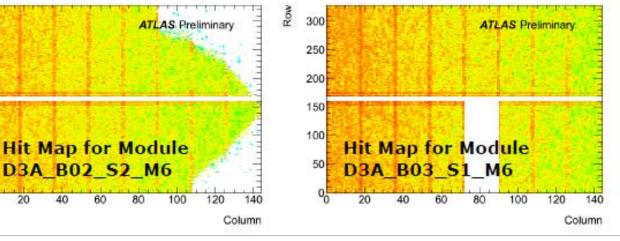

### Efficiency

#### Coverage after LS1

### **On-Detector sources of Efficiency Loss**

- $\geq$ Offline Calibration Loop to identify

- Inefficiencies related to dead channels, FE, Modules, Optical links, ...

Row

300

250

200

150

100

50

00

20

Noise

#### Kerstin Lantzsch (University of Bonn)

10<sub>E</sub> Pixel Disabled Modules [%] End of Run 1 9 ATLAS Pixel Preliminary After Re-installation 7.0% 7 6 5 4 4 3 2 1 0 6.3% 3.5% 2.0% 1.9% 1.4% 1.2% Disk Laver 2 Layer 0 Layer 1

# **Operational Limits**

Pixel built for Luminosity of 1x10<sup>33</sup> cm<sup>-2</sup>s<sup>-1</sup>, 100 kHz trigger rate, 50 Mrad / 1x10<sup>15</sup> 1MeV neq cm<sup>-2</sup> at LHC (B-Layer replacement was foreseen). Operation limits arise from these constraints, as well as general considerations.

#### Intrinsic to detector limitations:

- Bandwidth

- Buffer size limitations: FE and back-end

- $\succ$  Detector coverage  $\rightarrow$  related to detector granularity issues

- Tracking and reconstruction to deal with known holes

- Power and DCS limitation

- HV Leakage Current related to radiation damage or breakdown

- Power limitation and budget (may need to be adjusted with detector aging)

- FE and module losses in-run due to SEUs

- Requires module reconfiguration and causes dead time

#### **Other external factors:**

- Robustness of procedures and software

- Expertise for operation and calibration

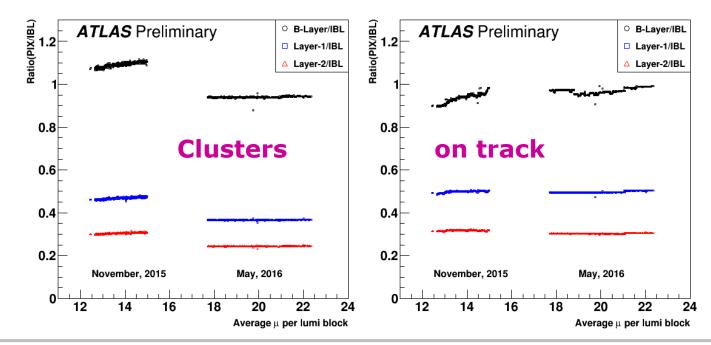

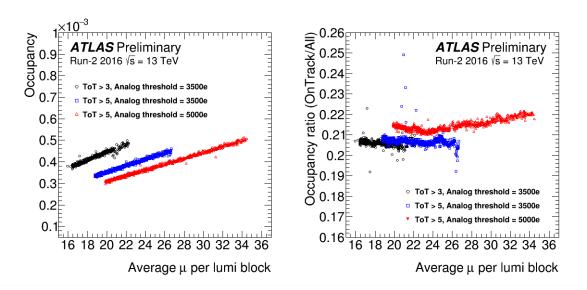

### Anticipation in 2016

Occupancy reduction given the increased luminosity in 2016

- Disable ToT doubling in all Pixel Layers

- Increase ToT cut to avoid reading out out-of-time hits

- IBL was unchanged

#### → Save ~20% occupancy, clusters on-track unaffected

05.09.2016 ATLAS Pixel

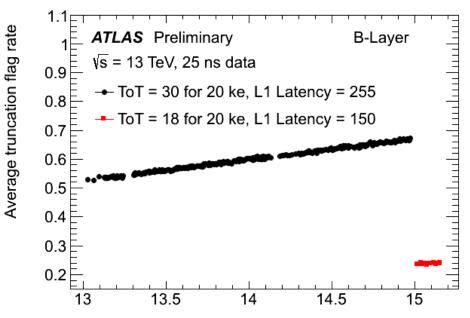

### B-Layer FE efficiency

- > No sign of efficiency loss in 2015 for B-Layer

- ➢ But with expected pile-up of 2016 up to 40 this would lead to uncontrolled level of truncation in the FE → truncation errors would saturate at 100%

#### Addressed by decreasing the FE Latency

- Buffer size latency 255 BC  $\rightarrow$  150BC

- Each hit will clear the FE buffer 100 BC earlier

- Retune ToT to keep the dynamic range, at reduced charge resolution

- → Truncation drastically reduced:

< 10% in 2016</li>

Average number of Pile-up in a given luminosity block

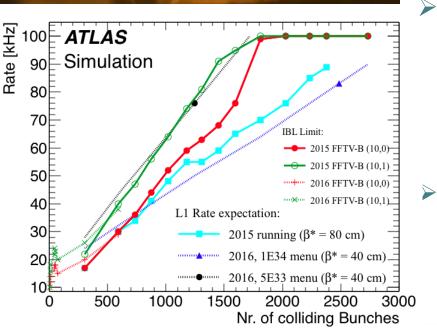

### Bandwidth

- - first signs already seen end of run 1 and also in 2015 → significant desynchronisation at high occupancy and trigger rate

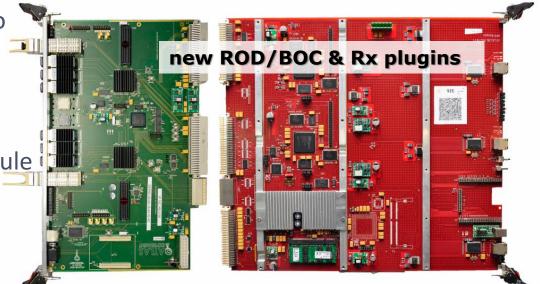

- Layer 2 Upgrade completed during 2015 YETS → bandwidth doubled to 80 Mbps, using IBL off-detector readout electronics

### Layer 1 Upgrade foreseen for 2016 YETS

- bandwidth will be doubled to 160 Mbps

- using Layer 2/IBL readout electronics

- one additional fiber per module to allow 2X80 Mbit/s was installed during LS1

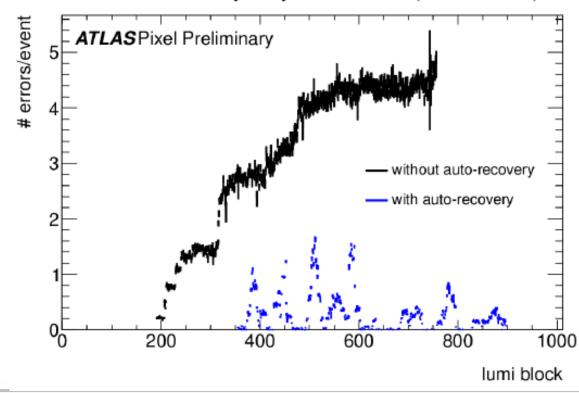

### SEU

- SEUs lead to local inefficiencies with various symptoms (Desynchronization, efficiency loss, LV current steps, ...)

- Recover by back-end and or module reconfiguration

- Effect is dominant in 2016 also for IBL

Modules affected by desynchronisation (Module level)

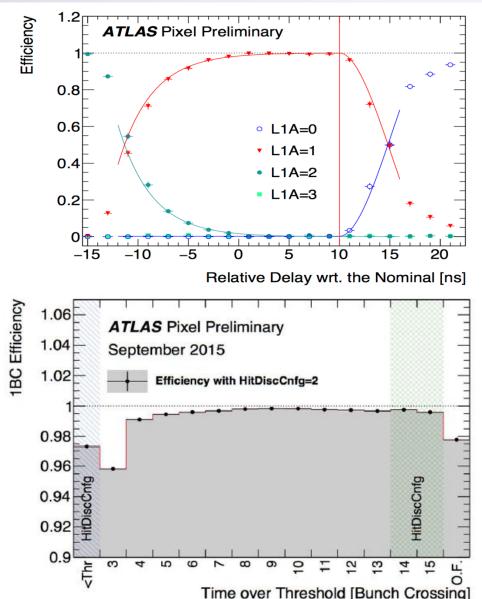

### **Detector** Timing

- Goal is to take data within 1 BC

- ➢ If timing not properly adjusted → inefficiencies

- Timing adjustment is done at the level of the module and FE granularity

- IBL is a new detector and fine tuning completed successfuly in 2015

- Fine tuning allows better 0.1ns

Pixel readout with 1BC Since September 2010

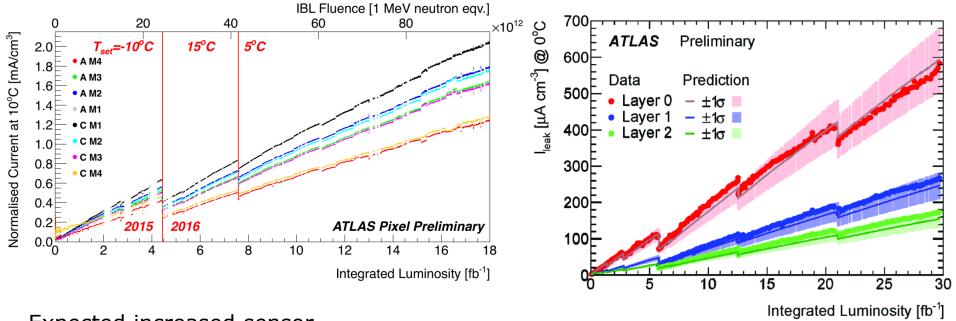

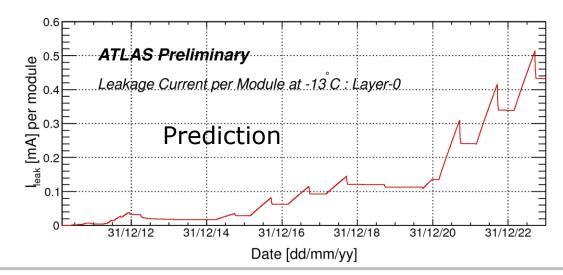

### Leakage Current evolution

Expected increased sensor current is regularly monitored for both Pixel and IBL

→ Power budget still comfortable wrt limitation

### Other Challenges

### Detector features and protection

- Wire bonding oscillation

- Mechanical distortion#

- FE LV current increase with TID

- Readout limitations

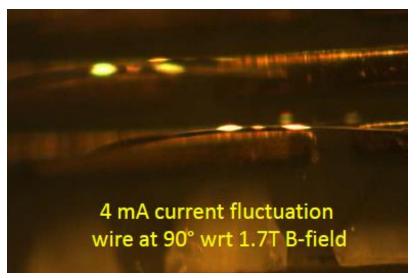

# IBL Wire Bond Oscillations

IBL wire bonds susceptible to some resonance frequencies during data taking

- Protection Scheme implemented into the readout chain for data taking and calibration

- Fixed Frequency Trigger Veto (FFTV): limiting the number of triggers in resonance region

- Trigger Veto is dependent on LHC filling scheme

- no rate limitation in 2015

- reviewed parameters in 2016 to avoid limiting rate while keeping the detector safe.

- ➢ Few occurrences in the experiment of fixed frequency trigger at 11 or 22 kHz → protection essential

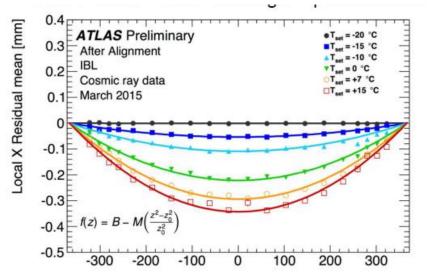

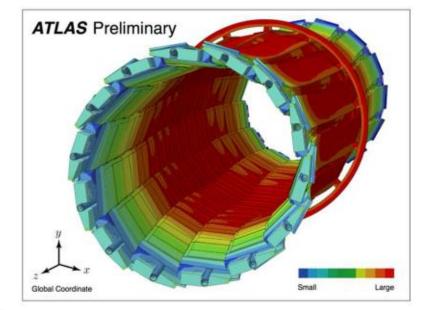

## **IBL** Mechanical Distortion

- During early cosmics run, temperature dependent distortion was observed in IBL, O(10um/K)

- Due to CTE mismatch between service bus and stave

- ➤ Impact on tracking performance

→ temperature dependent

alignment correction → Javier's poster

- large temperature excursion made a LB dependent correction necessary, implemented 2016

- Avoid temperature cycles inducing mechanical stress

- CO₂ cooling very stable and reliable

→ Bart's talk

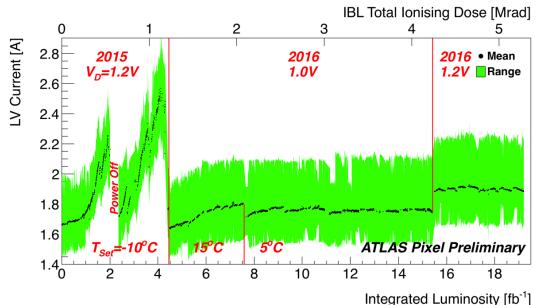

# IBL LV current drift → Karola's talk

Starting from summer 2015, IBL frontends started to show a drift in LV current and fast detuning of threshold and ToT.

- With increasing TID, LV currents exceeded values beyond safe operation parameters

- Switched off IBL for one run in October, and module groups when reaching critical level

- Detuning → regular monitoring and retune, phase space for tuning reduced

#### Task force was set-up:

Understand the cause of the issue + Lab measurements were essential to drive the operation conditions + Assessed the impact of running IBL warm for one year

In 2016 the increased peak luminosity for the same detector condition would have led to operational issue...

The recommendations were:

- Higher temperature

- Lower digital supply

### B-Layer Limitation in 2016

- In Pixel B-Layer, bandwidth issues were not foreseen before a factor of 2-3 higher occupancy

- In 2016 readout problems were already observed at a luminosity of 1x10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>

- Source was identified as:

- LHC beam is not uniform: up to 30% fluctuation between bunch crossing ID

- Readout is designed for average data rates: large events can cause problems

- Mitigation:

- Occupancy reduction: TOT cut and higher analog threshold (impact on tracking limited)

- Firmware improvements

- B-Layer is working stable since then

- ATLAS tracking at Run-2 significantly improved with IBL as new innermost Pixel layer

- Good performance seen since beginning of run 2 for IBL and Pixel

- Anticipated a number of limitations, successful changes to the detector configuration and hardware in view of increased luminosity

- Unforeseen challenges addressed and overcome

- Approaching stable operation for run conditions beyond LHC design luminosity

### BACKUP

### ATLAS Pixel Frontend Chip

#### **Pixel Cell**

- Amplifier with adjustable constant current feedback

- Discriminator with 7-bit threshold adjust

- Circuitry to measure *Time over Threshold* (ToT)

- Possibility for analogue and digital test injection

#### **End Of Column**

- Hit storage during Level-1 trigger latency

- 64 memory buffers for each column pair of 2 x 160 pixels ("EoC Buffers")

- Hit data: pixel ID + timestamp + ToT

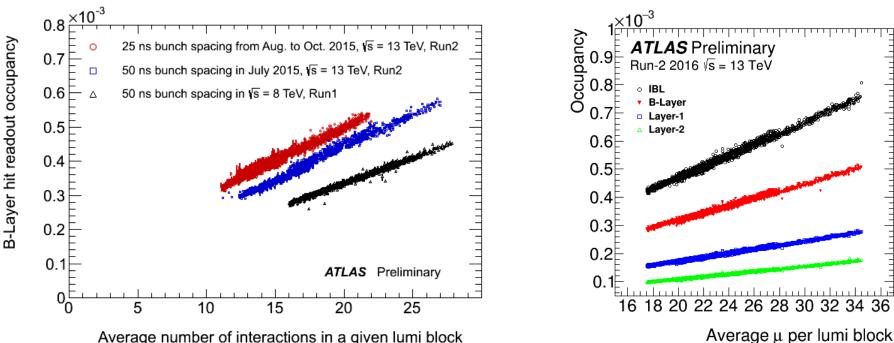

### Occupancy vs Pileup

Average number of interactions in a given lumi block

#### **Run 2:**

- additional material

- 25 ns operation

- increasing target luminosity