## A new Data Acquisition System for the CMS Phase 1 Pixel Detector

Andreas Kornmayer on behalf of the CMS Pixel DAQ WG

#### CERN

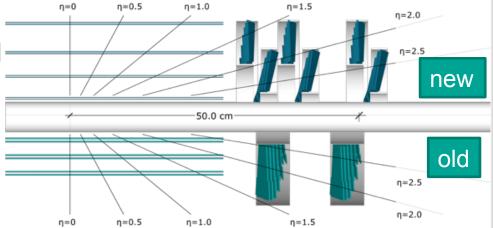

## The CMS Phase 1 Upgrade in a Nutshell

Motivation:

- Increase of instantaneous luminosity until Long Shutdown 3

- Higher pile-up, higher track density and higher occupancy on  $\rightarrow$ detector

- Higher data rates, old readout chips (ROCs) become inefficient  $\rightarrow$

- During an extended YETS 2016/2017 the entire CMS Pixel Detector is being replaced and upgraded

- one additional layer in barrel (BPIX) and forward region (FPIX), gives a 4<sup>th</sup> point for vertex reconstruction

- number of channels increases from 66M to 123M

- new digital readout scheme (PSI46dig + PROC600)

- $CO_2$  cooling

- reduction of material budget

More info in talk from Vittorio Raoul Tavolaro, "The Phase1 CMS Pixel detector upgrade"

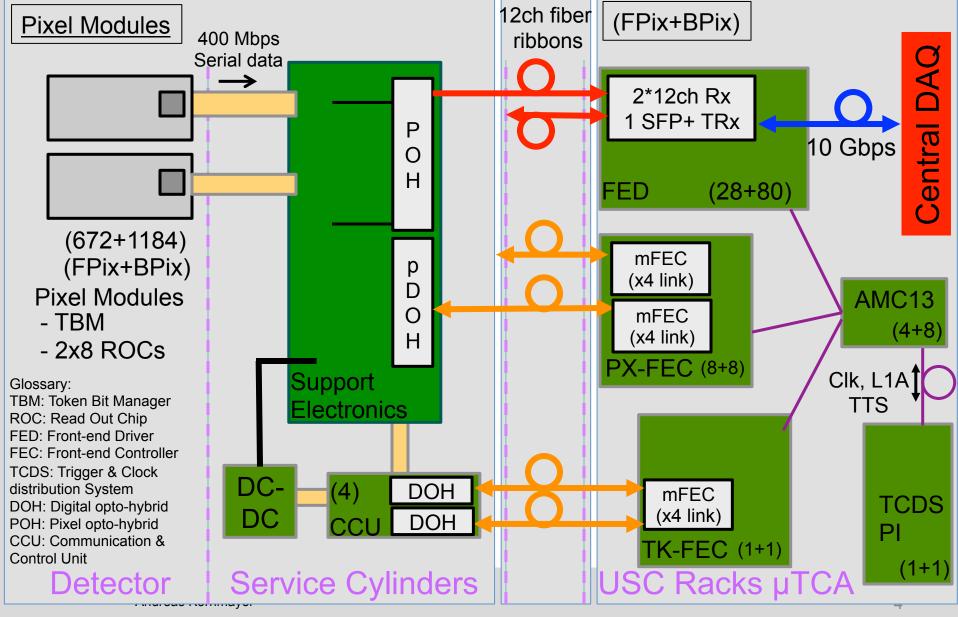

### System requirements for the new Pixel DAQ

- digital 400 Mb/s readout scheme

- 2x number of readout channels (1856 modules, 2368 links)

- increased data rate per link due to improved front-end

- increased number of control links

- VME parts out of production

→Upgrade of the Front End Driver (FED)

→Upgrade of the Front End Controller (FEC)

## **Readout architecture**

## The Phase 1 Pixel FED and FECs

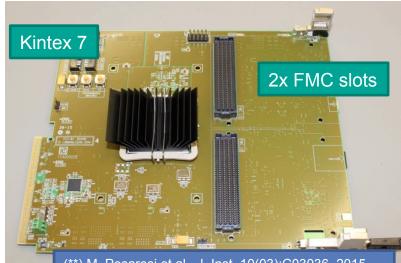

### FC7 board

- full size, double width µTCA AMC

- common standard in CMS (TCDS, HCAL, CT-PPS)

- Kintex 7 FPGA

- 4 GB DDR3 RAM for data buffering

- 12 high speed links to backplane (10Gb/s)

- 2 FMC (FPGA Mezzanine Card) slots

→ decide flavor of card (FED or FEC)

(\*\*) M. Pesaresi et al., J. Inst. 10(03):C03036, 2015.

## The Phase 1 Pixel FED and FECs

### FC7 board

- full size, double width μTCA AMC

- common standard in CMS (TCDS, HCAL, CT-PPS)

- Kintex 7 FPGA

- 4 GB DDR3 RAM for data buffering

- 12 high speed links to backplane (10Gb/s)

- 2 FMC (FPGA Mezzanine Card) slots

→ decide flavor of card (FED or FEC)

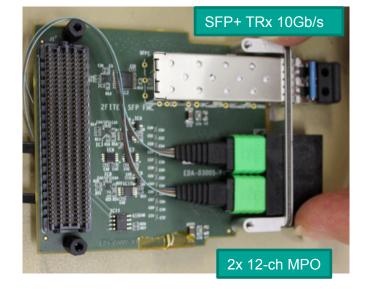

### To make it a FED:

- 24 optical input channels

- 2 FITEL 12 channel optical receivers, optimized for the 400Mb/s optical signal at 1310nm

- 1 DAQ output

- SFP+ 10Gb/s transceiver for S-Link Express DAQ output to CMS Central DAQ

### Firmware:

Decode incoming data links, detect possible errors, build events, transfer data to central DAQ

## The Phase 1 Pixel FED and FECs

# CERN

### FC7 board

- full size, double width µTCA AMC

- common standard in CMS (TCDS, HCAL, CT-PPS)

- Kintex 7 FPGA

- 4 GB DDR3 RAM for data buffering

- 12 high speed links to backplane (10Gb/s)

- 2 FMC (FPGA Mezzanine Card) slots

→ decide flavor of card (FED or FEC)

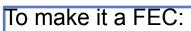

- Two FMCs equipped with low-speed (1Gb/s) optical transceivers

- 8 SFPs per FMC

- Two flavors of FECs, but hardware fully identical Firmware defines FEC flavor

- Firmware: Receives configuration, program front-end (Pixel FEC) or service electronics (Tracker FEC), send control signals (clock, trigger, resets...)

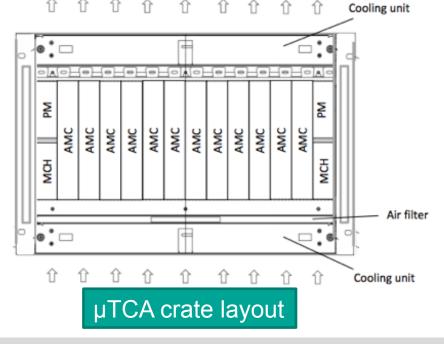

## A single µTCA crate

- Can hold up to 12 full size AMC cards

- Two redundant power supplies

- 1Gb/s Ethernet network access to all cards through MCH (MicroTCA Carrier Hub)

- Additional AMC13, custom made MCH like card, to distribute clock and trigger signals over crate backplane (CMS specific design)

### Full system layout

Last update

ID

56 55

53

52 51 50

56

2 June 2016 by JT/KG

- 12 µTCA crates in 3 racks to hold all components of the DAQ backend.

- 108 FEDs

- 18 FECs

- + spares

- Separated into 1 rack for FPIX and 2 racks for BPIX

- Powered by AC/DC converters

- Patch panels for 12-fibre optical cables coming from the detector (MPO connectors)

Contents S1G01 - FPIX Units RackWiz I ID Units Contents S1G03 - BPIX BackWiz ID | Units Contents S1G04 - BPIX 1 2 3 4 5 6 7 8 9 10 11 12 13 14 2 3 4 5 6 7 8 9 10 11 12 13 14 56 55 54 53 56 55 Turbine Turbine Turbine 4 54 53 52 51 50 49 1 52 51 50 49 48 47 46 45 44 43 42 41 40 48 BPIX Near BPIX Near 8 PIX Near 47 46 45 41 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 39 FPIX Far + BPIX Far BPIX Far + 38 37 36 35 33 32 30 8 BPIX Near **BPIX** Near 29 28 27 26 Cable Organize Cable Organiz 25 24 23 22 21 20 19 18 17 21 20 **FPIX Far** 8 **BPIX** Far **BPIX Far** 19 18 17 able Organize Cable Organize Cable Organiz 16 15 14 13 12 11 10 9 8 eat Exchang 1 Heat Exchange 16 Heat Exchan 15 2 2 Air Deflector Air Deflecto Air Deflecto 13 96x MPO patch panel 96x MPO patch panel 96x MPO patch panel 2 12 Cable Organizer Cable Organize 11 Cable Organi 1 10 96x MPO patch pane 2 96x MPO patch pane 96x MPO patch pa able Organ 1 Cable Orga 2 2 96x MPO patch panel 96x MPO patch pane 96x MPO patch pane 1 4 3 2 1 Cable Feedthrough Cable Feedthroug Cable Feedthroug

Rack layout for CMS service cavern

56

56

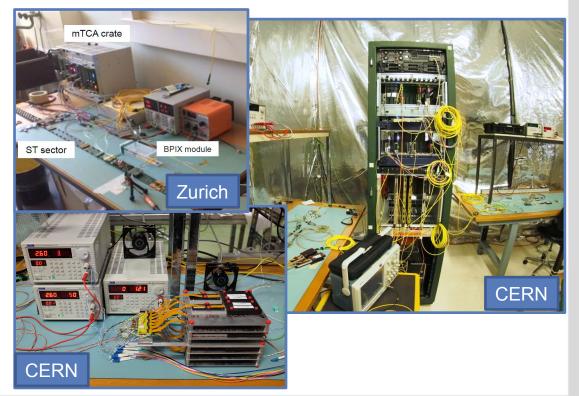

### System tests: In the laboratory

- Firmware and software development still ongoing

- Small scale systems used for development and testing of final detector parts

- $\rightarrow$  Advances development and helps finding bugs

Integration centers using µTCA: @CERN: Firmware development and general hardware tests, reception tests of arriving detector parts

@Fermilab: Final checkout of FPIX detector before being shipped to CERN for installation in CMS

QZurich: Test of the optical components of the service cylinders, integration tests for BPIX

## System tests: Getting a little bigger

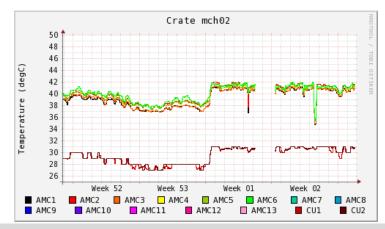

- A soak test facility has been set up at CERN

- Rack layout identical to the final setup (3 racks with 4 crates each)

- Will be used to test all production parts before they are installed in the CMS service cavern

### Soak test:

Firmware load and power cycling of FEDs & FECs → Test for infant mortality while stressing the components

- Measurement of optical receivers using the FED tester, a front-end emulator board

- Development stage for a crate monitoring system (temperatures, voltages, currents)

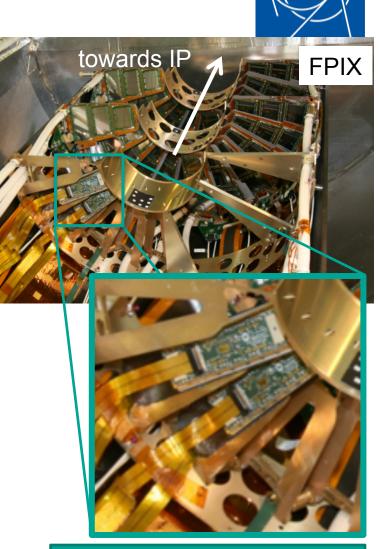

## System tests: In the CMS detector

### Phase 1 Pilot Blade

- 8 prototype pixel modules installed in CMS, right behind the two current FPIX disks

- Full readout chain as is intended for the upgraded detector

- Readout chips & TBM chips

- DC-DC power converters

- Portcards and CCU cards

- Readout in legacy VME and µTCA possible

- All components can be tested under realistic conditions within CMS

- Test integration of new Pixel DAQ with central systems of CMS

Two upgrade pixel modules

## System tests: In the (near) future

- Only small scale systems with low data throughput have been tested until now

- Before installation the system has to be fully qualified also for the highest expected data rates

- Stress test system:

- → Connect a fully loaded crate (10 FEDs), emulated data patterns are send to the central DAQ processor of CMS

- → Test that the new detector DAQ does work with all other sub systems of CMS to ensure a smooth start-up in 2017

- $\rightarrow$  Ensure and show the readiness of the upgrade DAQ

### **Summary and Outlook**

- A new DAQ system based on the µTCA standard has been designed and is currently under development to accommodate for the new digital readout scheme and higher data rates coming from the front-end.

- FEDs and FECs based on the FC7 μTCA board have been produced.

- Several test stands for hardware and firmware development and final detector checkout have been setup.

- Integration tests of the system into the full CMS experiment are planned for this fall.

- Once the current run period has ended the old pixel detector and its corresponding VME based readout system will be fully replaced by the new Phase 1 Pixel detector and the presented DAQ system.