# OPERATIONAL EXPERIENCE OF THE ALICE PIXEL DETECTOR

#### Annalisa Mastroserio

Università degli Studi di Bari and INFN (Bari)

On Behalf of the ALICE Collaboration

### Outline

- ALICE Silicon Pixel Detector

- From Run 1 to Run 2

- Operation after long shutdown

- Detector status

- Calibration

- Trigger performances

- Online Background rejection

- High multiplicity

- Double gap diffractive

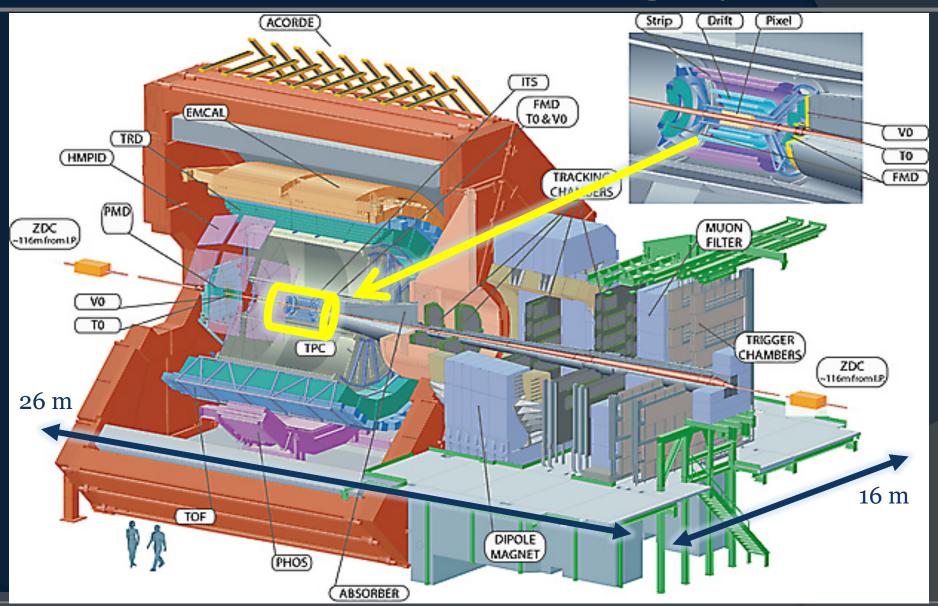

# ALICE Inner Tracking System

### ALICE Silicon Pixel Detector SPD

#### **Design goals:**

- Primary and secondary vertices

- Contribution to tracking

- Contribution to ALICE Lo Trigger

#### **Detector characteristics:**

- spatial precision:

- 12 μm in rφ and 100 μm in z

- Pixel size :425μm x 50μm (z x rφ)

- material budget: ~1.1% X₀ per layer

- Readout time: 256 μs

- power consumption: 1.35 kW (0.5 W/cm<sup>2</sup>)

Minimum distance to the beam pipe: 5 mm

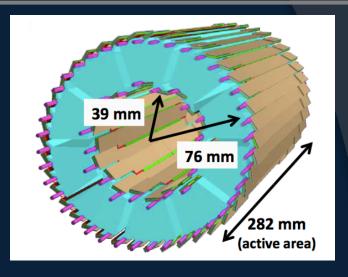

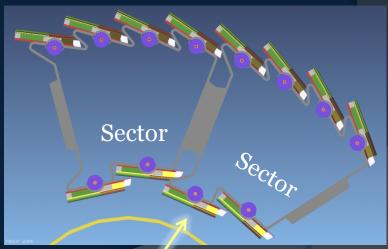

### ALICE Silicon Pixel Detector SPD

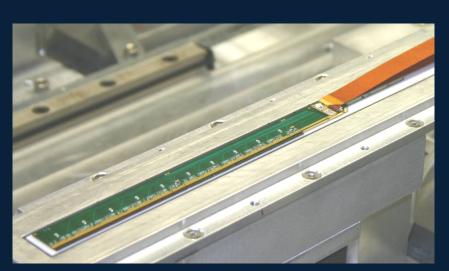

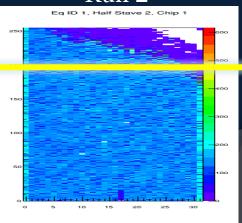

Smallest fully functional block: Half Stave

Detector segmentation :

10 Sector

120 half-staves (40 inner +80 outer)

10 pixel chips per half stave

> 1200 chips (400 + 800)

Each chip has 256 x 32 pixels

$\triangleright$  9.83 x 10<sup>6</sup> pixels in total

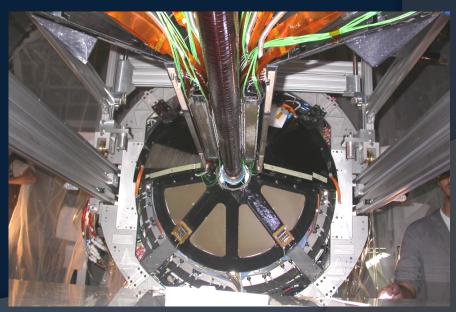

# SPD integration in ALICE

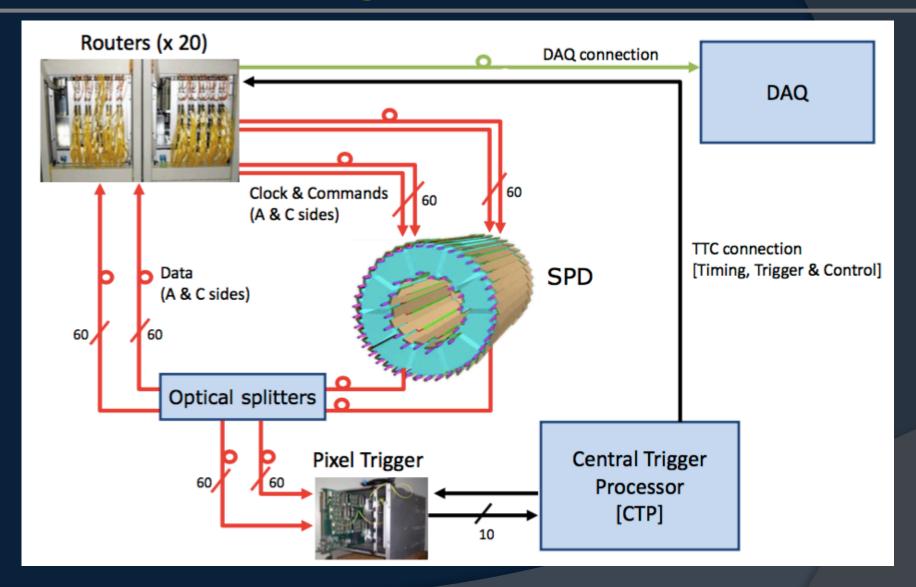

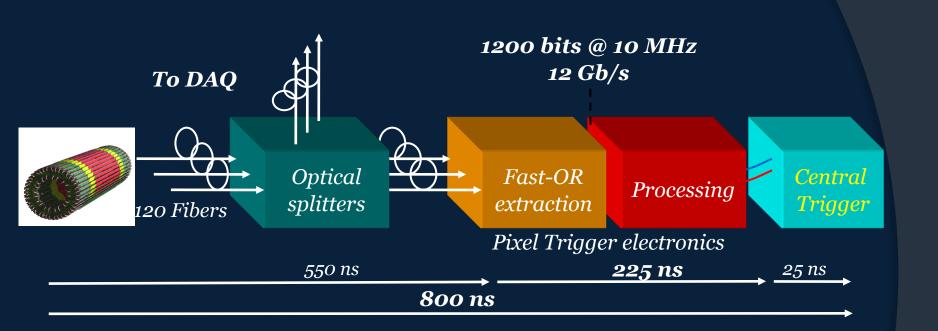

# Pixel Trigger Schematics

- ☐ Basic information : FastOr bit per chip TRUE if at least one pixel is fired

- □ 1200 FastOr bits per event sent to the Pixel Trigger Electronics for processing

- □ 10 programmable algorithms based on 1200 bits and boolean logics return 10 boolean responses to CTP

### From Run1 to Run2

- End of Run1 : March 2013

- Long Shut down 1

• Run2:

- Recommissioning with beams in May 2015

- Energy increase up to 6.5 TeV per beam

- 25 ns bunch spacing in trains

- Instantaneous luminosity up to 5 Hz/ub

- Campaign for minimum bias and rare triggers at low pile up  $(\mu)$

- Pb-Pb collisions in December 2015

- P-Pb collisions foreseen in December 2016

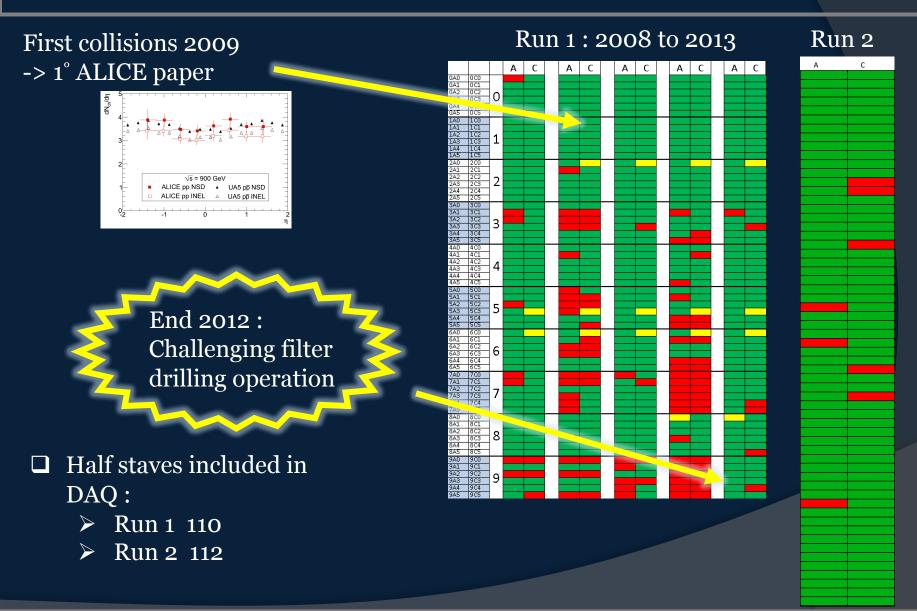

### Operational half-staves from Run1 to Run 2

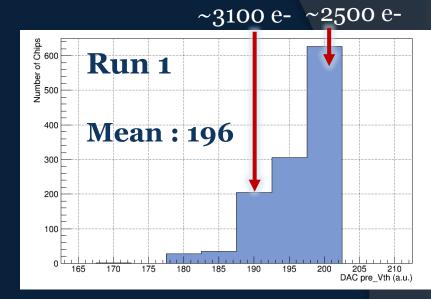

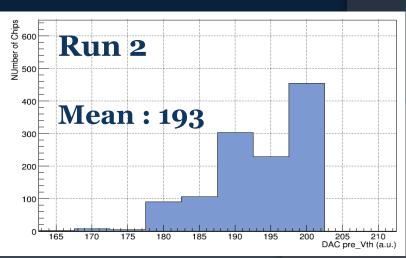

### Detector Configuration

- ☐ FEE configuration similar to Run 1

- Threshold campaign

- Timing campaign

- ☐ Same noisy pixel fraction as in Run 1 ≈10-

- ☐ Change of the latency of the trigger signals from the CTP lead to a timing campaign that aimed to match the internal data readout delay with the arrival of the trigger. A mis-match between the Fast-OR and the pixel data was found and solved.

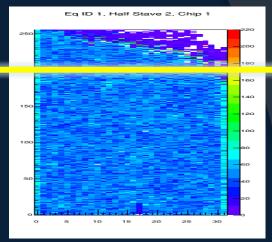

### **Detector Configuration**

- Expected increase of dead areas

- Switching on and off HV => thermal cycles that in turn cause the detaching of the readout chips from the sensor

- Dead pixels are due to missing bump bondings at the 4 corners of the chip. Other contributions are from

- Dead pixel from construction

- Inefficient pixels

- Inefficient and dead pixel in hs in DAQ :

- □ Run 1 (2013) 2%

- □ Run 2 (2015) 4.5%

#### Run 1

#### Run 2

### **Detector Operation**

- Same as in Run 1:

- Configuration done once, then tuned. Further checks only after a technical stop.

- Noisy pixels rarely appear. Usually very few in a run (<3)

- The detector configuration parameters of front-end and trigger algorithms are checked automatically at each run by means of the Alice Configuration Tool (ACT)

- Same working conditions in pp and PbPb also in Run 2

- New higher luminosity regime in pp

- Smooth operation of the detector during Run 2

- Loss of configuration of one hs or few chips during data taking

- Data format errors (missing header/trailer)

- Fraction of Phyiscs Runs with SPD :

- Run 1 (2013) = 86%

- Run 2 = 93%

- EOR caused by SPD :

- Run 1:2%

- Run 2: 4%

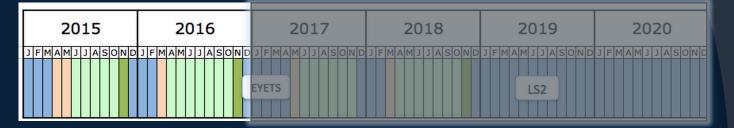

### New Feature in Run 2

2015

2016

- □ New trigger classes used in ALICE as Lo from Pixel Trigger :

- Online Background rejection studies

- High Multiplicity studies

- Double gap diffractive studies

- New firmware deployed

Pixel Trigger electronics

#### Pixel trigger I/O

- ► Input : 1200 bits

- Output : 10 programmable algorithms

# Pixel Trigger Algorithms

| Output | Name                                                         | Algorithm                                          |

|--------|--------------------------------------------------------------|----------------------------------------------------|

| 1      | Minimum Bias                                                 | $(I+O) \ge th_0$ and $I \ge th_1$ and $O \ge th_2$ |

| 2      | High Multiplicity 1                                          | I≥th₁ and O≥th₂                                    |

| 3      | High Multiplicity 2                                          | I≥th₁ and O≥th₂                                    |

| 4      | High Multiplicity 3                                          | I≥th₁ andO≥th₂                                     |

| 5      | High Multiplicity 4                                          | I≥th₁ andO≥th₂                                     |

| 6      | Generalized topological trigger with programmable acceptance | Based on tracklets                                 |

| 7      | Less Than                                                    | I≤th₁ and O≤th₂                                    |

| 8      | Spare background                                             | $O \ge I + offset_{Outer}$                         |

| 9      | Background                                                   | $(I+O) \ge th_{(Inner+Outer)}$                     |

| 10     | Cosmics                                                      | Selectable coincidence                             |

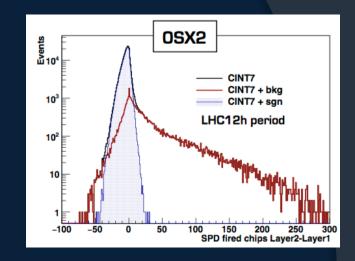

### Online background estimator (2015)

#### Main idea:

- ➤ Bunch-Bunch collisions expected to have equal number of Fired Chips in the two layers. The event distribution peaked around difference in Layer1− Layer2 equals to 0

- ➤ Bunch-Gas collisions expected to have large difference in the number of Fired Chips in the two layers

Background trigger algorithm:

I > O + Threshold

Recent studies performed on data taken in 2012 prove that background can be efficiently separated

• E.g. with a Threshold = 20 the background reduction is ~40%

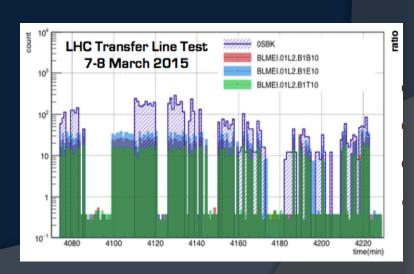

LHC Transfer Line Test (7-8 March) beam quenched on the TDI : correlation found between BLM and oSX2

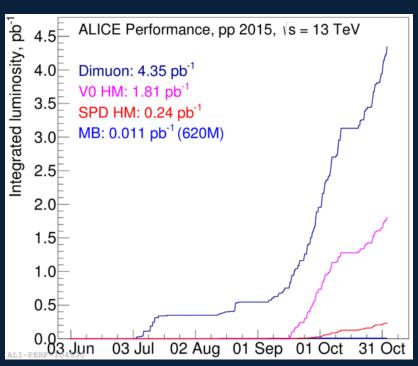

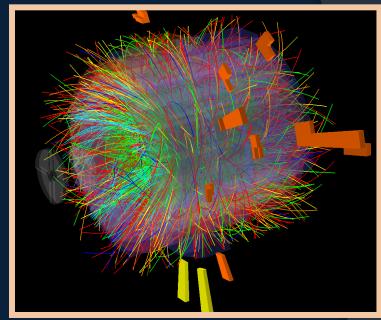

# High Multiplicity Trigger (2015)

I≥0 and O ≥ 70

High background

**p-p** @ 13 TeV

High multiplicity pp event

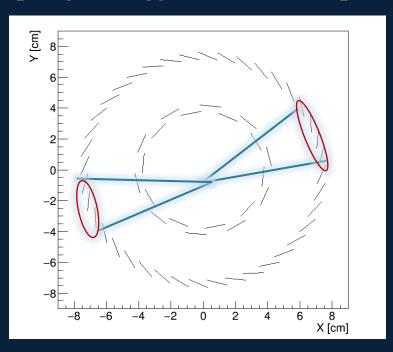

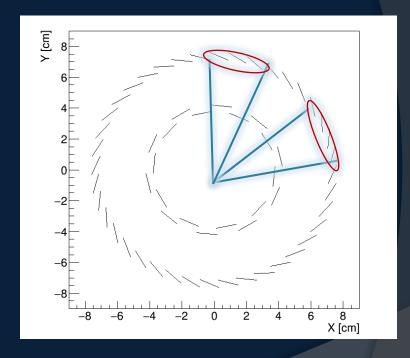

# Topological Trigger (2016)

Tracklet: correlation in  $r\phi$  between chips in the inner layer and chips in the outer layer

Topological trigger: based on chip inside cones

Input parameters foresee also:

- opening angle between two tracklets

- Number of tracklets (min and max)

Under study

## Summary

- All leftover issues from Run 1 solved during Long Shutdown

- The re-commissioning of the detector and the new data taking went smoothly. The number of half-staves in read-out is the same as in Run1

- Exploitation of new trigger capabilities such as online background rejection, High Multiplicity, topological trigger for double gap diffractive events

- Detector proved to be robust providing key data and trigger information since the very beginning of LHC running

- The very good performance of the SPD during data-taking provides a fundamental information to many physics analysis that result in published papers

# Backup

## Activities during LS1

- Readout electronics issue in Run 1: high busy time

- problem in the firmware identified and solved

- New VME controller for crates with readout electronics

- replaced National Instruments controller with CAEN controller

- Migration of DCS software

- New operating systems installed in machines at P2

- Old PVSS software for User Interface moved to the new platform WinCC

- Cooling Intervention : further improvement!

- Issues with a pump at the cooling plant in Run 1 solved by changing the pump with a gear pump. Good stability since its replacement in March.

- Replacement of broken compressor

- 4 new HV boards