# OVERVIEW DEL PROCESSORE FAST TRACKER PER ATLAS

G. VOLPI - UNIVERSITÀ ED INFN DI PISA

PER CONTO DELL'ESPERIMENTO ATLAS ED IL GRUPPO FTK

#### INTRODUZIONE

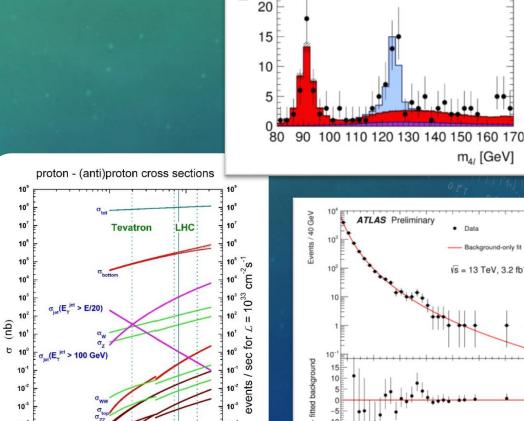

- ATLAS ha raccolto numerosi successi durante il Run I, rafforzati dai primi dati del Run II

- Scoperta del Bosone di Higgs e prime misure delle sue proprietà

- Misure di altissime precisione sui più importanti processi dello SM

- Limiti stringenti sui modelli di Fisica oltre lo SM

- Le misure sono in sostanziale accordo con lo SM, ma discrepanze appaiono e punti di interesse sono presenti

- Necessario raccogliere campioni abbondanti di fenomeni rari o non ancora accessibili

- Esplorare tutti i meccanismi di produzione del Higgs e particelle attese dalle sue estensioni

- Per sfruttare al meglio le potenzialità dell'esperimento è indispensabile mantenere e migliorare la capacità di identificare fenomeni interessanti

- Il livello di complessità delle collisioni è infatti cresciuto già all'inizio del Run II, con la prospettiva di maggiore pileup del corso del run

$\alpha$

(s = 8 TeV: Ldt = 20.3 fb

ATLAS-CONF-2015-081

m<sub>41</sub> [GeV]

vs = 13 TeV, 3.2 fb

E (TeV)

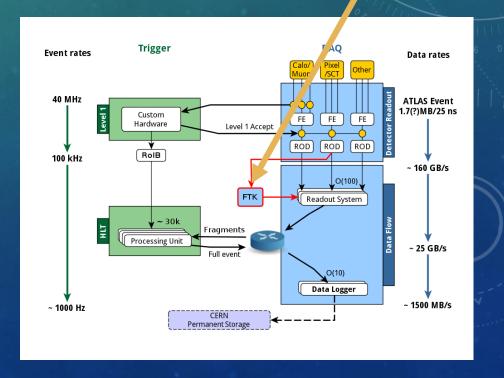

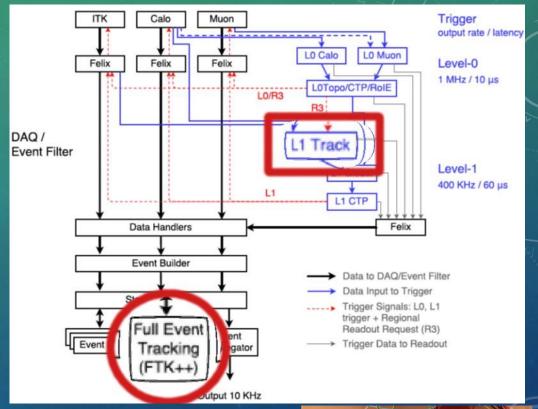

#### EVOLUZIONE DEL TDAQ DI ATLAS

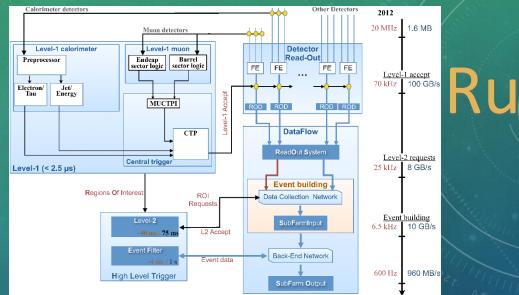

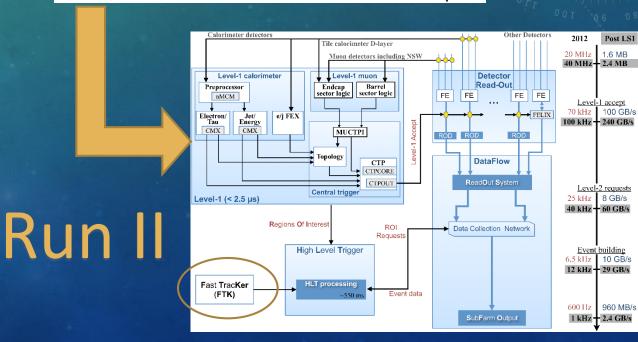

- Nel Run I ATLAS l'infrastruttura di ATLAS per il Sistema di DAQ è stato basato su un trigger a 3 livelli

- Primo livello basato su HW dedicato e basato sull'informazione dei calorimetri e dei rivelatori a muoni

- Livelli successive basati su CPU con risorse organizzate in 2 computing farm distinte

- Level-2 e Event filter

- Durante il LS1 l'infrastruttura ha subito dei mutamenti

- La divisione tra Level-2 ed Event Filter è sparita. consentendo di avere algoritmi con maggiore latenza

- L'infrastruttura di rete è migliorata, garantisci maggiore potena e flessiilità

- Miglioramenti nelle performance del software del HLT dopo un'intensa campagna di ottimizzazione

- Previsto l'inserimento di un processore HW per il tracciamento: FTK

- Argomento principale di questa presentazione, fondamentale il contributo italiano

#### L'USO DEL TRACCIATORE NEL TRIGGER

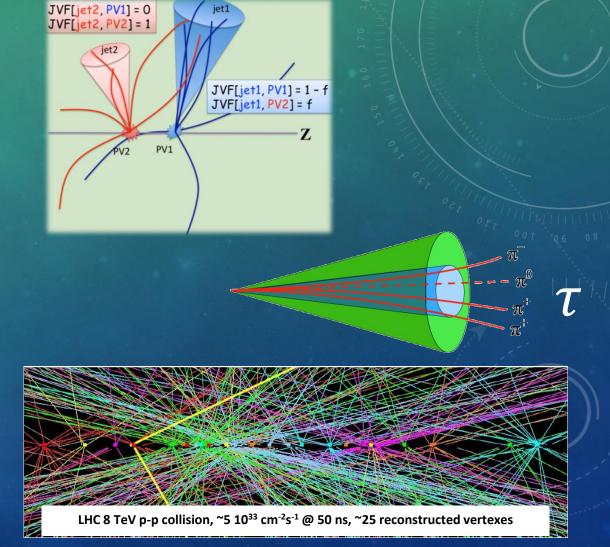

- Le tracce sono uno strumento fondamentale per identificare processi chiave per SM e BSM

- Identificazione di b-jet, decadimenti adronici dei tau

- Consente di mitigare gli effetti di «confusione» legati alle molte collisioni in sovrapposizione

- identificare i vertici di tutte le collisioni nell'evento per associare oggetti prodotti dalla stessa collisione

- Ridurre l'effetto del pileup nell'identificazione di vertici: JVF, track jets, correggere la determinazione della MET, particle flow, ...

- Il tracciatore al silicio fornisce informazione sull'evento a partire da pochi centimetri dal punto di collisione

- Altissima densità di punti, problema di calcolo oneroso per HLT

- In ATLAS la tracciature limitata a RoI o completa ma per una frazione limitata degli eventi

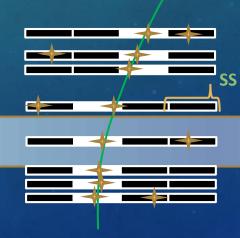

#### TRACCIARE USANDO CHIP DI MEMORIA ASSOCIATIVA

- Una possibile soluzione per ricostruire tracce usando tutti dati dell'inner detector, con bassa latenza è l'uso di Memorie Associative

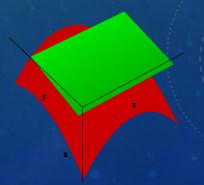

- L'algoritmo di tracciatura prevede di separare il «pattern recognition» ed il «track fitting» in 2 passi sequenziali

- Il pattern recognition si basa disponibilità di un dizionario precalcolato di tracce, pattern

- Le tracce sono calcolate a bassa risoluzione, ottimizzando la capacità di reiezione e la dimensione della banca di pattern

- Gli hit associati con un pattern trovato in un evento sono quindi usati per costruire candidati di tracce

- La precisione piena del rivelatore è ripristinata

- Il calcolo dei parametri sfrutta trasformazioni conformi, riducendo il calcolo dei parametri ad un prodotto scalare

- Procedura già provata a CDF, migliorata per essere utilizzata in ATLAS

- Capacità di utilizzare pixel, ricostruzione 3D, maggiore flessibilità

$$p_i = \sum_j C_{ij} \cdot x_j + q_i$$

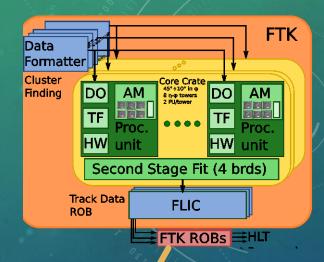

#### DESIGN DEL PROCESSORE FAST TRACKER

- FTK design finalizzato nel 2013 con la presentazione del TDR

- Computing power organizzato in processori indipendenti

- Dati organizzati in 64 torri proiettive η-φ

- 8 processori indipendenti per torre

- Latenza di processamento estremamente ridotta ed alta frequenza di processamento

- Tracciamento completo entro 100 μs

- Tracciatura usa chip VLSI custom e FPGA di ultima generazione

- 8192 AM chips, capaci di registrare fino ad 1 miliardo di patterns

- Più di 2000 FPGA in schede VME e ATCA

- FTK sarà visto dagli algoritmi di selezione come un algortimo standard

- Stesso formato degli algoritmi forniti dagli altri algoritmi, basso payload

- Possibilità di raffinare le tracce se utile per le selezioni

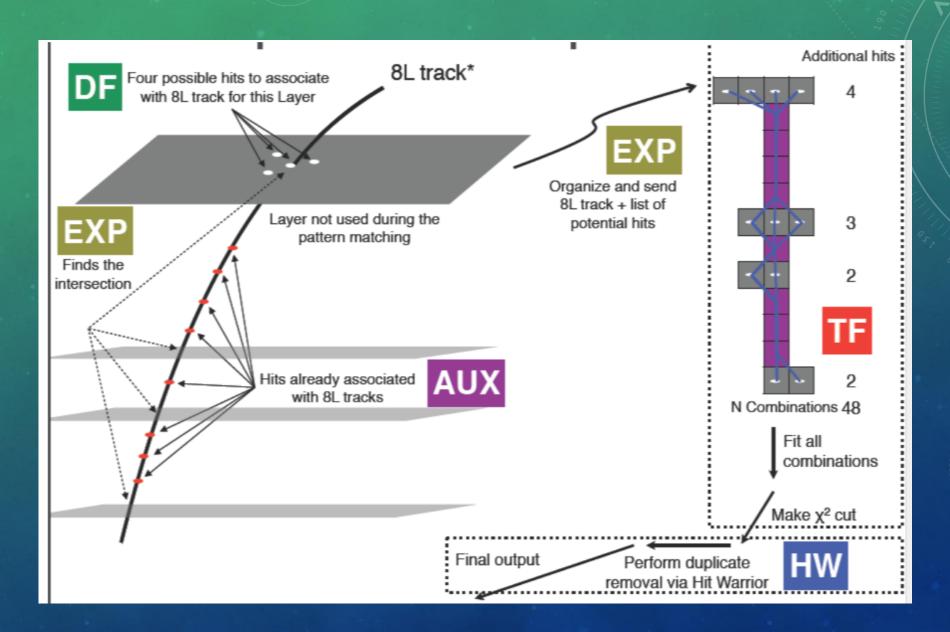

#### LA PIPELINE COMPLETA DEGLI ALGORITMI

2.1m

Barrel semiconductor tracker

Pixel defectors

Barrel transition radiation tracker

End-cap transition radiation tracker

End-cap semiconductor tracker

FTK has a custom clustering algorithm, running on FPGAs

Data are geometrically distributed to the processing units and compared to existing track patterns.

Pattern matching limited to 8 layers: 3 pixels + 5 SCTs.

Hits compared at reduced resolution.

Good 8-layer tracks are extrapolated to additional layers, improving the fit

$$p_i = \sum_j C_{ij} \cdot x_j + q_i$$

$$\chi^2 = \sum_i \left(\sum_j A_{ij} \cdot x_j + k_i\right)^2$$

Full hit precision restored in good roads.

Fits reduced to scalar products.

#### FTK PIPELINE BANDWIDTH SUMMARY

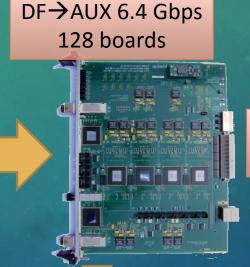

ROD→DF/IM 2 Gbps/link, 380 links 32 boards

DF→DF

~25 Gbps between shelves

40 Gbps within the shelf

AUX→SSB 6.4x4 Gbps 32 boards

AUX→AMB 12 Gbps AMB→AUX 16 Gbps

SSB→FLIC 32 Gbps total FLIC→ROS 32 Gbps total 2 boards

IFAE 2016, Genova - 31/03/2016

#### RICERCA DEI CLUSTER E DISTRIBUZIONE DEI DATI

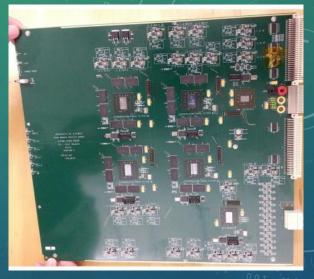

- La porta d'ingresso del sistema è composto da «Input Mezzanine» (IM) e «Data Formatter» (DF)

- Il sistema finale sarà composto da 32 DF e 128 IM

- Raccoglie 700 Gbps dall'ID di ATLAS

- La IM raccoglie i dati raw da pixel e strip

- Implementa un algoritmo di clustering in real-time capace di sostenere un input rate di 40 MHz

- Responsabilità della scheda e FW: INFN Frascati (LNF),

Pisa e Waseda (Tokyo)

- 2 Modelli basati su FPGA diversi: Spartan 6 o Artix 7

- Tutte le 80 schede per modello sono già disponibili ed in fase di test

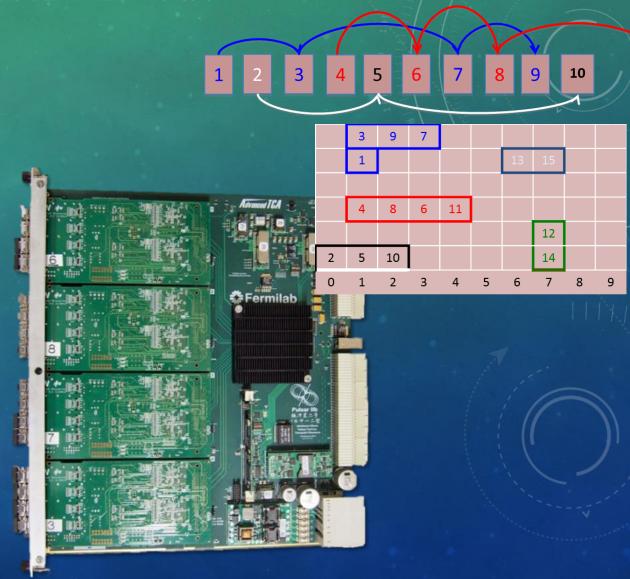

- Il DF sfrutta la tecnologia ATCA ed ha la possibilità di gestire fino a 4 IMs

- Backplane full-mesh in grado di garantire fino a 40 MB/s punto-punto

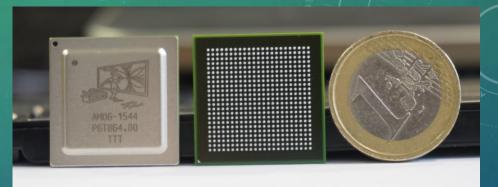

#### IL CHIP DI MEMORIA ASSOCIATIVA: AM06

- Il chip di memoria associativa è il cuore del sistema

- Progettato da INFN (Milano, Pisa, Frascati) e LPNHE (Parigi) per FTK

- Caratteristiche principali

- Tecnologia TSMC CMOS 65 nm

- 168 mm<sup>2</sup>, 421 M transistor

- 128 k patterns per chip, in 64 blocchi, 8 layers da 16 bits

- Possibilità di uso di «don't care» bits, da 3 a 6 bit ternary

- Complessità paragonabile ad un processore commerciale

- Produzione cominciata a Novembre

- 9 wafer con transistor «tipici», «fast» e «slow»

- Test e caratterizzazione in corso su «slow» e «fast»

- Performance in linea con le attese

- Consumo osservato di 3-4 W/chip

Siti di test: Milano, Frascati e Parigi

Overview of the ATLAS FTK - G. Volpi

#### LA SCHEDA DI MEMORIA ASSOCIATIVE

- Scheda di memoria associative composta da una motherboard (AMBSLP) ed un daughter board con 16 AM chip 06 (LAMB)

- Entrambe le schede progettate da Univ ed INFN Pisa

- LAMB (v3) in fase di pre-produzione utilizzando i primi chip testati da Milano e Parigi

- 5 schede prodotte dal servizio di elettronica del CERN

- Altre schede in produzione ed attese presto

- AMBSLP, produzione del prototipo finale (v5) della scheda in corso

- Cruciale la capacità di gestire link seriali ad alta frequenza

- Pattern matching ottenuto entro 10 us

- Capacità di alimentare stabilmente i 64 AM chip (8 M patterns) con 4

DCDC da 80 A picco

- Consumo massimo stimato di 300 W

- Funzionamento del sistema verificato all'interno del DAQ di ATLAS

11

Overview of the ATLAS FTK - G. Volpi IFAE 2016, Genova - 31/03/2016

#### TRACK FITTING E PREPARAZIONE DEI DATI

- Fit suddiviso in 2 step sequenziali

- Primo fit utilizza 8 layer, usando gli hit compatibili con road trovate dalla AMBSLP

- Combinazioni di bassa qualità rigettate

- Tracce di buona qualità estese a 12 layer, aumentando la qualità e diminuendo la quantità di «fake»

- Primo fit sequenziale fatto dall AUXiliary card

- Installata come modulo posteriore della AMBSLP

- Secondo fit gestito dalla «Second Stage Board» (SSB)

- Contenuta nello stesso crate VME

- Tracce finali prodotte dalla SSB raccolti dal «FTK to Level-2 Interface Card»

- Implementato in un crate ATCA

Overview of the ATLAS FTK - G. Volpi

'AtlasPublic

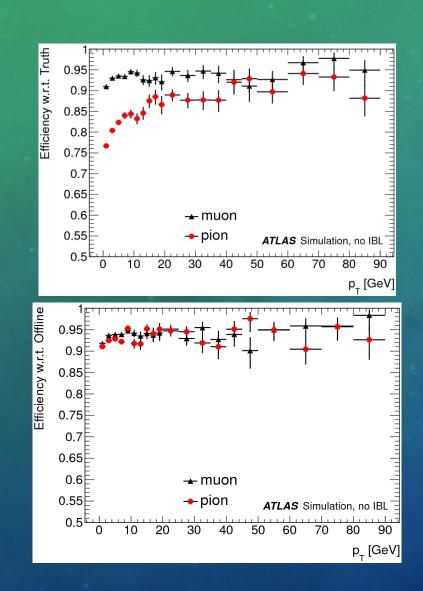

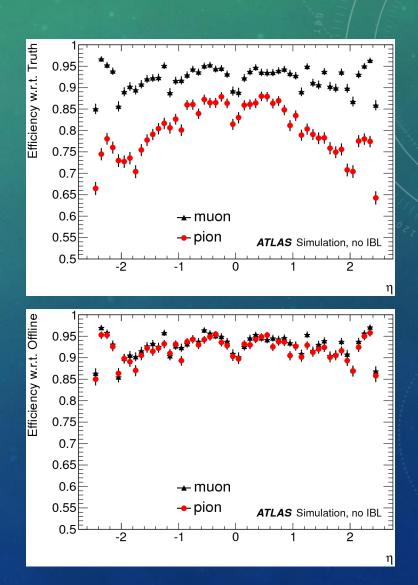

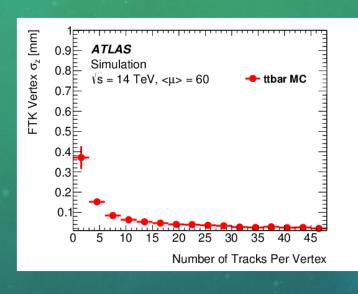

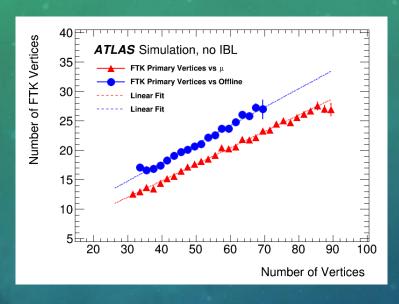

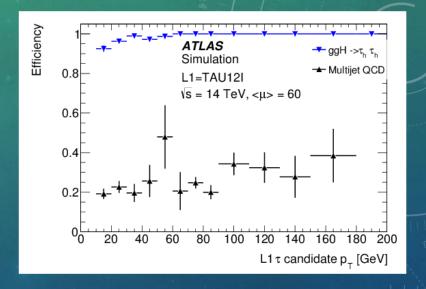

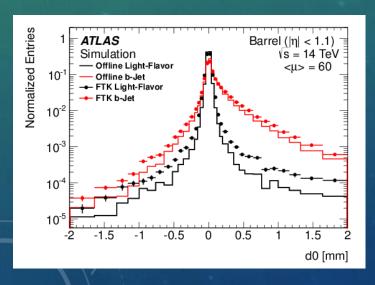

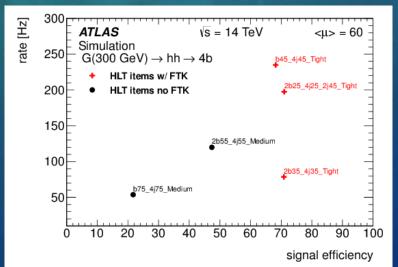

#### FTK PERFORMANCE: HLT ALGORITHMS

14

Overview of the ATLAS FTK - G. Volpi IFAE 2016, Genova - 31/03/2016

#### INTEGRAZIONE E TEST DELL'INFRASTRUTTURA

- Primi passi dell'integrazione di FTK nella DAQ di ATLAS in corso

- Sviluppo del software di controllo e monitoraggio in corso

- Parte delle IM e dei DF già installati

- Integrazione degli altri prototipi in corso, sistema in veloce evoluzione

- Test in corso per validare l'infrastruttura

- Attenzione sul design dei crate VME

- Alimentazione della «Processing Unit» richiede 7 kW

- Power supply custom costruito con l'aiuto di CAEN

- Raffreddamento attraverso fan-tray custom costruito dall'INFN di Pavia

#### SCHEDULE DELL'INTEGRAZIONE DI FTK IN ATLAS

| Step  | IM  | DF | AUX | AMB | AMChip | SSB | FLIC | Milestones            | Expected         |

|-------|-----|----|-----|-----|--------|-----|------|-----------------------|------------------|

| Α     | 4   | 1  | 1*  | 1   | 05     | 1   | 1    | Nel TDAQ              | In progress      |

| В     | 32* | 8* | 1*  | 1   | 06     | 1   | 1*   | Nel TDAQ              | In progress      |

| 3°    | 128 | 32 | 16  | 1   | 06     | 1   | 2    | Nel TDAQ              | 4/2016           |

| 4°    | 128 | 32 | 16  | 16  | 06     | 8   | 2    | Barrel (mu=40)        | 7/2016           |

| 5°    | 128 | 32 | 32  | 32  | 06     | 8   | 2    | Full detector (mu=40) | 2/2017           |

| Final | 128 | 32 | 128 | 128 | 06     | 32  | 2    | TDR Specs             | 2018/Lumi driven |

- Integrazione in corso, con copertura del barrel durante l'estate del 2016

- HW necessario per sostenere pileup fino a 40

- Copertura completa del detector attesa per l'inizio della presa dati del 2017

- Il numero finale di schede, in grado di sostenere fino a pileup 80, sarà installato per il 2018

- La quantità di schede sarà guidato dalla disponibilità delle schede ma anche dalle performance di LHC e dalle necessità di ATLAS

#### PROSPETTIVE FUTURE

- L'integrazione di FTK è ancora in corso, la tecnologia utilizzata è importante per future applicazioni

- Durante HL-LHC l'informazione delle tracce sarà di importanza anche maggiore

- Sarà identificare segnali rari in un numero di eventi di pileup di 140 e oltre

- ATLAS si aspetta di poter continuare ad avere tracciamento a 100 KHz prima dell'HLT e in RoI per il Level 1

- Le AM sono l'unica soluzione tecnologica per il L1Track

- Tecnologia favorita per FTK++, in competizione con GPU ed altri acceleratori

- Attenzione anche da parte di CMS per la tecnologia nel caso del «Track Trigger»

- Possibilità di uso delle memorie in coprocessori

- Anche per uso extra-HEP, visitate il poster di C. Sotiropoulou poster su applicazioni per l'imaging

#### ATLAS LO/L1 Infrastructure for HL-LHC

#### CONCLUSIONI

- FTK consentirà al sistema di trigger e acquisizione dati di ATLAS di ricostruire completamente le tracce per ogni evento raccolto dal trigger di Livello 1, fino a 100 kHz, con latenza minore di 100 μs

- Consente di superare le limitazioni imposta dalla tracciatura in «Regioni di Interesse» per canali di primo piano

- Aumenta la capacità per tutti le selezioni del HLT di mitigare gli effetti negativi dell'alta luminosità

- Si aspettano benefici diretti in trigger per jet da b-quark e leptoni T

- Consentirà di implementare correzioni evento per evento per misure calorimetriche

- Possibilità di ricostruire tutti i vertici delle collisioni ed associare gli oggetti alla collisione di origine

- La costruzione dell'HW e in dirittura di arrivo e la fase di installazione è in corso

- Alcune schede hanno già terminato la produzione (IM e DF)

- Altre sono nella fase finale di produzione o pre-produzione

- Copertura della zona centrale entro il 2016, copertura completa all'inizio del 2017

- La tecnologia sviluppata per FTK è un ottimo candidato per trigger di traccia per HL-LHC

- Con possibili usi in altri campi: image processing, analisi biomedicale, ...

Overview of the ATLAS FTK - G. Volpi IFAE 2016, Genova - 31/03/2016

## GRAZIE A TUTTI PER L'ATTENZIONE

Overview of the ATLAS FTK - G. Volpi

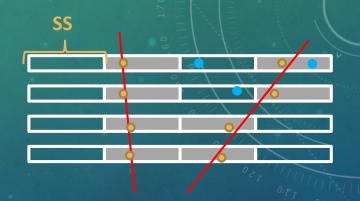

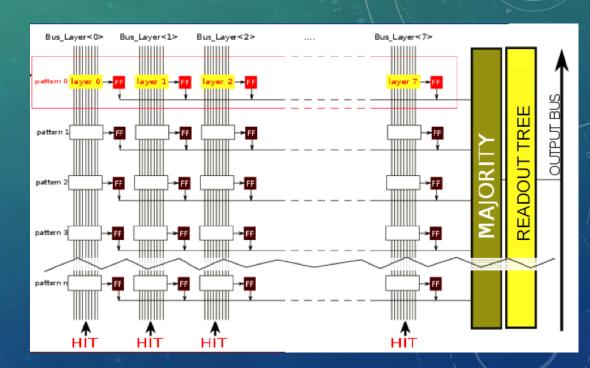

#### PATTERN MATCHING WITH AM CHIP

- The AM chip is a special CAM chip

- The AM identify the presence of stored patterns in the incoming data

- Input data arrives through independent busses

- Patterns with enough matching data are selected

- Threshold can be reprogrammed

- DC feature (next slide) allow different match precision

- The chips are installed in boards able to send data to all the chips in parallel

- At every clock incoming data can be compared with all the patterns

AM CONSUMPTION: ~ 3.5 W for 128 kpatterns

#### AM COMPUTING POWER

Each pattern can be seen as 4 32 bits comparators, operating at 100 MHz.  $50 \ 10^6 \ \text{MIP/chip} \rightarrow 4 \ 10^{11} \ \text{MIP}$  in the whole AM system

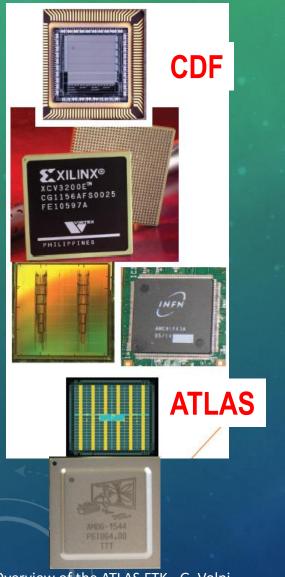

#### THE AM CHIP HISTORY

- 90's Full custom VLSI chip 0,7 mm AMS (INFN-Pisa) 128 patterns, 6x12 bit words each (F. Morsani et al., The AM chip: a Full-custom MOS VLSI Associative memory for Pattern Recognition, IEEE Trans. on Nucl. Sci.,vol. 39, pp. 795-797 (1992).) 25 MHz clock

- 1998 FPGA (Xilinx 5000) for the same AMchip (P. Giannetti et al., A Programmable Associative Memory for Track Finding, Nucl. Intsr. and Meth., vol. A 413/2-3, pp.367-373, (1998)).

- 1999 first standard cell project presented at LHCC

- 2006 AMChip 03 Standard Cell UMC 0,18 mm, 5k patterns in 100 mm² for CDF SVT upgrade total: AM patterns (L. Sartori, A. Annovi et al., A VLSI Processor for Fast Track Finding Based on Content Addressable Memories, IEEE TNS, Vol 53, Issue 4, Part 2, Aug. 2006). 50 MHz clock

- 2012 AMchip04 (Full custom/Std cell) TSMC 65 nm LP technology, 8k patterns in 14mm<sup>2</sup> Pattern density x12. First variable resolution implementation. (F. Alberti et al, 2013 JINST & C01040, doi:10.1088/1748-0221/8/01/C01040) 100 MHz

- 2013 AMchip05, 4k patterns in 12 mm<sup>2</sup> a further step towards final AMchip version. **Serialized**I/O buses at 2 Gbs, further power reduction approach. BGA 23x23 package.

- End 2015 AMchip06: 128k patterns in 180 mm<sup>2</sup>. Final version of the AMchip for the ATLAS experiment.

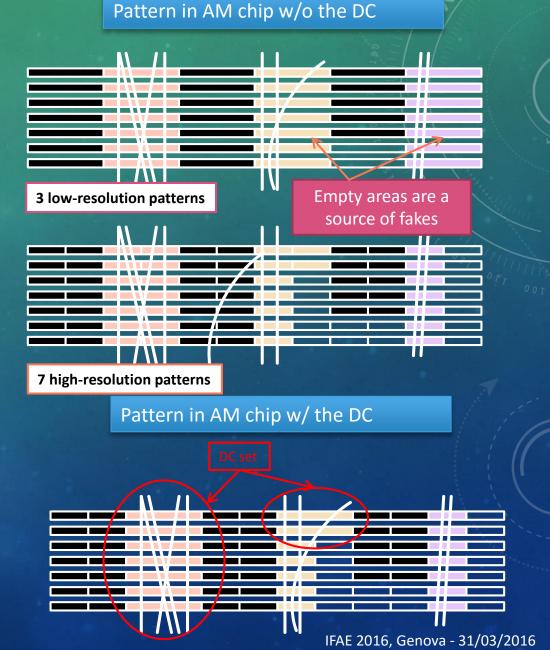

#### DON'T CARE FEATURES

- The LSB bit in AM match lines can use up to 6 ternary bits

- Each bit allow 0, 1 and X (don't care)

- K. Pagiamtzis and A. Sheikholeslami, Solid-State Circuits, IEEE Journal of, vol. 41, no. 3, 2006

- The DC bits allow to reduce the match precision where required

- The use of DC solves the problem of balancing the match precision

- Low resolution patterns allow smaller pattern bank size (less chips, less cost), but the probability of random coincidences grows

- High resolution increase the filtering power at the price of a much larger banks

- DC allows to merge similar pattern in favored configurations (less patterns) maintaining high-resolution and rejection power where convenient

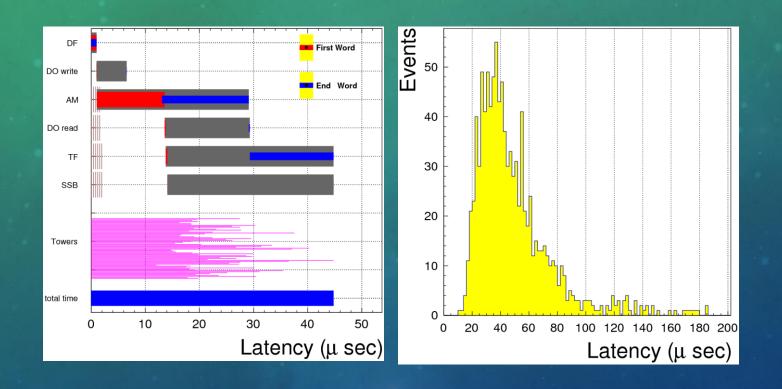

### FTK SYSTEM EXPECT PERFORMANCE (LATENCY)

The expected latency of the FTK pipeline has been carefully emulated highlighting how full tracking reconstruction can be achieved within 100  $\mu$ s.

Results obtained combining the emulation results with the parameters from the boards' design.

Overview of the ATLAS FTK - G. Volpi