## SVT organization for TDR

#### 1. Major decisions needed and R&D required to make them.

- Layer 0 technology:

- Hybrid Pixel: Want to demonstrate that reduction in the front-end pitch to 50x50  $\mu$ m2 and in the total material budget is possible to meet Layer0 requirements. Working on a plan to test this option with beam Sep. 2010.

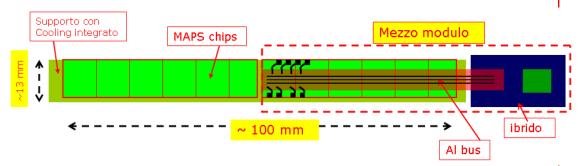

- <u>CMOS MAPS</u>: Plan to build a multichip CMOS MAPS prototype module with specs close to the SuperB LayerO requirements → Testbeam in 2010.

- All the module components could be the same for a LayerO module based on MAPS/Hybrid Pixels

- Striplets: evaluate real limit of FSSR2 speed with high background.

### 2. Manpower in place and still required

- Still Working on a better estimate of manpower for TDR

- Old estimate: Phy~6 FTE(~4 avail.), Mech Eng.~ 4 FTE (< 2 avail.), Electr. Eng.</li>

~ 6 FTE (<4 avail.)</li>

- LayerO activities somehow covered

- External layer design: interest from some groups but lack of manpower and activities not yet started (no real commitments yet).

- Mechanics: long list of activities but < 2 FTE involved</li>

# SVT organization for TDR

#### 3. Milestones (very preliminary)

- May '09: finalize readout architecture for MAPS

& Hybrid pixel front-end chips

- Sept-Nov '09 chips submission

- <u>Sept '09</u> high resistivity pixel sensor production

- Jan July 2010: lab test (sensor/front-end chip/MAPS) → bump bonding hybrid pixel / MAPS module assembly → lab test

Sep 2010: testbeam

| WBS     | Item                                              | Required |     | d Man-months (2 year |                | ea) •                                          | Mai        |

|---------|---------------------------------------------------|----------|-----|----------------------|----------------|------------------------------------------------|------------|

|         |                                                   | Phy      | Eng | Tecn                 | Comp           | p l                                            | Maj<br>Nee |

| 1       | SVI (IDR)                                         |          |     |                      |                |                                                | Mac        |

| 1.1     | Design optimization                               |          |     |                      |                | 7                                              | INCE       |

| 1.1.1   | detetctor geometry optimization                   |          |     | ١.                   |                | 7                                              | <b>T</b> . |

| 1.1.1.1 | FastSim implementation                            |          |     |                      | 3.2.2          | MAPS readout architecture (VHDL •              | Ite        |

| 1.1.1.2 | Physic Study                                      |          |     |                      | 3.2.3          | MAPS chip layout                               |            |

| 1.1.2   | background studies                                |          |     | _                    | 3.2.4          | MAPS chip testboard design/construction/chip i | mounting   |

| 1.1.2.1 | Geometry implementation                           |          |     |                      | 3.2.5          | MAPS chip test                                 |            |

| 1.1.2.2 | SVT rate                                          |          |     |                      | 3.3            | Pixel Module design electronics                |            |

| 1.2     | Mechanics                                         |          |     |                      | 3.3.1          | Pixel bus                                      |            |

| 1.2.1   | LO                                                |          |     |                      | 3.3.2          | HDI                                            | $\perp$    |

| 1.2.1.1 | Module support and cooling design/simulation/tes  | st       |     |                      | 3.4            | Prototype MAPS module                          |            |

| 1.2.1.2 | Full layer0 design                                |          |     |                      | 3.4.1          | Pixel bus test                                 |            |

| 1.2.2   | L1-L5                                             |          |     |                      | 3.4.2          | HDI                                            |            |

| 1.2.2.1 | Module support and cooling design                 |          |     |                      | 3.4.3          | Module Integration                             |            |

| 1.2.2.2 | Full L1-L5 support design                         |          |     |                      | 3.4.3          | Module lab test                                |            |

| 1.2.3   | Beam Pipe design                                  |          |     |                      | 3.5            | Radiation damage MAPS chip                     | ++         |

| 1.2.4   | Mech integration (fast dismounting design)        |          |     |                      | 3.6            | Striplets                                      | $\perp$    |

| 1.2.5   | Mechanical System Engineer                        |          |     |                      | 3.6.1          | FSSR2 speed evaluation                         |            |

| 1.3     | Electronics & Sensor                              |          |     |                      | 3.6.2          | multilayer interconnection                     |            |

| 1.3.1   | Hybrid Pixels                                     |          |     |                      | 3.7            | L1-L5                                          |            |

| 1.3.1.1 | Sensor design/test                                |          | +   |                      | 3.7.1          | Sensors                                        |            |

| 1.3.1.2 | FE analog optimization                            |          |     |                      | 3.7.2<br>3.7.3 | FE chips evaluation HDI                        | +          |

| 1.3.1.3 | FE chip layout                                    |          | 1   |                      | 3.7.4          | Prototype module production ???                | +          |

| 1.3.1.4 | FE chip testboard design/construction/chip mounti | na       | 1   |                      | 3.6            | DAQ+trigger                                    | ++         |

| 1.3.1.5 | FE chip tests tests                               | 9        | +   |                      | 3.7            | Power Distribution                             | +          |

| 1.3.1.6 | FE chip + sensor bump bonded test                 |          | +   |                      | 3.8            | Electrical System Engineer                     | +          |

| 1.3.2   | MAPS                                              |          | +   | 1 1                  |                | Detetctor Monitoring & Interlocks              | + +        |

| 1.3.2.1 | FE analog-sensor optimization                     |          | +   | 1.5                  | -              | Testbeam                                       | +          |

|       |                           | start  | end    |

|-------|---------------------------|--------|--------|

| 1     | I.1 Hybrid pixels         |        |        |

| 1.1.1 | front-end chip            |        |        |

|       | optimization readout arch | 1-Feb  | Apr-09 |

|       | design analog cell        | 1-Apr  | May-09 |

|       | VHDL                      | 1-May  | Jun-09 |

|       | layout                    | 1-May  | Sep-09 |

|       | production                | Sep-09 | Jan-10 |

|       | test                      | Feb-10 | Mar-10 |

| 1.1.2 | sensor                    |        |        |

|       | design                    | Jul-09 | Aug-09 |

|       | production                | Sep-09 |        |

|       | test                      | Jan-10 | Feb-10 |

| 1.1.3 | chip+sensor               |        |        |

|       | interconnection           | Mar-10 | Apr-10 |

|       | test                      | May-10 |        |

| 1.1.4 | testbeam                  | Sep-10 |        |

|       |                           |        |        |

#### 4. Status of WBS planning

- Major activities defined

- Need to fill in manpower

- Iteration with Institutions

### SVT Activities for TDR (I)

Activities now more focused on TDR preparation (end of 2010) Some R&D still needed for Layer 0:

- Plan to build a multichip CMOS MAPS prototype module with specs close to the SuperB LayerO requirements → Testbeam in 2010.

- All the module components could be the same for a LayerO module based on Hybrid Pixels.

Activity funded by INFN.

Institutions: Bologna, Milano,

Pavia/Bergamo, Pisa, Roma III,

Torino, Trieste.

- Hybrid Pixel: more emphasis now on this option: it could become the baseline LayerO option for the TDR in case MAPS are not considered mature enough by that time.

- Need to demonstrate by 2010 that reduction in the front-end pitch to 50x50  $\mu\text{m}^2$  and in the total material budget is possible to meet Layer0 requirements.

- Striplets: continue to evaluate the use of FSSR2 readout chip and light interconnections from sensor to front-end

## SVT Activities for TDR (II)

### **Background Simulation:**

This set the scale for requirements on Layer0 and the inner SVT Layers.

### External Layers Design

- Technology is not an issue

- Need to optimize the geometry with Fast Simulation (D. Brown's talk)

- Need to evaluate the best front-end chip for strip modules among the ones "on the market" (FSSR2...)

### Off Detector electronics and DAQ Development

(M. Citterio, M. Villa's talk)

#### Mechanics:

- · Beam-pipe design

- Light support and cooling for LayerO modules (F.Bosi's talk)

- Module design for the external Layers

- Design the full SVT support structure (want to have the LayerO easily accessible for replacement). Important interplay with IR design.

- A significant amount of work is needed for the TDR and not all listed activities are well covered.