## VHDL COUNTER

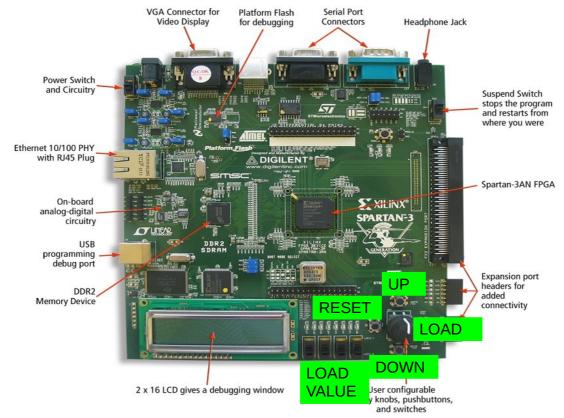

Implement an up/down counter using a spartan3A/3AN board. The counter must have a LOAD, UP, DOWN and RESET signals mapped on the board according to Figure I.

Figure 1: Board signal map

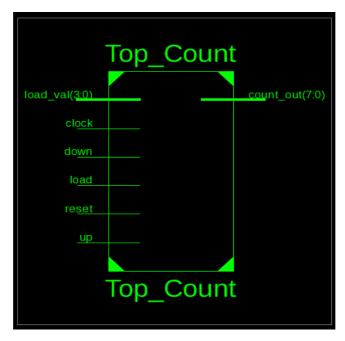

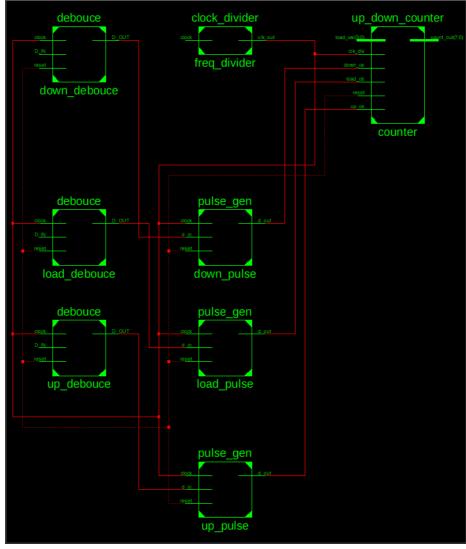

Design the counter according to the block diagram shown in fig. 2 and 3. The blocks **Top\_Count**, **debouce** and **pulse\_gen**, together with the **UCF** file are already contained in the **contatore\_edit** project. **Freq\_divider** and **counter** must be designed according to the following requirements:

freq\_divider: must implement a 16 bits division, while counter must have asynchronous reset and up/down/load features.

Suggestion for behavioral simulation: decrease the **freq\_divider** value (for example use  $2^4$  in such a way you can check the counter functionality in the default time window display).

Figure 2: Top\_Count block diagram (the I/O signals are mapped in the ucf file)

$Figure\ 3:\ Top\_Counter\ internal\ block\ diagram$