# PId Front End Chip: PIF

D. Breton, C. Beigbeder, A. El Berni, V. Tocut, LAL/IN2P3 Orsay

> H. Lebbolo LPNHE/IN2P3 Paris

# Characteristics & Requirements

- PMT signal characteristics (Jerry's & Bari's meas.):

- ✤ amplitude's:

- ♦ Dynamic around 15

- Pixel to pixel dispersion: 3

- ♦ time's:

- rise time: 700ps

- ♦ Fall time: 1,5ns

### • Time measurement :

- Solution max total

Considering 70ps TDC resolution: 50ps for PIF

- MHz background rate max

- ✤ 50ns double pulse resolution min

#### • Charge measurement :

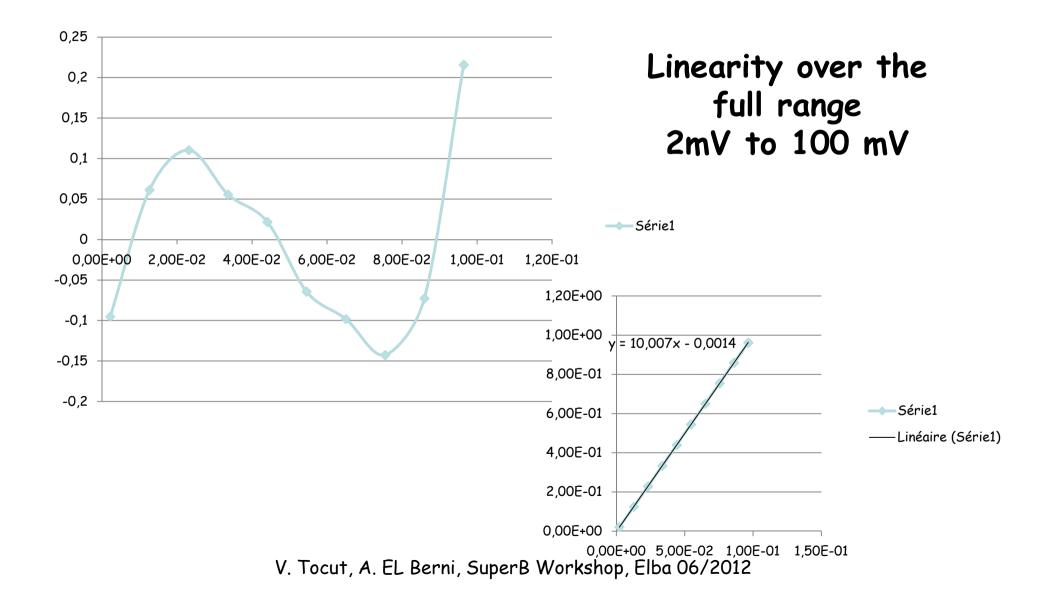

- ♦ Maximum signal considered to be 100mV

- ♦ 8 bits

- ✤ Time measurement synchronous

- V. Tocut, A. EL Berni, SuperB Workshop, Elba 06/2012

PIF: PID FE chip

| +++                                                                                                                                           |                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| <ul> <li>No walk correction if walk &lt; 50ps<br/>(depending on PM dynamics)</li> <li>Charge measurement to improve<br/>resolution</li> </ul> | <ul> <li>Need « Time + charge » data<br/>synchronization</li> </ul> |

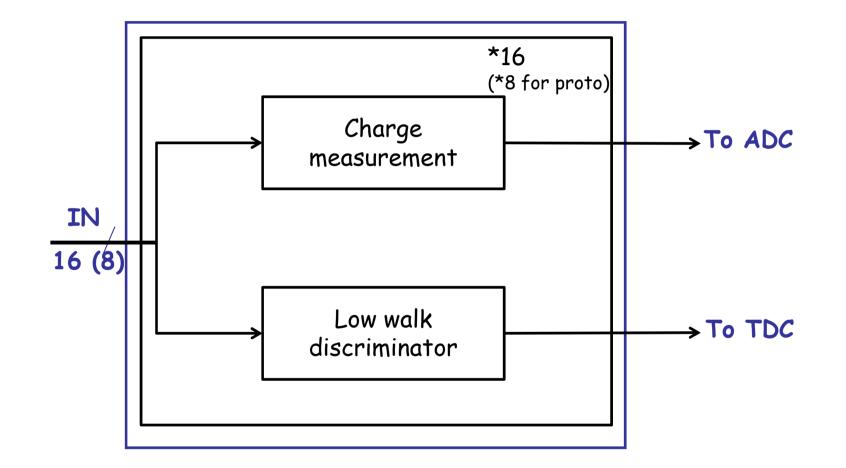

2 different chips developed:

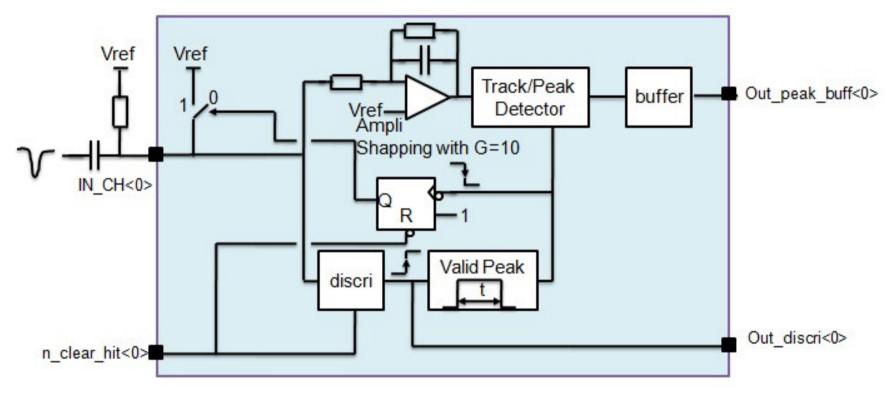

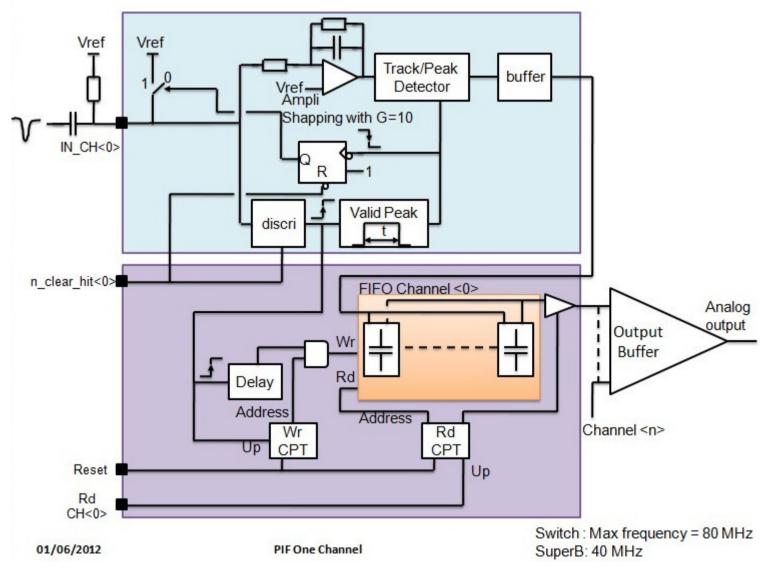

• analog front end -> {PIF }: CFD like and charge measurement

```

\Theta time measurement \rightarrow {SCATS}

```

Gain dispersion consideration:

>Input gain selection

>No selection / look up table

Both solutions need pixel mapping - 2<sup>nd</sup> solution has been chosen for the 1rst proto.

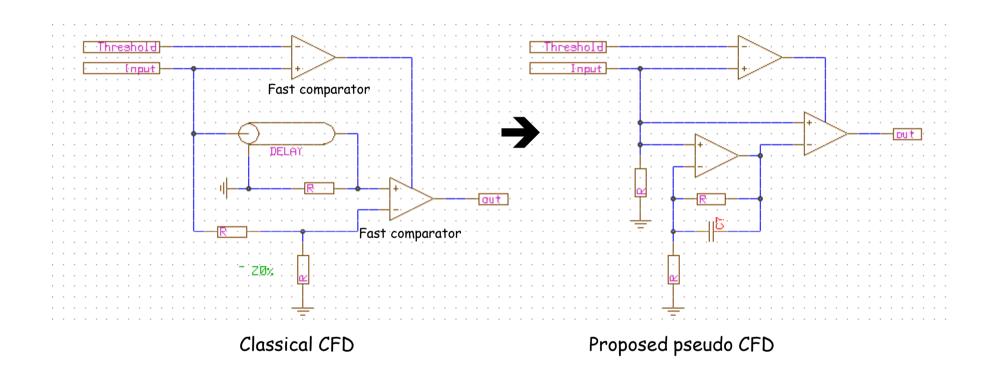

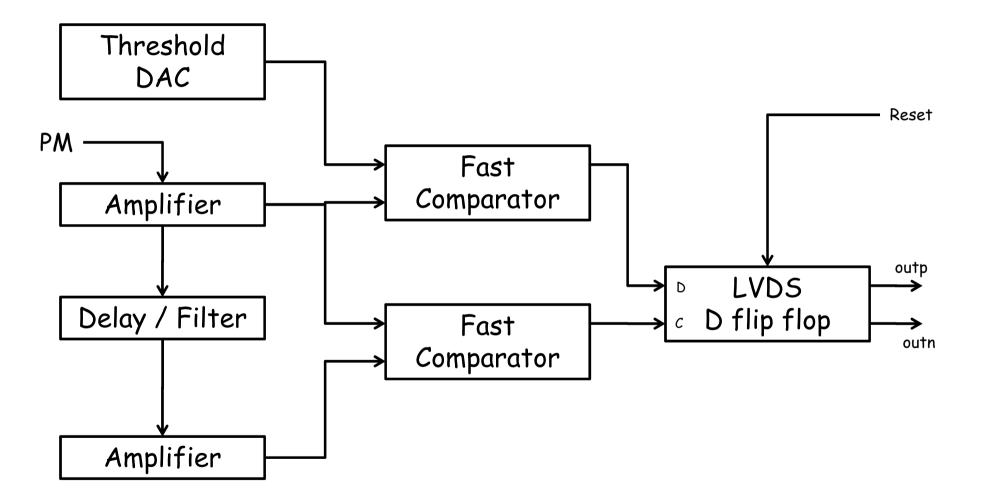

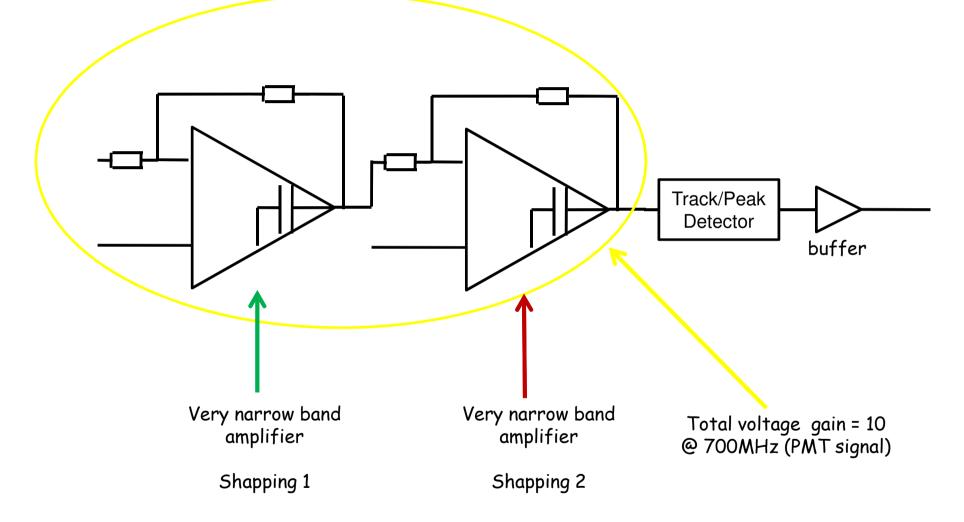

# **CFD** on silicon

• Delay + Fraction  $\rightarrow$  Gain + Integrators

V. Tocut, A. EL Berni, SuperB Workshop, Elba 06/2012

# **CFD** Implementation

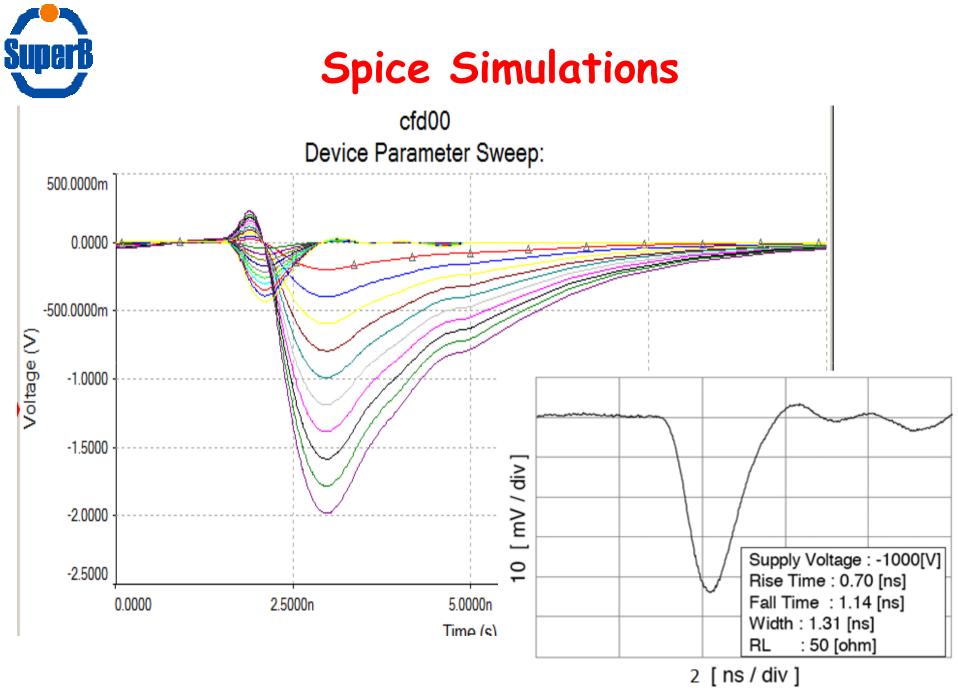

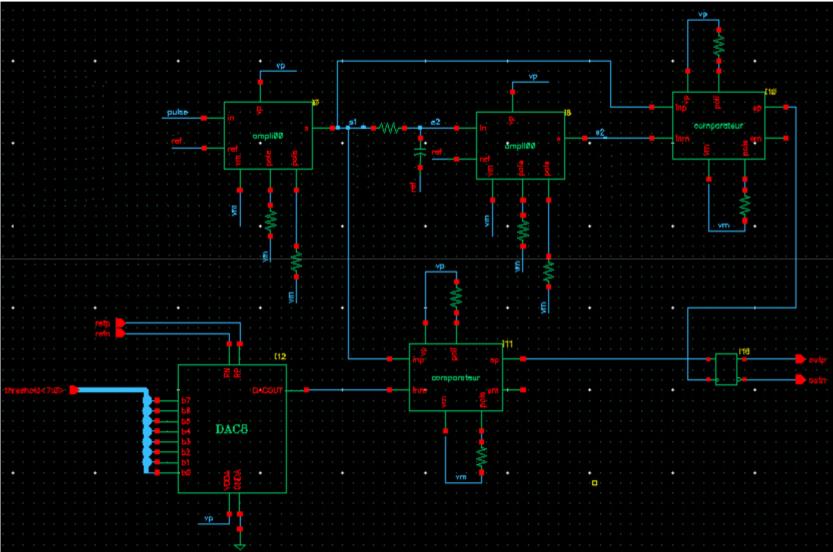

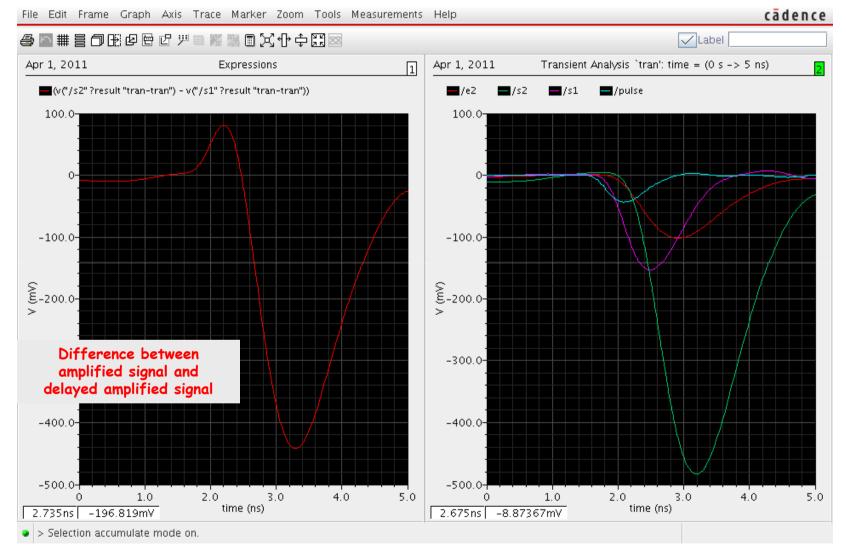

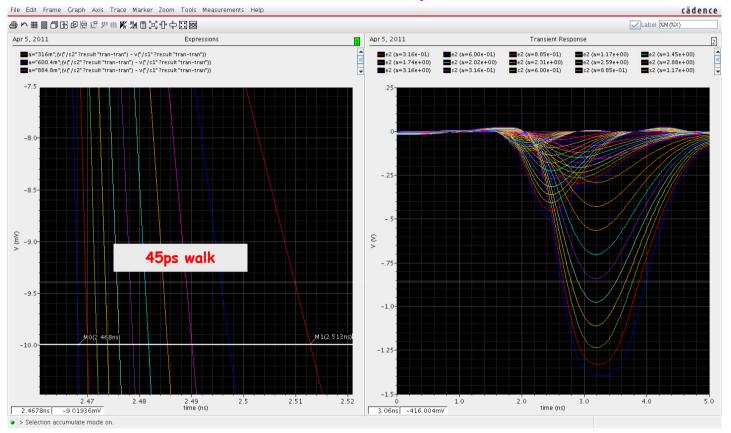

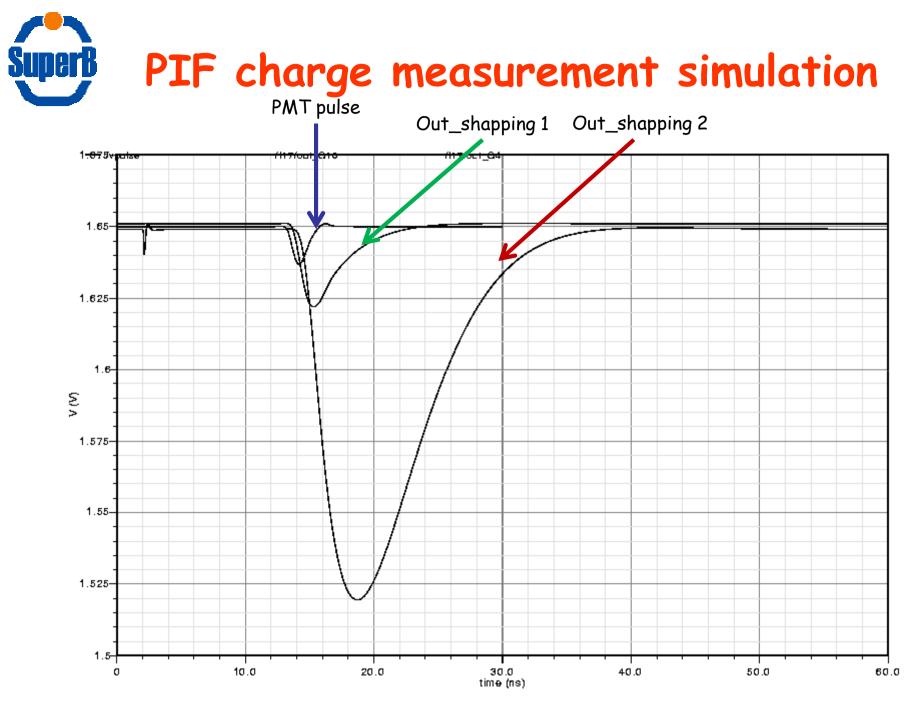

# Simulations with AMS CMOS $0.35\mu$

SuperB

# Simulations with AMS CMOS $0.35\mu$

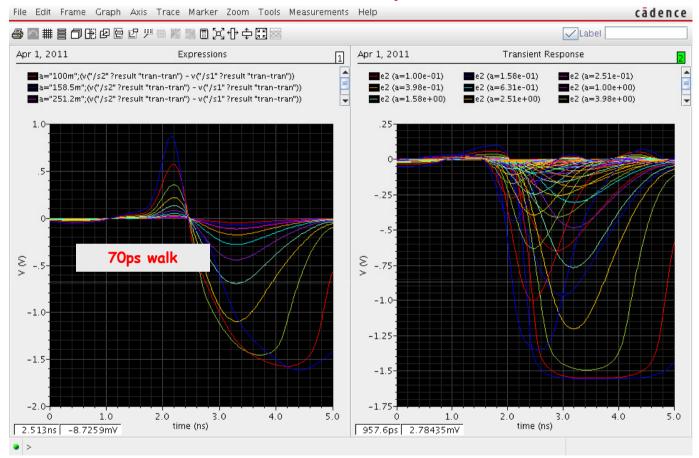

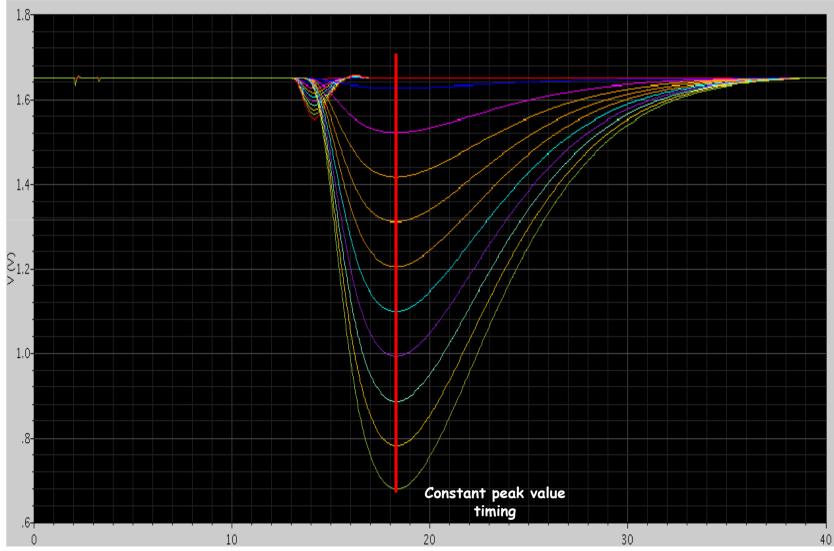

### Parametric simulation : amplitude from 1 to 100

SuperB

Resolution: \$70ps for a dynamic of 100 \$100ps total resolution

### Parametric simulation : amplitude from 1 to 10

#### Resolution: \$50ps for a dynamic of 10 \$86ps total resolution

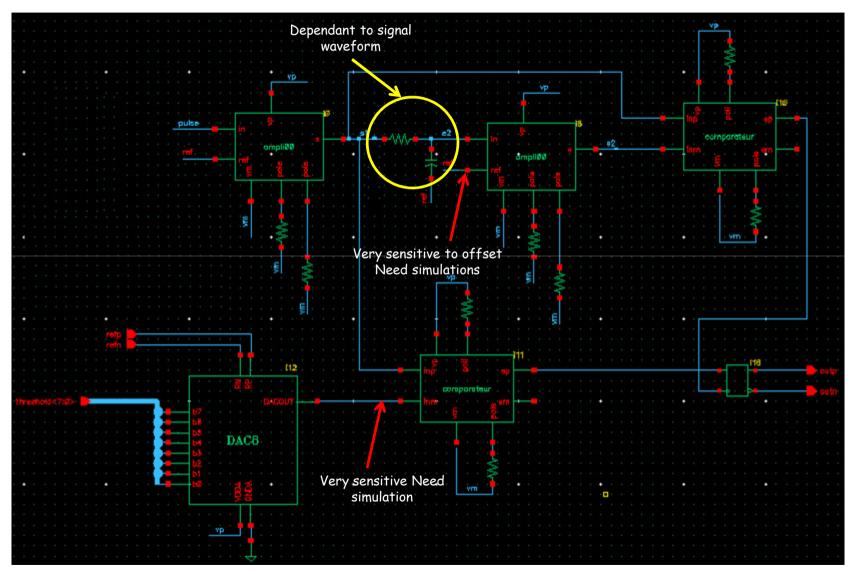

# Design challenges

V. Tocut, A. EL Berni, SuperB Workshop, Elba 06/2012

V. Tocut, A. EL Berni, SuperB Workshop, Elba 06/2012

## Milestones

- PIF:

- > Design & Simulations with CMOS AMS  $0.35\mu$  (to be 'SCATS compatible')

- Submission by the end of 2012 (Dec, the 10th). PIF back around the end of feb. 2013

# LAL CRT test bench

D. Breton, C. Beigbeder, A. El Berni, V. Tocut, LAL/IN2P3 Orsay

> M. Dehlot, H. Lebbolo LPNHE/IN2P3 Paris

>Operational CRT test bench @ LAL with discri boards.

>Sensitivity to fine tuning has been demonstrated: signal shape - signal offset....

>Manuel tuning 'a la BABAR' has to be avoided!

$\succ$  Width and amplitude of the discri signal is critical for SCATS (Time measurement):

>very low amplitude & narrow signal on CRT board

>discrete solution problem or pseudo-CFD generic problem? Has to be solved.

>Can we enlarge the signal to be able to deal with SCATS requirements?

>Pseudo CFD walk can be evaluated

At the same time, another is now under investigation

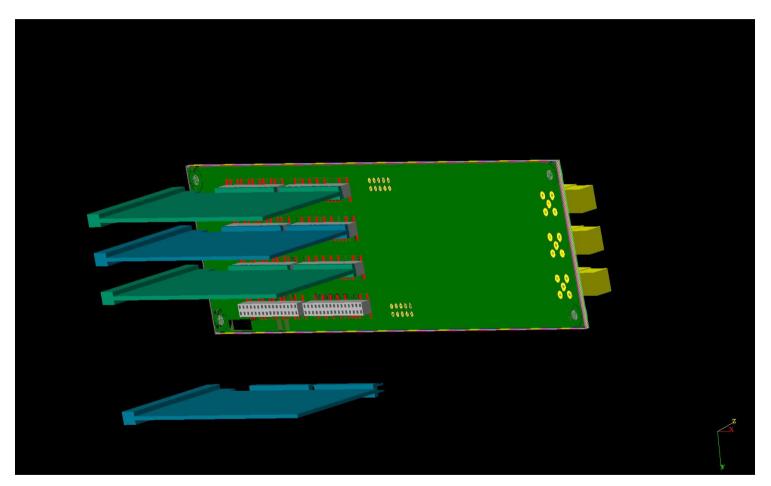

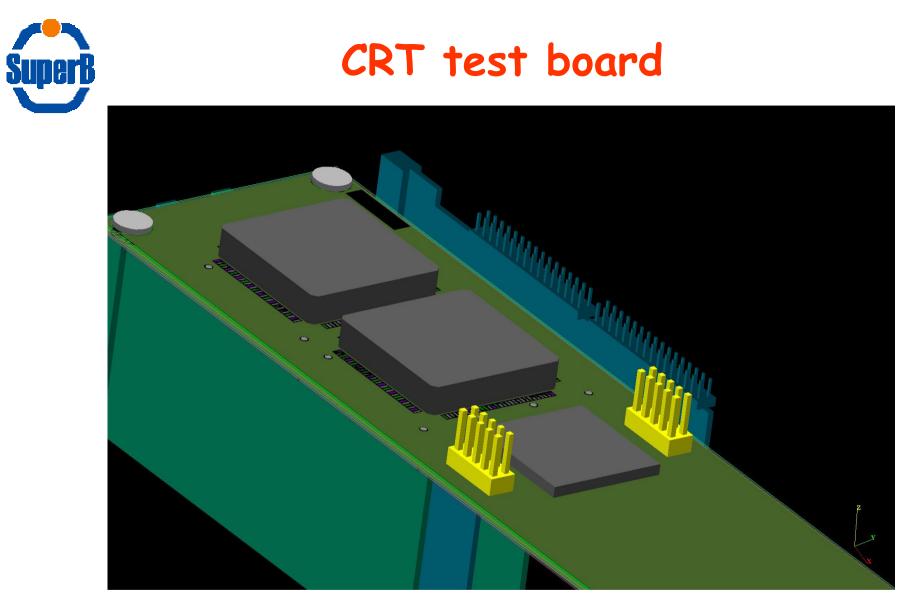

CRT test board

4 analog boards with the SCATS CRT ( bottom view)

C. Beigbeder, V. Tocut, SuperB Workshop, Elba 06/2012

SCATS CRT board : 2 SCATS, 1 FPGA.

ADC will be added for the new design of analog board with PIF.

Input and ouput connectivity have to be compatible with both designs.

C. Beigbeder, V. Tocut, SuperB Workshop, Elba 06/2012