# $\begin{array}{c} {\bf Super} B \ {\bf Detector} \\ {\bf Technical} \ {\bf Design} \ {\bf Report} \end{array}$

#### Abstract

This report describes the technical design detector for Super B.

### **Contents**

| 1 | Intro | oduction                                                         | 1  |

|---|-------|------------------------------------------------------------------|----|

|   | 1.1   | The Physics Motivation                                           | 1  |

|   | 1.2   | The SuperB Project Elements                                      | 1  |

|   | 1.3   | The Detector Design Progress Report                              | 2  |

| 2 | Acce  | elerator Overview                                                | 5  |

| 3 | Dete  | ector Overview                                                   | 7  |

|   | 3.1   | Physics Performance                                              | 7  |

|   | 3.2   | Challenges on Detector Design                                    | 10 |

|   | 3.3   | Open Issues                                                      | 12 |

|   | 3.4   | Detector R&D                                                     | 12 |

| 4 | Phys  | sics with SuperB                                                 | 17 |

| 5 | Mac   | chine Detector Interface and Backgrounds                         | 19 |

|   | 5.1   | Overview M.Sullivan, M. Boscolo E.Paoloni, - 1 page              | 19 |

|   | 5.2   | Backgrounds sources. M.Sullivan, M.Boscolo, E.Paoloni, - 2 pages | 19 |

|   | 5.3   | Radiative Bhabha A.Perez - 2 pages                               | 19 |

|   | 5.4   | Pairs Production C.Rimbault - 2 pages                            | 19 |

|   | 5.5   | Touscheck bacgkround. M.Boscolo - 2 pages                        |    |

|   | 5.6   | Beam gas background.  M.Boscolo - 2 pages                        |    |

|   | 5.7   | Synchrotron radiation background.  M.Sullivan - 2 pages          |    |

|   | 5.8   | SVT background overview R.Cenci C.Stella - 2 pages               |    |

|   | 5.9   | DCH background overview R.Cenci D.Lindemann - 2 pages            |    |

|   | 5.10  |                                                                  |    |

|   | 5.11  | FDIRC background overview R.Cenci A.Perez - 2 pages              |    |

|   | 5.12  |                                                                  |    |

|   | 5.13  |                                                                  |    |

|   | 5.14  |                                                                  |    |

|   | 5.15  |                                                                  |    |

|   | 5.16  | Quick demounting. M.Sullivan, F.Bosi, E.Paoloni - 4 pages        | 20 |

| 6 | Silic | on Vertex Tracker                                                | 21 |

|   | 6.1   | Overview                                                         |    |

|   |       | 6.1.1 SVT and Layer0                                             |    |

|   | 6.2   | SVT Requirements                                                 |    |

|   |       | 6.2.1 Resolution                                                 |    |

|   |       | 6.2.2 Acceptance                                                 |    |

|   |       | 6.2.3 Efficiency                                                 |    |

|   |       | 6.2.4 Radiation Tolerance                                        | 24 |

|      | 6.2.5   | Reliabilit | ty                                                                                   |     | <br> |      | 25 |

|------|---------|------------|--------------------------------------------------------------------------------------|-----|------|------|----|

| 6.3  | Baselir |            | or Concept                                                                           |     |      |      |    |

|      | 6.3.1   | Technolo   | ogy                                                                                  |     | <br> |      | 25 |

|      | 6.3.2   |            |                                                                                      |     |      |      |    |

|      | 6.3.3   | Electron   | ics                                                                                  |     | <br> |      | 25 |

|      | 6.3.4   | Mechanie   | cal Support                                                                          |     | <br> |      | 25 |

| 6.4  | Layer0  | Pixel Up   | $     \text{grade}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |     | <br> |      | 25 |

|      | 6.4.1   | Technolo   | egy Options                                                                          |     | <br> |      | 25 |

|      | 6.4.2   | Pixel Mo   | odule Design                                                                         |     | <br> |      | 25 |

|      | 6.4.3   | Mechani    | cal Support and Cooling                                                              |     | <br> |      | 25 |

| 6.5  | R&D I   | Main Acti  | vities                                                                               |     | <br> | <br> | 25 |

| 6.6  | Backgr  | rounds     | R.Cenci - 4 pages                                                                    |     | <br> |      | 25 |

|      | 6.6.1   | Pair pro   | $\operatorname{duction} \ldots \ldots \ldots \ldots \ldots \ldots$                   |     | <br> | <br> | 25 |

|      | 6.6.2   | Radiativ   | e Bhabha                                                                             |     | <br> |      | 25 |

|      | 6.6.3   | Touschel   | ς                                                                                    |     | <br> |      | 25 |

|      | 6.6.4   | Beam Ga    | as                                                                                   |     | <br> |      | 25 |

|      | 6.6.5   | Other so   | urces                                                                                |     | <br> | <br> | 25 |

| 6.7  | Detect  | or Perform | mance Studies N.Neri - 6 pages .                                                     |     | <br> |      | 25 |

|      | 6.7.1   |            | tion $(about 1/2 page) \dots \dots \dots \dots \dots$                                |     |      |      |    |

|      | 6.7.2   | Impact o   | of Layer<br>0 on detector performances $(about\ 2\ pages)$ .                         |     | <br> |      |    |

|      | 6.7.3   | Sensitivi  | ty studies for time-dependent analyses (about $2$ pages                              | ) . | <br> |      | 26 |

|      | 6.7.4   | Vertexin   | g and Tracking performances $(about\ 1\ pages)$                                      |     | <br> |      | 26 |

|      | 6.7.5   | Particle   | Identification (about $1/2 pages$ )                                                  |     | <br> |      | 26 |

| 6.8  | Silicon | Sensors    | L. Bosisio - 8 pages                                                                 |     |      |      |    |

|      | 6.8.1   | Requirer   | nents                                                                                |     |      |      |    |

|      |         | 6.8.1.1    | Efficiency                                                                           |     |      |      |    |

|      |         | 6.8.1.2    | Resolution                                                                           |     |      |      |    |

|      |         | 6.8.1.3    | Radiation hardness                                                                   |     |      |      |    |

|      | 6.8.2   |            | $\operatorname{esign}$                                                               |     |      |      |    |

|      |         | 6.8.2.1    | Technology choice                                                                    |     |      |      |    |

|      |         | 6.8.2.2    | Optimization of strip layout                                                         |     |      |      |    |

|      |         | 6.8.2.3    | Wafer sizes and quantities                                                           |     |      |      |    |

|      | 6.8.3   |            | ing and tests                                                                        |     |      |      | 30 |

| 6.9  |         | t Circuits | L.Vitale - M.Prest4+4 pages                                                          |     |      |      | 30 |

|      | 6.9.1   |            | for layer0                                                                           |     |      |      | 30 |

|      |         | 6.9.1.1    | Requirements                                                                         |     |      |      | 30 |

|      |         | 6.9.1.2    | Technology                                                                           |     |      |      | 30 |

|      |         | 6.9.1.3    | Design                                                                               |     |      |      | 30 |

|      |         | 6.9.1.4    | Prototyping and tests                                                                |     |      |      | 30 |

|      | 6.9.2   |            | for outer layers                                                                     |     |      |      | 30 |

|      |         | 6.9.2.1    | Requirements                                                                         |     |      |      | 30 |

|      |         | 6.9.2.2    | Material and production technique                                                    |     |      |      | 30 |

|      |         | 6.9.2.3    | Design                                                                               |     |      |      | 31 |

| C 10 | T31 /   | 6.9.2.4    | Tests and prototyping                                                                |     |      |      | 31 |

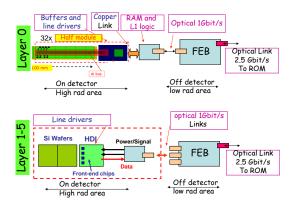

| 0.10 |         | onics Reac | 1 0                                                                                  |     |      |      | 32 |

|      | 0.10.1  | Readout    |                                                                                      |     |      |      |    |

|      |         | 0.10.1.1   | Electronic Readout for Strip and Striplet Detectors                                  |     | <br> | <br> | 32 |

|   |       |        | 6.10.1.2 | Readout chips re                        | equirements | 8            |                          | <br>. 33 |

|---|-------|--------|----------|-----------------------------------------|-------------|--------------|--------------------------|----------|

|   |       |        |          | Readout Chip Ir                         | _           |              |                          |          |

|   |       |        |          | R&D for strip re                        | _           |              |                          |          |

|   |       | 6.10.2 | Hybrid I |                                         | •           |              | 10                       |          |

|   |       |        | •        | ansmission                              |             |              | o - 10                   |          |

|   |       |        | Power S  |                                         |             |              |                          |          |

|   | 6.11  |        |          | port & Assembly                         |             |              |                          |          |

|   |       |        | _        | $\operatorname{nstraint} \ldots \ldots$ |             |              |                          |          |

|   |       |        |          | Assembly                                |             |              |                          |          |

|   |       |        |          | r Assembly and Ir                       |             |              |                          |          |

|   |       | 0.11.0 |          | Half Detector As                        |             |              |                          |          |

|   |       |        |          | Mount L0 on the                         | •           |              |                          |          |

|   |       |        |          | Installation of C                       |             |              |                          |          |

|   |       |        |          | Quick Demounti                          | _           |              |                          |          |

|   |       | 6 11 4 |          | r Placement and S                       |             |              |                          |          |

|   |       | 0.11.1 |          | Placement accur                         | •           |              |                          |          |

|   |       |        |          | Survey with trac                        | -           |              |                          |          |

|   |       | 6 11 5 |          | Monitoring                              |             |              |                          |          |

|   |       | 0.11.0 |          | Position Monitor                        |             |              |                          |          |

|   |       |        |          | Radiation Monit                         |             |              |                          |          |

|   |       | 6 11 6 |          | ogram                                   |             |              |                          |          |

|   |       | 0.11.0 |          | Cables                                  |             |              |                          |          |

|   |       |        |          | hybrid                                  |             |              |                          |          |

|   |       |        |          | Inner layer sexta                       |             |              |                          |          |

|   |       |        |          | Arch modules                            |             |              |                          |          |

|   |       |        |          | Cones and space                         |             |              |                          |          |

|   |       |        |          | Full-scale model                        |             |              |                          |          |

|   | 6 19  | Lower  |          |                                         |             |              | - 10 pages               |          |

|   | 0.12  |        |          | ogy options                             |             |              |                          |          |

|   |       | 0.12.1 |          | Hybrid pixels                           |             |              |                          |          |

|   |       |        |          | Deep N-well CM                          |             |              |                          |          |

|   |       |        |          | Monolithic pixel                        |             |              |                          |          |

|   |       | 6 19 9 |          | w of the R&D act                        |             |              |                          |          |

|   |       | 0.12.2 |          | Front-end electr                        |             |              |                          | 41       |

|   |       |        | 0.12.2.1 | technology                              |             |              | •                        | 41       |

|   |       |        | 6 12 2 2 | The Apsel DNW                           |             |              |                          |          |

|   |       |        |          | The Apsel DN W                          |             |              |                          |          |

|   |       | 6 19 3 |          | on tolerance                            |             |              |                          |          |

|   | 6 12  |        |          | es and E.S. & H i                       |             |              | 8 pages                  |          |

|   | 0.13  |        |          | and Utilities $\dots$                   |             |              |                          |          |

|   |       |        |          | ssue                                    |             |              |                          |          |

|   |       | 0.13.2 | ES&II I  | ssue                                    |             |              |                          | <br>48   |

| 7 | Drift | t Cham | ber      | _                                       | Finocchia   | ro, Roney 49 | nages                    | 55       |

| - | 7.1   | Overvi |          |                                         |             |              | pages                    |          |

|   | . =   | 7.1.1  |          | requirements                            |             |              | $_{ m iges}$             |          |

|   |       | 7.1.2  |          | rical constraints                       |             | <del>-</del> | page                     |          |

|   |       | 7.1.3  |          | e background cons                       | iderations  | <u>.</u>     | $-2 \text{ pages} \dots$ |          |

|   |       |        |          | 0-1-0-1-0-1-0-1-0-1-0-1-0-1-0-1-0-1-0-1 |             |              | - r-800                  | <br>     |

|      | 7.1.4    | DCH design overview          |                                 | - 2 pages        |                           |      | . 55 |

|------|----------|------------------------------|---------------------------------|------------------|---------------------------|------|------|

|      | 7.1.5    | Expected performance         |                                 | - 2 pages        |                           |      | . 55 |

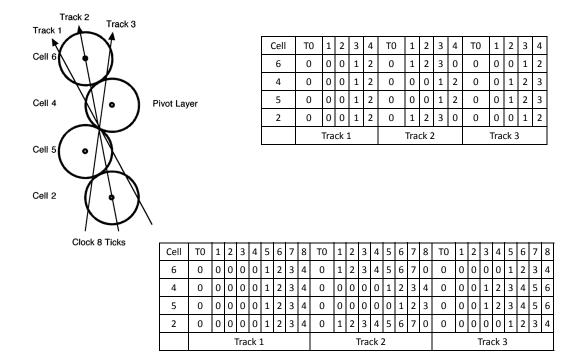

|      | 7.1.6    | Tracking software and patt   | tern recognition                |                  | ages                      |      |      |

| 7.2  | Optim    | zation of chamber operatio   | n - Finocchiaro,                | -                | _                         |      |      |

|      | 7.2.1    | Prototype studies            |                                 |                  |                           |      |      |

|      | 7.2.2    | Gas Mixture Optimization     |                                 |                  |                           |      |      |

|      |          |                              | nce considerations              |                  |                           |      |      |

|      |          |                              | elds, gas gain                  |                  |                           |      |      |

|      | 7.2.3    | Cluster Counting             | , 0                             |                  |                           |      |      |

| 7.3  |          | sign and layer arrangement   |                                 |                  |                           |      |      |

| 7.4  |          | nical Design                 |                                 |                  |                           |      |      |

|      | 7.4.1    | Endplates                    |                                 |                  |                           |      |      |

|      | 7.4.2    | Inner cylinder               |                                 |                  |                           |      |      |

|      | 7.4.3    | Outer Cylinder               |                                 |                  |                           |      |      |

|      | 7.4.4    | Choice of wire and electros  |                                 |                  |                           |      |      |

|      | 7.4.5    | Feed-through design          |                                 |                  |                           |      |      |

|      | 7.4.6    | Endplate system              |                                 |                  |                           |      |      |

|      | 1.4.0    |                              | letector boards                 |                  |                           |      |      |

|      |          |                              | · · · · · · · · · · · · · · · · |                  |                           |      |      |

|      |          | _                            |                                 |                  |                           |      |      |

|      | 7.4.7    | Stringing                    |                                 |                  |                           |      |      |

| 7.5  | Electro  |                              |                                 | n 1 page         |                           |      |      |

| 7.6  |          | oltage system                |                                 | in 1 page        |                           |      |      |

| 1.0  | 7.6.1    | Main HV system               |                                 |                  |                           |      |      |

|      | 7.6.2    | Distribution boards          |                                 |                  |                           |      |      |

| 7.7  | Gas sy   |                              |                                 | pages            |                           |      |      |

| 7.8  |          | ation and monitoring         | •                               | toney 3 pages    |                           |      |      |

| 1.0  | Calibr   | 9                            | $\mathrm{ems}\dots\dots$        |                  |                           |      |      |

|      |          |                              |                                 |                  |                           |      |      |

|      |          |                              | $\operatorname{ystem}$          |                  |                           |      |      |

|      |          | 9                            |                                 |                  |                           |      |      |

| 7.9  | Integra  |                              | - Hearty, Laucia                |                  |                           |      |      |

| 1.0  |          | Overall geometry and med     | • /                             |                  |                           |      |      |

|      | 7.9.2    | Cable supports and routing   |                                 |                  |                           |      |      |

|      | 7.9.3    | Access                       | -                               |                  |                           |      |      |

|      | 7.9.4    | Gas system                   |                                 |                  |                           |      |      |

|      | 7.9.5    | Off-detector electronics cra |                                 |                  |                           |      |      |

|      | 7.9.6    | High voltage crates          |                                 |                  |                           |      |      |

|      | 7.9.7    | Installation and alignment   |                                 |                  |                           |      |      |

| 7.10 |          | Program                      | - Finocchiaro, P                |                  |                           |      |      |

| 1110 |          | Results                      |                                 | • •              |                           |      |      |

|      | 7.10.2   |                              |                                 |                  |                           |      |      |

|      |          |                              |                                 |                  |                           |      | . 00 |

| Part | icle Ide | ntification                  |                                 |                  |                           |      | 61   |

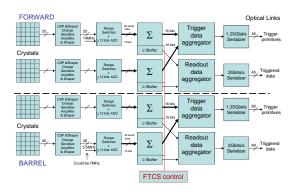

| 8.1  | Sumn     | ary of Physics Requiremen    | ts and Detector Po              | erformance goals | $3-4 \text{ pag}\epsilon$ | es . | . 61 |

|      | 8.1.1    | Physics requirements         |                                 |                  |                           |      | . 61 |

|      | 812      | Detector concept             |                                 |                  |                           |      | 61   |

|      | 8.1.3      | Charged Particle Identification                                    |

|------|------------|--------------------------------------------------------------------|

| 8.   | 2 Partic   | le Identification Overview 2-3 pages                               |

|      | 8.2.1      | Experience of BABAR DIRC                                           |

|      | 8.2.2      | Barrel PID: Focusing DIRC (FDIRC)                                  |

| 8.   | 3 Projec   | eted Performance of FDIRC 2-3 pages                                |

|      | 8.3.1      | Reconstruction Arnaud, Roberts                                     |

|      | 8.3.2      | MC Simulation                                                      |

|      | 8.3.3      | Effect of Background on performance Roberts, Arnaud, Cenci, Vavra, |

|      |            | Kravchenko                                                         |

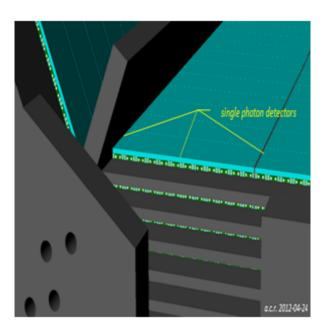

| 8.   |            | farrel FDIRC Detector Overview 5-10 pages                          |

|      | 8.4.1      | Impact on other systems Benettoni, Simi, Vavra                     |

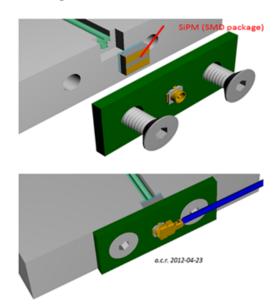

|      | 8.4.2      | Photodetectors                                                     |

|      | 8.4.3      | Laser calibration system                                           |

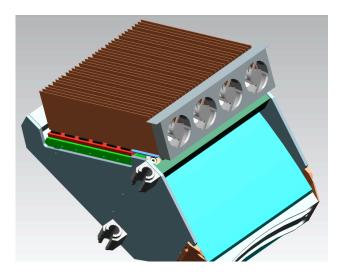

|      | 8.4.4      | FDIRC Mechanical Design                                            |

|      | 8.4.5      | Electronics readout, High and Low voltage                          |

|      | 8.4.6      | Integration issues 2 pages                                         |

|      | 8.4.7      | DAQ and computing 1 page                                           |

|      | 8.4.8      | FDIRC R&D Results until now 2-3 pages                              |

|      | 8.4.9      | Ongoing FDIRC R&D                                                  |

|      | 8.4.10     | System Responsibilities and Management                             |

|      | 8.4.11     | Cost, Schedule and Funding Profile                                 |

| In   | strumente  | ed Flux Return 105                                                 |

| 9.   | 1 Perform  | nance Optimization                                                 |

|      | 9.1.1      | Identification Technique                                           |

|      | 9.1.2      | Baseline Design Requirements                                       |

|      | 9.1.3      | Design Optimization and Performance Studies                        |

| 9.   |            | $ m 	extsf{Vork}$                                                  |

|      |            | R&D Tests and Results                                              |

|      | 9.2.2      | Prototype                                                          |

| 9.   |            | ne Detector Design                                                 |

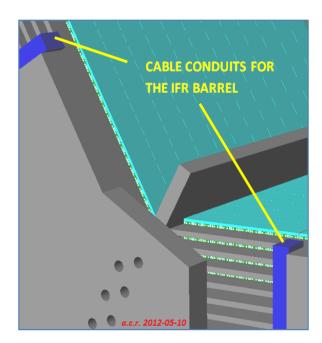

|      | 9.3.1      | Flux Return                                                        |

| .0 M | agnet and  | i Flux Return 113                                                  |

| 1 EI | ectronics, | Trigger, Data Acquisition and Online 115                           |

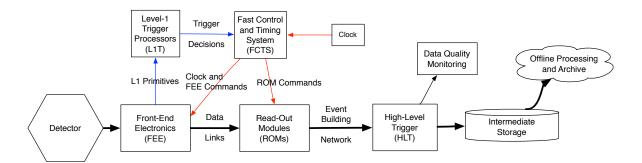

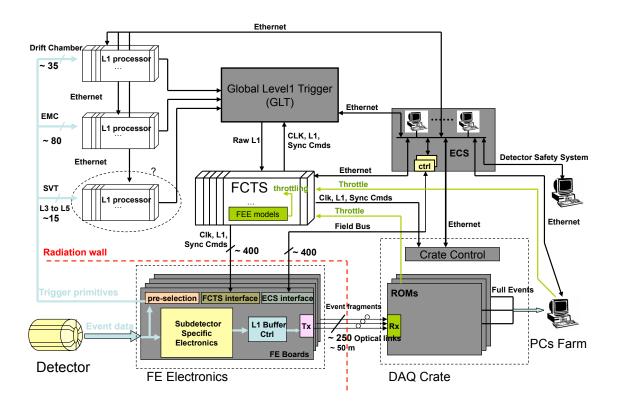

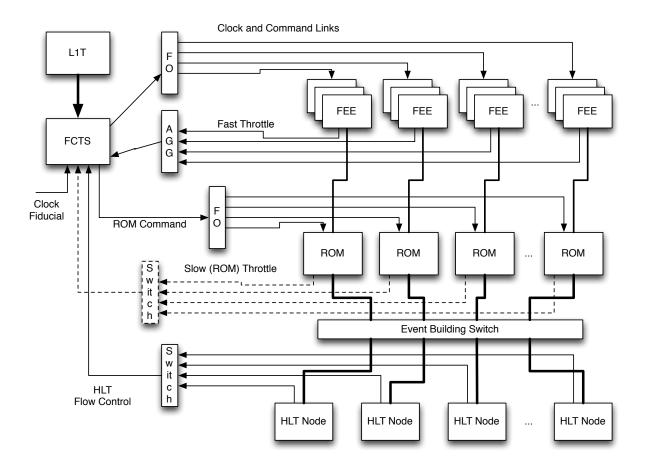

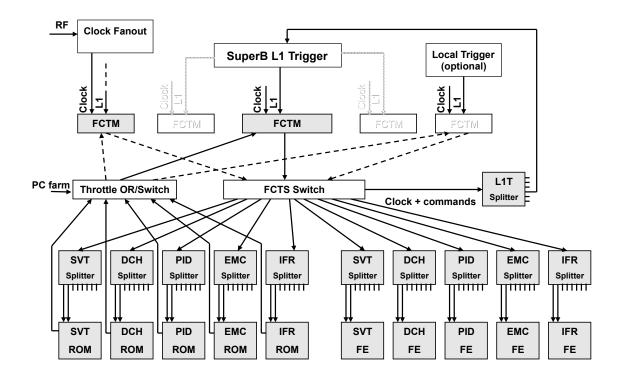

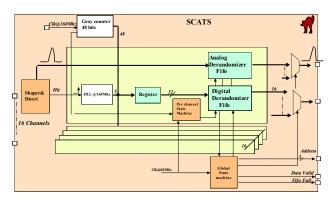

|      |            | ecture Overview                                                    |

|      | 11.1.1     | Trigger Strategy                                                   |

|      | 11.1.2     | Trigger Rate and Event Size Estimation                             |

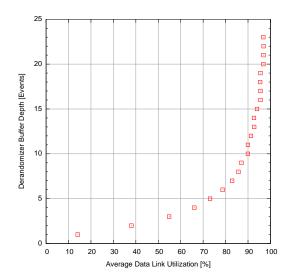

|      | 11.1.3     | Dead Time and Buffer Queue Depth Considerations                    |

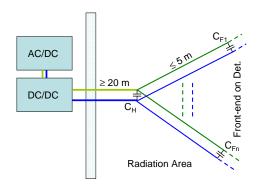

| 11   | .2 Electro | onics in the SuperB Radiation Environment                          |

| 11   | .3 Trigger | and Event Data Chain                                               |

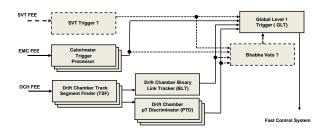

|      | 11.3.1     | Level-1 Trigger                                                    |

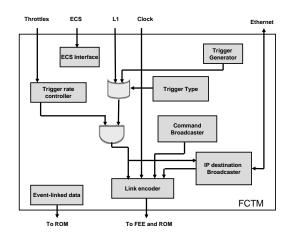

|      |            | Fast Control and Timing System                                     |

|      |            | Control and Data Links                                             |

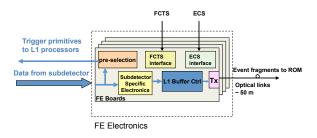

|      |            | Common Front-End Electronics                                       |

|      |            | Read-Out Modules                                                   |

|      | 11.3.6     | Network Event Builder                                              |

|    |      | 11.3.7   | High-Lev            | rel Trigger Farm                                                   |

|----|------|----------|---------------------|--------------------------------------------------------------------|

|    |      | 11.3.8   | Data Log            | gging                                                              |

|    | 11.4 | System   | Integrat            | ion and Error Handling                                             |

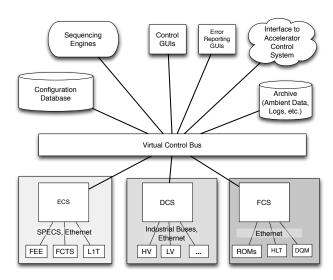

|    | 11.5 | Control  | l Systems           | 130                                                                |

|    |      | 11.5.1   | Electroni           | cs Control System                                                  |

|    |      | 11.5.2   | Detector            | Control System                                                     |

|    |      |          |                     | ntrol System                                                       |

|    | 11.6 |          |                     |                                                                    |

|    |      |          |                     | ality Monitoring System                                            |

|    |      |          |                     | omponents                                                          |

|    |      |          |                     | Infrastructure                                                     |

|    |      |          |                     | onics, Trigger and Data Acquisition and Online                     |

|    |      |          |                     | Structure of Electronics, Trigger, Data Acquisition and Online 134 |

|    | 11.9 | Conclus  | sions               |                                                                    |

| 12 | Suba | detector | Flectro             | nics and Infrastructure 137                                        |

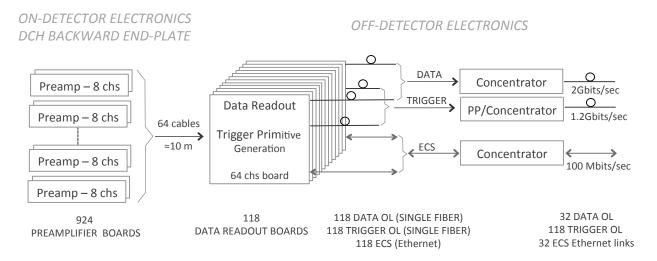

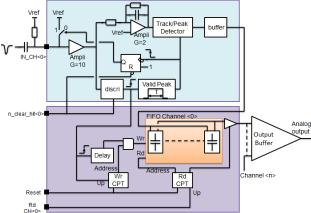

|    |      |          |                     | fic Electronics                                                    |

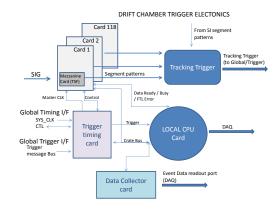

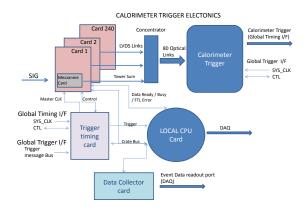

|    | 12.1 |          | -                   | ctronics                                                           |

|    |      |          |                     | ectronics                                                          |

|    |      |          |                     | Design Goals                                                       |

|    |      |          | 12.1.2.2            | Standard Readout - charge measurements specifications 139          |

|    |      |          | 12.1.2.3            | Standard Readout - time measurements specifications                |

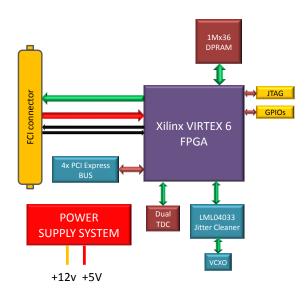

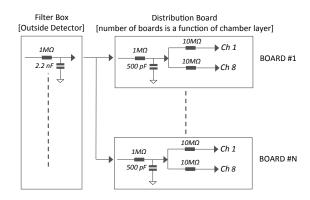

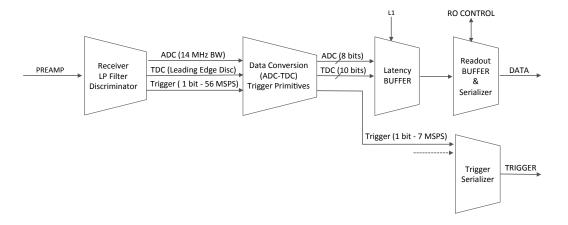

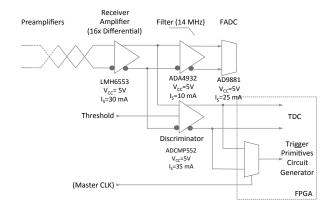

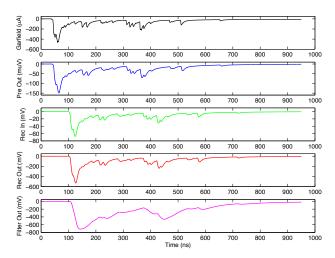

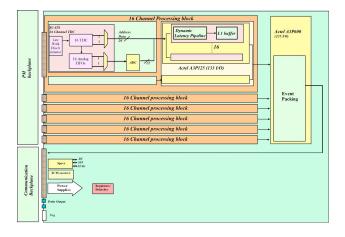

|    |      |          | 12.1.2.4            | Standard Readout - DCH Front-end system (block diagram) 141        |

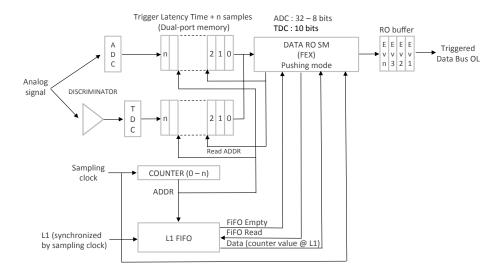

|    |      |          | 12.1.2.5            | Standard Readout - ON-DETECTOR electronics                         |

|    |      |          | 12.1.2.6            | Standard Readout - OFF DETECTOR electronics                        |

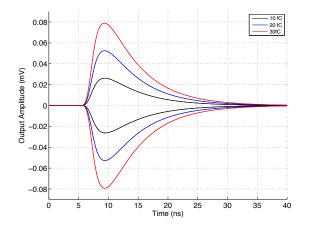

|    |      |          | 12.1.2.7            | Sampled Waveforms - specifications                                 |

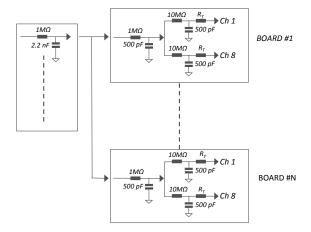

|    |      |          | 12.1.2.8            | Sampled Waveforms - DCH front-end system (block diagram) $$ 145    |

|    |      |          | 12.1.2.9            | Sampled Waveforms - ON DETECTOR electronics 145                    |

|    |      |          |                     | Sampled Waveforms - OFF DETECTOR electronics 145                   |

|    |      |          |                     | Front End Crates                                                   |

|    |      |          |                     | Number of crates and links                                         |

|    |      |          |                     | ECS                                                                |

|    |      |          |                     | Cabling                                                            |

|    |      |          |                     | Power Requirements                                                 |

|    |      |          |                     | Grounding                                                          |

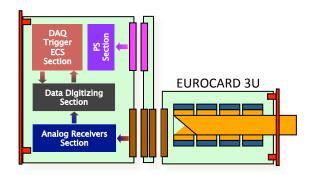

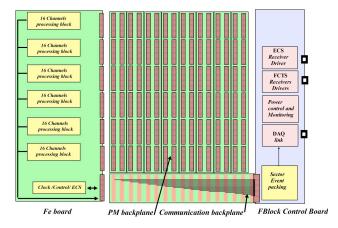

|    |      |          |                     | etronics                                                           |

|    |      |          | 12.1.3.1 $12.1.3.2$ | The TDC chip                                                       |

|    |      |          | _                   | The Communication Backplane                                        |

|    |      |          | 12.1.3.4 $12.1.3.4$ | The PMT Backplane                                                  |

|    |      |          | 12.1.3.4 $12.1.3.5$ | Cooling and power supply                                           |

|    |      |          | 12.1.3.6 $12.1.3.6$ | The front-end board                                                |

|    |      |          |                     | The crate controller board (FBC)                                   |

|    |      |          |                     | ectronics                                                          |

|    |      |          |                     | tronics                                                            |

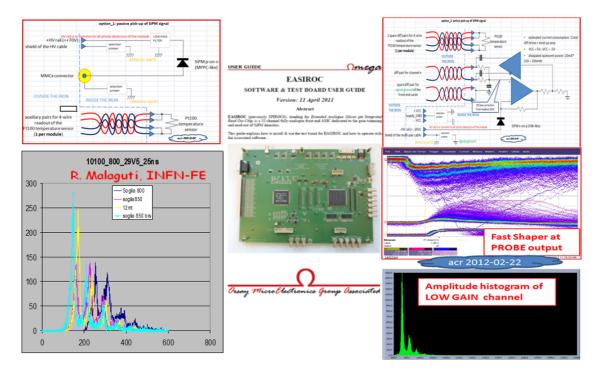

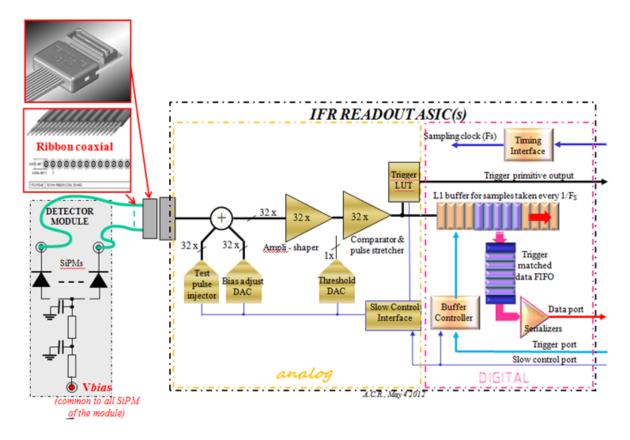

|    |      |          |                     | Introduction                                                       |

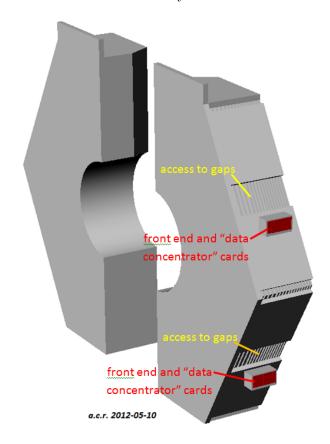

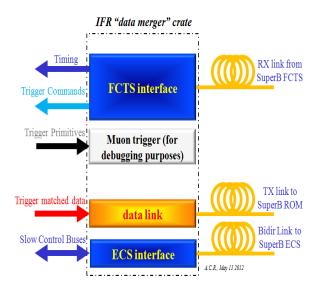

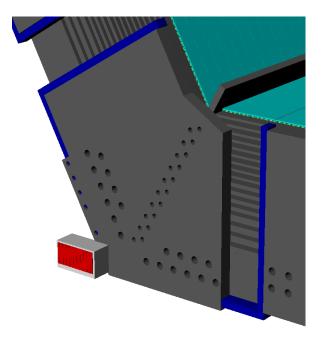

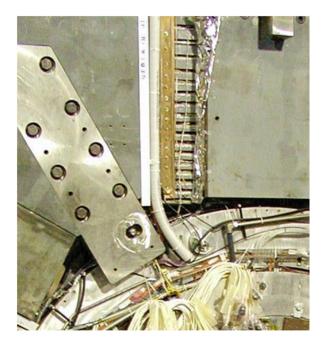

|    |      |          |                     | Basic features of the IFR detector                                 |

|    |      |          |                     |                                                                    |

|    |      |         | 12.1.5.3  | IFR channel count estimates           | $\operatorname{mation}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 153 |

|----|------|---------|-----------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

|    |      |         | 12.1.5.4  | Estimations of the IFR                | event size and data bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 153 |

|    |      |         | 12.1.5.5  | Background radiation a                | and electronics design constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 154 |

|    |      |         |           |                                       | m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |     |

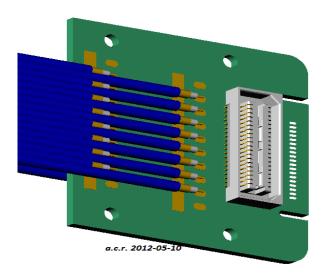

|    | 12.2 | Electro |           | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |     |

|    |      |         |           |                                       | $\operatorname{abling}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |     |

|    |      | 12.2.1  |           | . , ,                                 | cont-end:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |     |

|    |      |         |           |                                       | pply to the Detectors:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |     |

|    |      | 1999    |           |                                       | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |     |

|    |      |         |           | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |     |

|    |      | 12.2.0  | Cubic 1   | collo                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • | 100 |

| 13 | Soft | ware ar | nd Comp   | uting                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 163 |

|    |      |         | iting Ove |                                       | F.Bianchi 2 pages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 163 |