### **Peripheral Electronics**

#### **Mauro Citterio**

#### **INFN Milano**

Mauro Citterio - SVT Parallel - Frascati

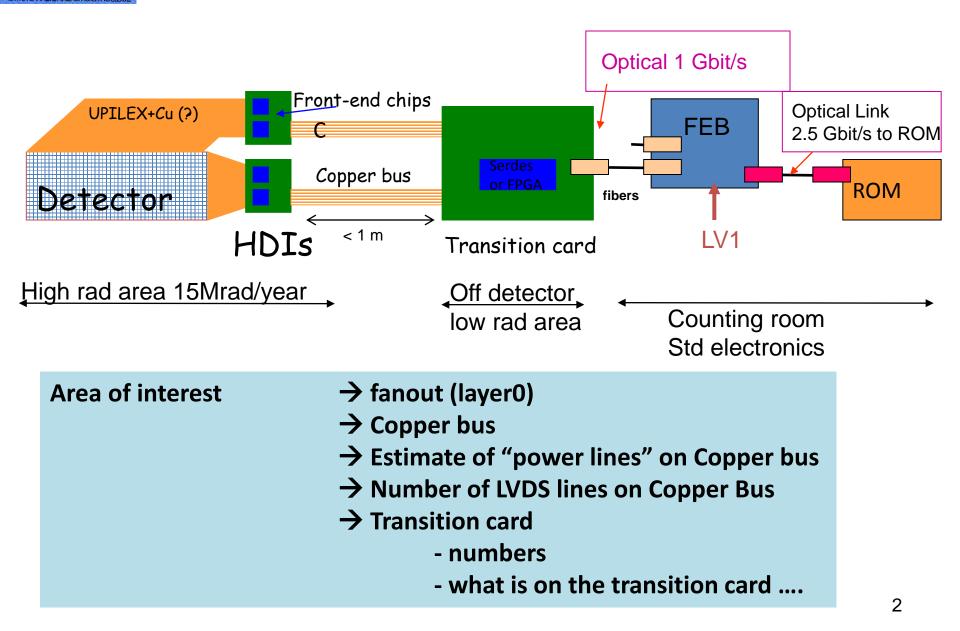

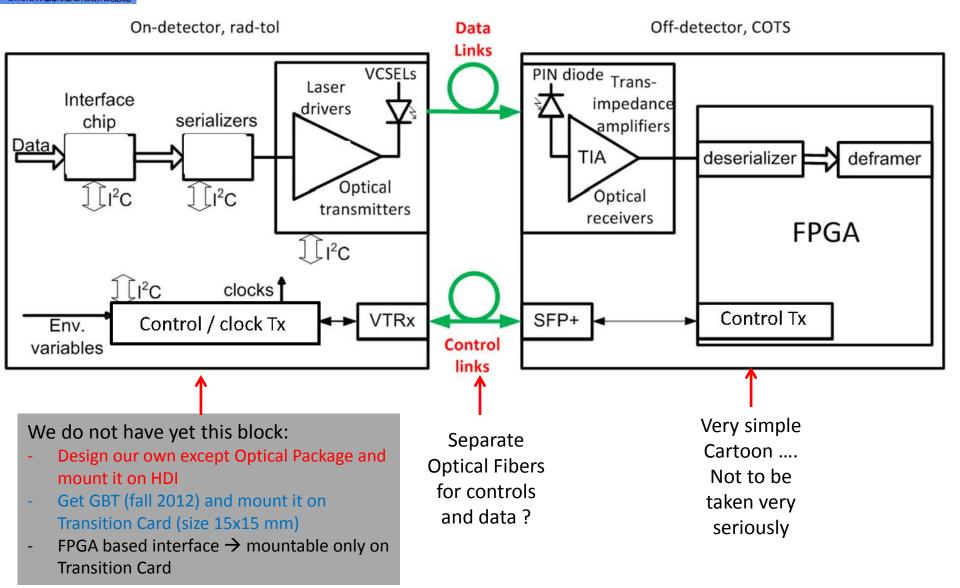

# DAQ reading chain for LO-L5

# Fanout (layer 0)

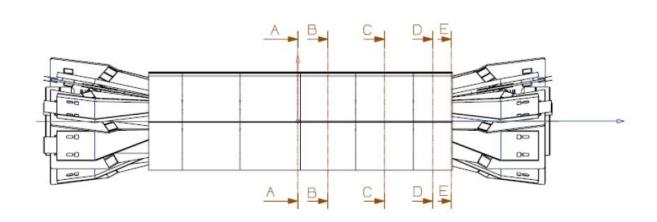

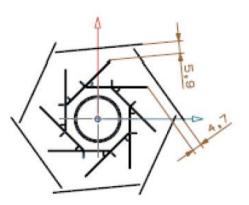

Absolute reference point (0,0) in scaling detector size

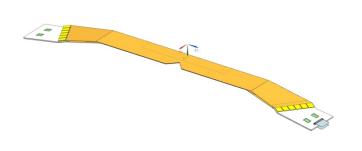

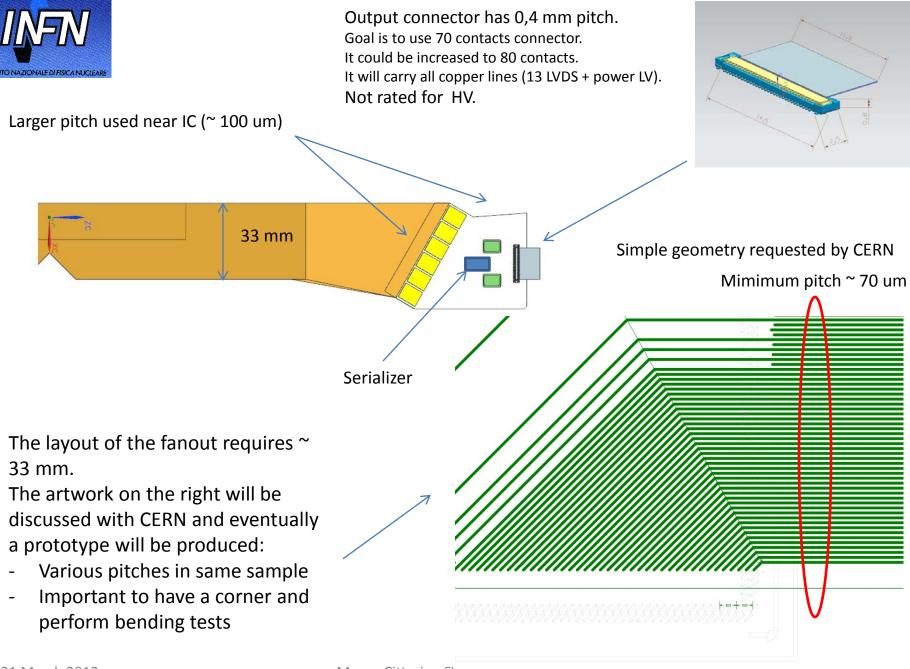

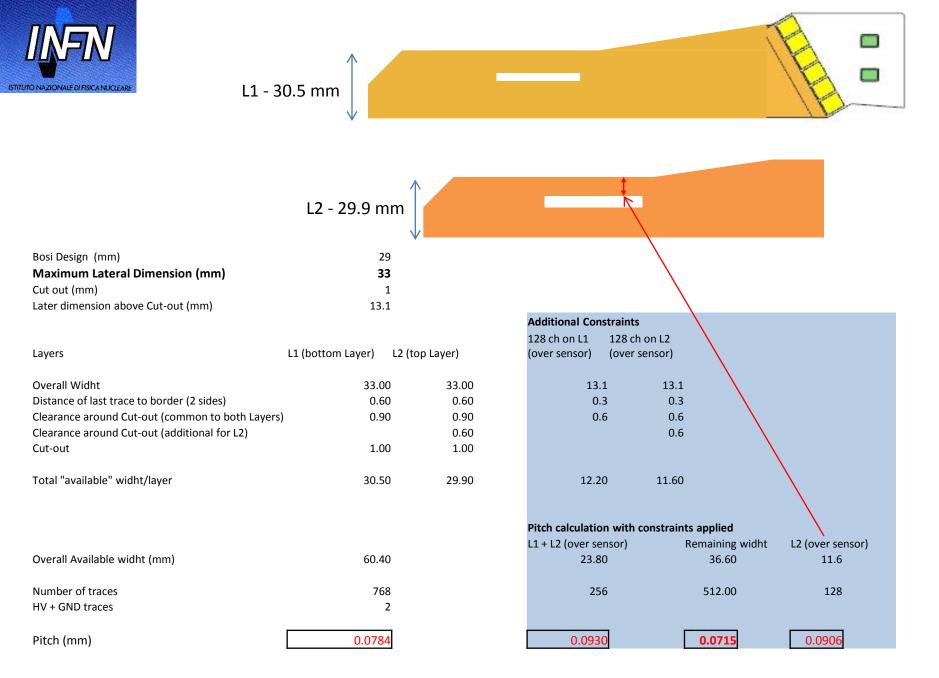

Design progressing on Aluminum/Kapton 2 layer fanout

- $\rightarrow$  Fanout min. pitch proposed is 71 um

- $\rightarrow$  Bonding always toward detector side

- $\rightarrow$  Some constraints applied on how traces match IC channel sequence

- → Fanout resistance estimate is still approximate ~ 0.85 ohm/cm (assuming Aluminum resistivity ~ 33 ohm x m x 10<sup>-9</sup>). Capacitance not yet estimated.

- $\rightarrow$  Narrow pitch needed over a length of ~ 50 mm

- $\rightarrow$  Cern suggestions:

- Minimize the area where the pitch is 71 um

- Perform a test on one layer to verify reliability/consistency of pitch

- Concern about bending such a fine lines (perform resistance test before and after banding) on first comple

- bending) on first sample

- Spread lines before reaching bonding

- $\rightarrow$  Overall fanout width 33 mm  $\rightarrow$  It should fit in the existing CAD model of detector

TUTO NAZIONALE DI FISICA NI

29

#### Two Layers Al Fanout: layout requires 33 mm

# **Dimensional Studies**

C-C

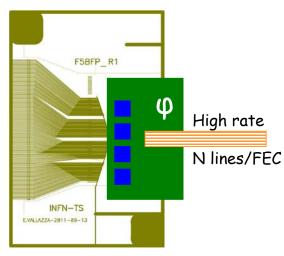

# HDI and output bus

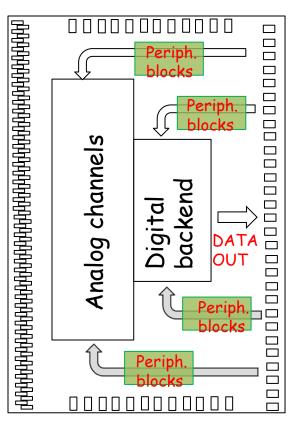

Minimal number of elements on HDI (ideally only FE chips and possibly a serializer)

6 shared input lines: Reset, Clock, FastClock, Timestamp, Trigger, RegIn 1 shared output line: RegOut N lines × M chips in output Ground and powering on the bus Signal lines in standard LVDS (CMOS to/from LVDS required on HDI if not provided on FE)

- HDI elements should be:

- Rad-hard characteristics dependent on chips

- Requirement: > 5 Mrad/year

- Power dissipation: < 1 W/chip (guess-estimate, past values)

- Option for a serializer on HDI

### Number of Transition Cards and Copper Bus

| L0<br>L1<br>L2 | Top<br>Bottom<br>Z<br>Phi<br>Z<br>Phi | 8<br>6<br>6 | 16<br>12<br>12 | 6<br>6<br>7<br>7<br>7<br>7<br>7            | 12<br>12<br>7<br>14<br>7<br>7<br>7 | 32<br>24<br>24 | 16<br>12<br>12 | 32<br>24<br>24 | 32<br>24<br>24 |

|----------------|---------------------------------------|-------------|----------------|--------------------------------------------|------------------------------------|----------------|----------------|----------------|----------------|

| L3<br>L4       | Z<br>Phi<br>Z                         | 6<br>16     | 12<br>32       | 10<br>6<br>5                               | 10<br>6<br>5                       | 24<br>64       | 12<br>16       | 24<br>32       | 24<br>32       |

| L5             | Phi<br>Z<br>Phi                       | 18          | 36             | 4<br>5<br>4                                | 4<br>5<br>4                        | 72             | 18             | 36             | 36             |

| Total          |                                       |             | 12             | 0                                          |                                    | 240            | 86             | 172            | 172            |

| P              | roposa                                | al: 1 Tra   | ansitio        | 2 copper<br>bus for TC<br>Layer<br>0,1,2,3 | 2 Fiber for<br>TC                  |                |                |                |                |

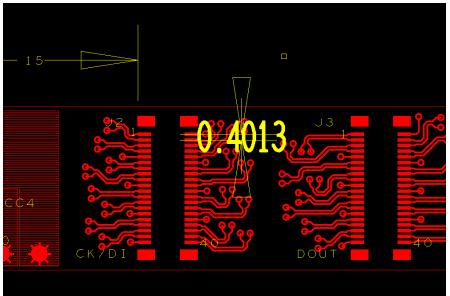

Proposal: 1 Transition Card accept at least 2 Copper Bus !!! Why? To increase size of TC  $\rightarrow$  shown later Number of LVDS lines on copper bus is limited !!!

4 copper bus for TC Layer 4,5

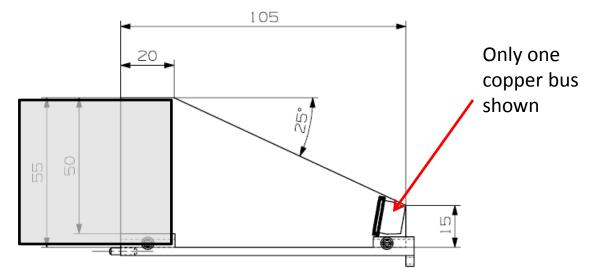

# **Copper Bus Structure**

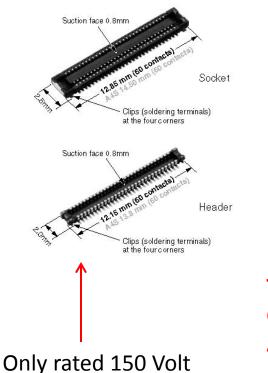

1. The world's smallest size\* (width: 2.5 mm, Terminal pitch: 0.35 mm and Mated height: 0.8 mm) The footprint when mated is down approx. 10% from our existing A4S model (60 contacts), contributing to the functionality enhancement and size reduction of target equipment.

For various reasons the wisted pair wire solution I proposed in the past (magnet wires) is not as simple as I thought. We will continue to study it but we need to investigate a different solution:

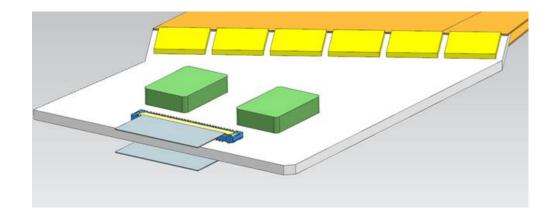

The copper bus is becoming a 3 layer Copper/Kapton Tape. Aspect ratio: ~ 10 mm x 400-500 mm At the connector the tape is ~ 17 mm wide

Width of Copper bus is determined by geometrical reasons:

Dimension of Transition Card Routing of Bus (an example is shown on bottom)

Mauro Citterio - SVT Parallel - Frascati

### **Copper Bus Structure**

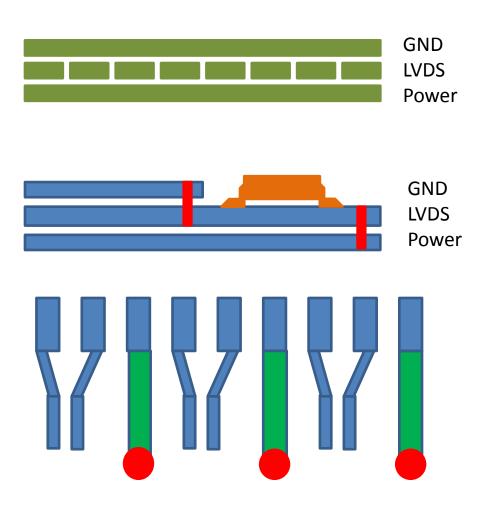

Stack-up Design Rules:

LVDS Lines: Strip lines LVDS Lines: 4 mils LVDS Space: 4 mils LVDS Copper Thickness ~ 20 um (~½ ounce)

Dielectric Thickness: ~ 100 mils Zdiff ~ 100 Ohm To be optimized

Kapton Thickness: 2 mils (?)

Via Diameter: 10-12 mils Via Clearance: 6 mils

Power/Gnd Planes: Widht ~ 4.7 mm (almost double for GND !!) Thickness > 50 um (or 2 ounces) Current capability ~ 3-3.5 Amps Voltage drop (both ways) ~ 250 mV

### **Copper Bus Structure**

| <br>GND      | 1  | 36 | GND       |  |

|--------------|----|----|-----------|--|

| D1+          | 2  | 37 | Reg Out + |  |

| D1-          | 3  | 38 | Reg Out - |  |

| GND          | 4  | 39 | GND       |  |

| D2+          | 5  | 40 | Power 1   |  |

| D2-          | 6  | 41 | Power 1   |  |

| GND          | 7  | 42 | Power 1   |  |

| D3+          | 8  | 43 | Power 1   |  |

| D3-          | 9  | 44 | Power 1   |  |

| GND          | 10 | 45 | Power 1   |  |

| D4+          | 11 | 46 | Power 1   |  |

| D4-          | 12 | 47 | Power 1   |  |

| GND          | 13 | 48 | Power 1   |  |

| D5+          | 14 | 49 | Power 1   |  |

| D5-          | 15 | 50 | Power 1   |  |

| GND          | 16 | 51 | Power 1   |  |

| D6+          | 17 | 52 | Power 1   |  |

| D6-          | 18 | 53 |           |  |

| GND          | 19 | 54 | Power 2   |  |

| Trigger +    | 20 | 55 | Power 2   |  |

| Trigger -    | 21 | 56 | Power 2   |  |

| GND          | 22 | 57 | Power 2   |  |

| TimeStamp +  | 23 | 58 | Power 2   |  |

| Time Stamp - | 24 | 59 | Power 2   |  |

| GND          | 25 | 60 | Power 2   |  |

| Clock +      | 26 | 61 | Power 2   |  |

| Clock -      | 27 | 62 | Power 2   |  |

| GND          | 28 | 63 | Power 2   |  |

| Fast Clock + | 29 | 64 | Power 2   |  |

| Fast Clock - | 30 | 65 | Power 2   |  |

| GND          | 31 | 66 | Power 2   |  |

| Reset +      | 32 | 67 | GND       |  |

| Reset -      | 33 | 68 | Reg In +  |  |

| GND          | 34 | 69 | Reg In -  |  |

| Not Assigned | 35 | 70 | GND       |  |

#### Courtesy of C. Gemme – IBL Flex Project

Mauro Citterio - SVT Parallel - Frascati

# Still a serious puzzle .....

Even with the proposed design  $\rightarrow$  not enough LVDS lines to match the HDI Data output lines:

→ 7 shared lines → 6 Data Output Lines

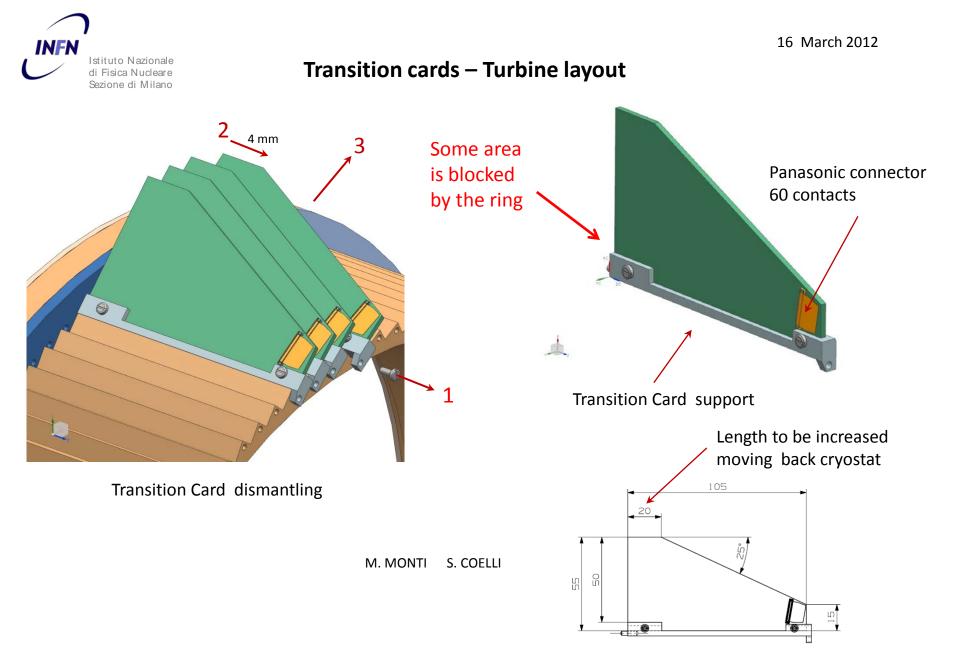

Increasing number of contacts on Panasonics?

$\rightarrow$  Max number of contacts is 80

$\rightarrow$  Max data out lines will become 9

From previous table Number of HDI Data lines which are critical

→ 12 on L0 → 14 on L1 Phi → 10 on L3 Z

Possible Solution .....

Having a 1:2 MUX on each HDI

Chip with 256 channels

- Frequency on LVDS increases → to be verified

### Where are the logic blocks located.....

M

ISTITUTO NAZIONALE DI FISICA NUCLE

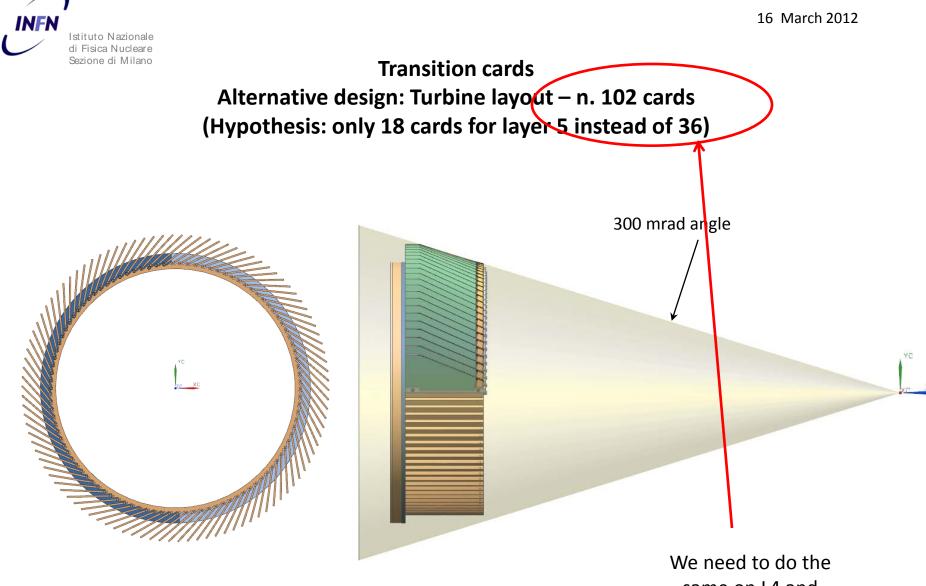

same on L4 and reduce to 86 cards

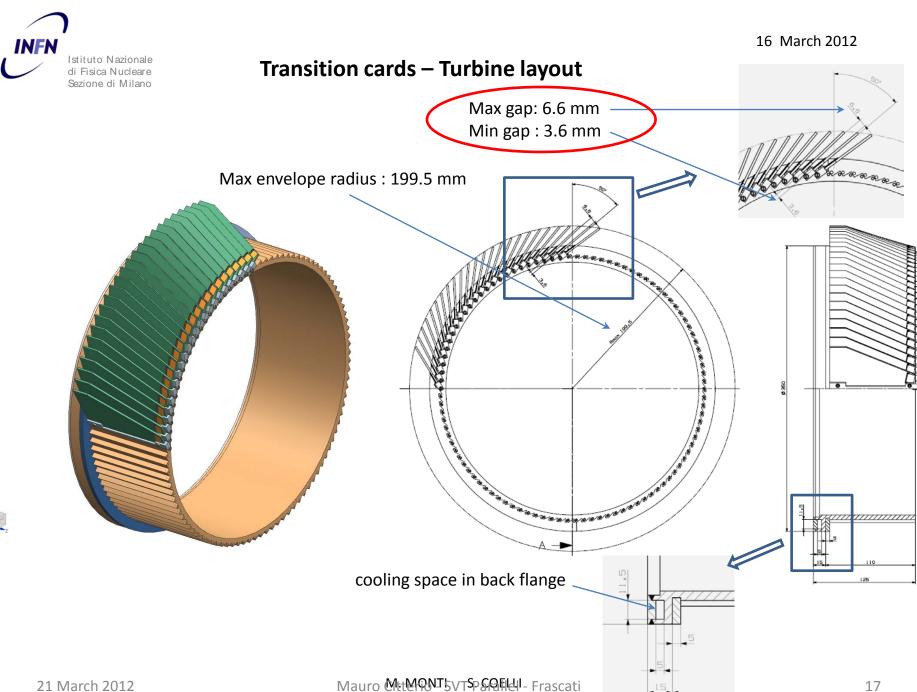

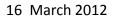

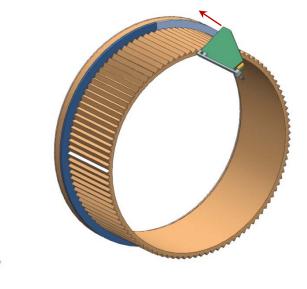

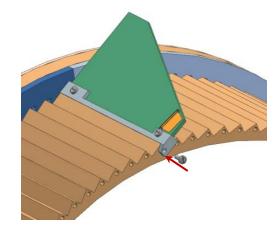

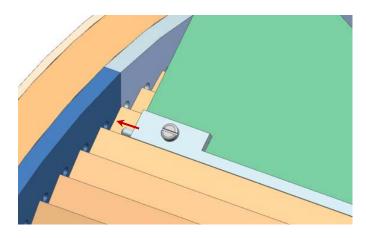

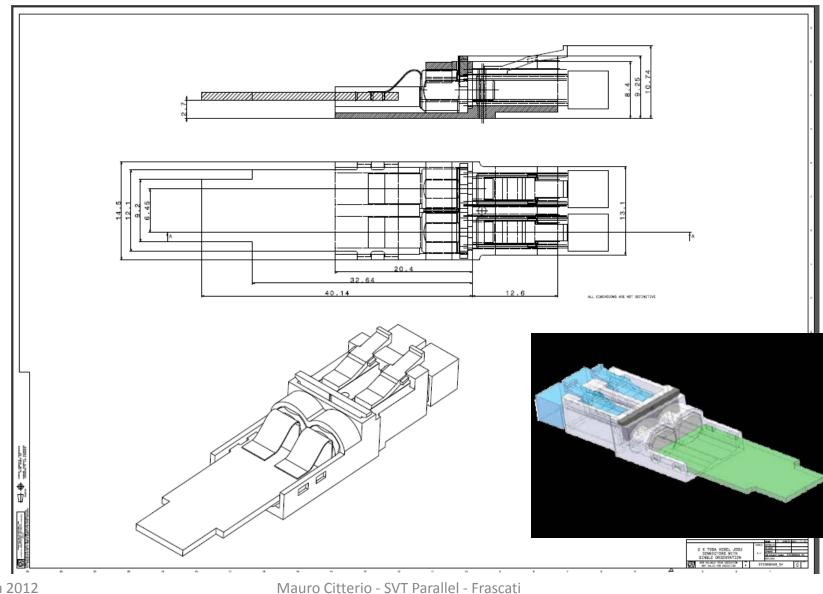

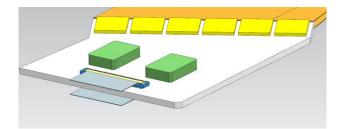

#### **Transition cards – Turbine layout assembling**

M. MONTI S. COELLI

INFN

Istituto Nazionale

di Fisica Nucleare Sezione di Milano

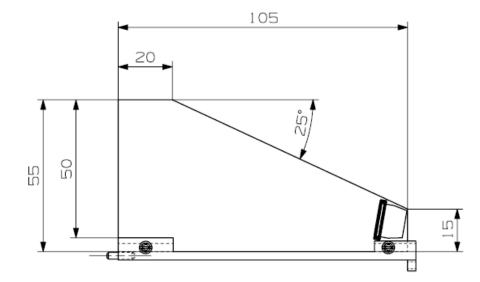

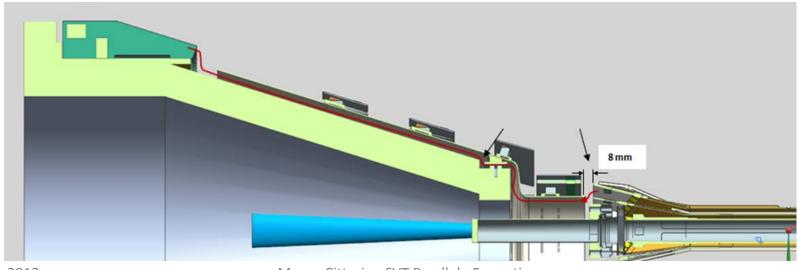

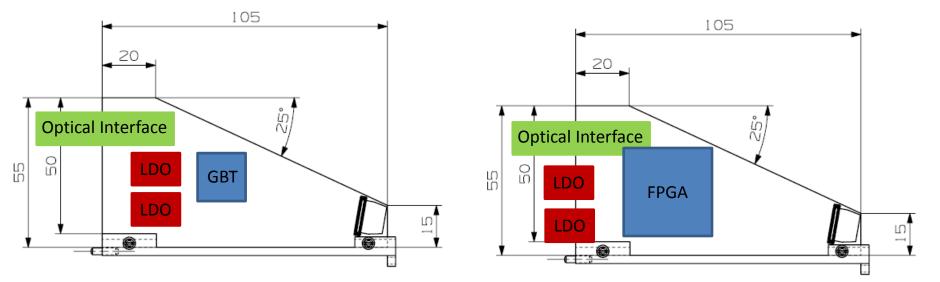

# How much space is needed .....

The "component" blocks have approximately the right dimensions:

- → We need to get more spaces ~ 3-4 cm (grey box)

- → The turbine structure is helping on one side only

#### **Input Power Cables NOT shown**

### HDI

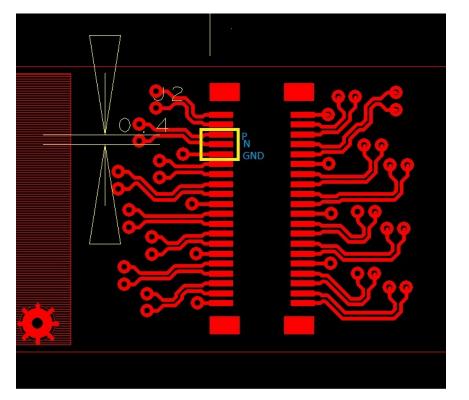

- $\rightarrow$  Layer 0 HDI dimensions

- $\rightarrow$  We should "freeze" the dimensions

- $\rightarrow$  I have started to draw a real "schematic and layout".

- → In the coming days we should agree on some "tentative" pad layout

- $\rightarrow$  No show-stopper up to now

- → Still need to understand if we need to "shielding" between LVDS lines close to the connector

- $\rightarrow$  Clock routing not yet addressed

- $\rightarrow$  Number of layers seems similar to Babar HDI

- → Summary of LVDS lines

- → 3 clocks (System clock, Time Stamp clock, readout clock)

- $\rightarrow$  1 REG In

- $\rightarrow$  1 REG out

- $\rightarrow$  1 Reset

- $\rightarrow$  1 Trigger

- → Max 9 Data lines

# LVDS test in preparation

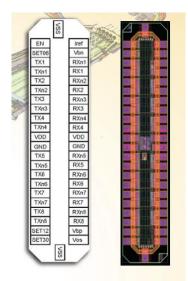

- $\rightarrow$  IC acquired from CERN (8 receivers and 8 transmitters, 6x1.5 mm)

- $\rightarrow$  Extract of info from CERN:

- $\rightarrow$  IBL loads 5.6m of twisted pair cable with this LVDS (FE-I4).

- → Baud rate is 160Mb/s, transmission quality is marginal. Eyeplot is small mostly due to NO pre-empjasis

- → nSPQ uses the same LVDS over a cable lenght (bunch of magnet wires) of 6.3m with a baud rate of 80Mb/s. Bit error rate is < 10E-14.</p>

- → With only one magnet wires baud rate could increase up to 120-130Mb/s, but if a bunch is used «mutual impedance» creates a problem

- $\rightarrow$  We are bonding the IC to a board

- → We will retest performance with multiple magnet wires

→ we would need to interpose shields ?

- → In parallel we will test an LVDC driver designed by Bergamo group

- $\rightarrow$  As soon as the Copper Bus is ready we will repeat the test