## SVT – Update (II)

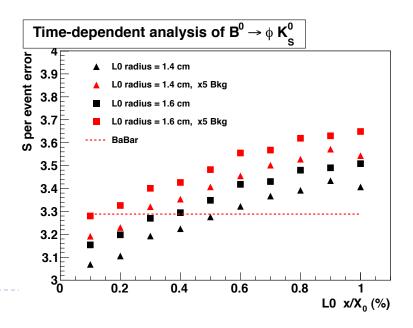

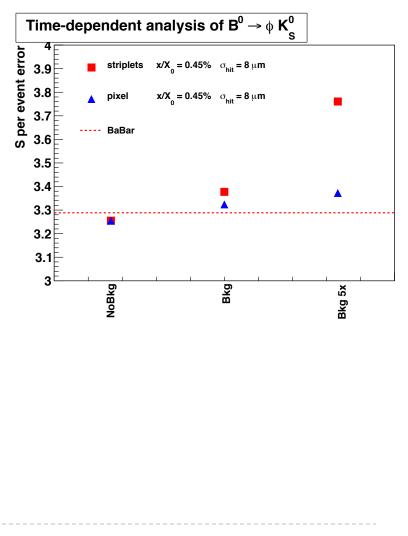

#### 3. Fastim performance comparison for striplets and pixel in Layer0 completed

- ➤ As expected pixel performance more robust in high background (pixel occup. 200 times smaller than striplets) → main motivation for pixel upgrade for full luminosity.

- With x5 background, sensitivity to S reduced by 15% with striplets, while only 3% degradation seen with pixel with same material budget assumed.

- > Thinner pixel options can further improve S sensitivity even with nominal background

# SVT – Update (III)

- 4. Higher neutron fluence found in SVT (bug fix) and effect on FE noise reavaluated

- > S/N marginal in L4-5 with 7.5 yrs x5 safety

- > A few knobs to improve the situation. Reduce:

- Reduce ambient temperature (T=12°C, in this table) & shaping time. Neutron shield in the hall?

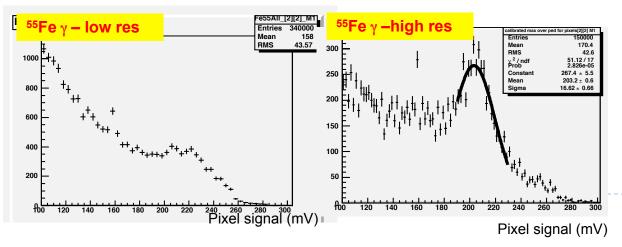

### R&D on pixel:

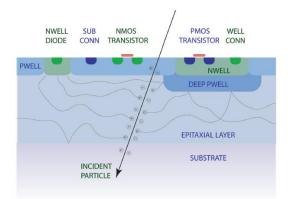

- INMAPS MAPS with high resistivity epi layer under test:

- Better charge collection evident with Fe55 spectrum

- Irradiation with neutrons performed (4 steps up to 1x10^14 n/cm2) and chips are being tested now.

#### > Getting ready for Nov. testbeam at CERN

| Layer | View | Shaping<br>time | S/N at the<br>start of<br>data<br>taking | S/N in 75<br>ab-1 | S/N in 75<br>ab-1 x5<br>bkg |

|-------|------|-----------------|------------------------------------------|-------------------|-----------------------------|

| 0     | 1    | 25              | 17                                       | 17                | 16                          |

| 0     | 2    | 25              | 17                                       | 17                | 16                          |

| 1     | phi  | 75              | 21                                       | 20                | 16                          |

| 1     | z    | 75              | 32                                       | 27                | 18                          |

| 2     | phi  | 100             | 22                                       | 20                | 16                          |

| 2     | z    | 100             | 34                                       | 27                | 18                          |

| 3     | phi  | 150             | 27                                       | 21                | 14                          |

| 3     | z    | 150             | 34                                       | 27                | 16                          |

| 4     | phi  | 500             | 22                                       | 17                | 10                          |

| 4     | z    | 500             | 29                                       | 19                | 11                          |

| 5     | phi  | 750             | 22                                       | 14                | 8                           |

| 5     | Z    | 750             | 30                                       | 18                | 10                          |

INMAPS CMOS process with 4 wells & high resistivity to improve charge collection efficiency and radiation resistance

## SVT – TDR final phase (I)

- Internal revision of the text started on completed sections (~ 75%)

- > Very few people (2!) sent comments on the written parts!

- Some of the parallel sessions devoted to TDR reading to get some more feedback.

- > Mechanics/Silicon sensor chapter is progressing.

- Background still to be written (only 2 pages + table)

- Still nothing in svn from peripheral electronics fanout layer0!

- Tech Board asked to enter in the final editing phase after this Meeting with the goal to publish by the end of October.

- Subsystem final readers appointed (Adrian Bevan for SVT). Should work for 2 weeks starting asap.

- > Final editing by the editorial board for 2 more weeks.

- > This looks a bit optimistic from the status I see today in svn for SVT but I really hope to have all the sections completed by the end of this meeting.

## SVT – TDR final phase (II)

- Need to include budget and schedule for SVT construction and will devote some time in the parallel tomorrow morning to discuss this.

- > Budget used for white paper should be revised

- > Need to include costing for quick demounting: nothing there.

- Refine manpower/cost for technicians and eng. for construction (seems underestimated for some phases)

- Preliminary schedule built looking at BaBar experience + some guess on Layer0 needs and relaxing the final phase of construction w.r.t BaBar.

### Main Assumption: Manpower available

- Assumed 2 main labs (as in BaBar):

- Pisa+UCSB for modules

- LBL+(Pisa) SVT Mechanics

- Pisa+Trieste Silicon sensors

- Pisa+Torino+Ferrara Jigs

- LBL+PV+MI On detector electronics

- UCSC Off Det. Electronics

### Using BaBar SVT Construction Experience + Layer0 needs + more relaxed final phase

|                                  | BABAR        |                                  | comments                                                                                                | SuperB                                                                                                 | end date | comments                                                            |

|----------------------------------|--------------|----------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------|

|                                  | Experience   |                                  | comments                                                                                                | Superb                                                                                                 | enu uate | comments                                                            |

|                                  | months       | date                             |                                                                                                         | months                                                                                                 |          |                                                                     |

| Si sensor design                 | 12           | 95                               |                                                                                                         | 12                                                                                                     |          |                                                                     |

| Si sensor production test        | 18           | mid 96- end 97                   |                                                                                                         | 18                                                                                                     |          |                                                                     |

| DFA                              | 12-18 months | beg full speed<br>july 97 end 98 |                                                                                                         | 18                                                                                                     |          | also L0                                                             |

| chips available                  |              | mid 98                           |                                                                                                         |                                                                                                        |          | prototyping<br>ends in 2 yrs<br>from now. +<br>months<br>production |

| HDI loading                      | 4            | aug 98-nov 98                    | too hard in 4<br>months                                                                                 | 12 m with 6m chips loading starting when chips avaliable                                               | end 2015 | include L0                                                          |

| DFA+HDI L1-2-3                   | 3            | sept - nov 98                    | in UCSB                                                                                                 | module assembly in 2 places 3<br>month for DFA+HDI + 3 months<br>for Module assembly 6 months<br>total | Mar-16   |                                                                     |

| DFA+HDI L4-5                     | 3            | oct-dic 98                       | in PISA at the same<br>time DFA_HDI<br>bonding/testing and<br>Arch construction<br>(2 teams too hard!!) | module assembly in 2 places 3<br>month for DFA+HDI + 3 months<br>for Module assembly 6 months<br>total | Mar-16   |                                                                     |

| Module 1-2-3                     | 2            | oc-nov 98                        | in UCSB                                                                                                 | module assembly in 2 places 3<br>month for DFA+HDI + 3 months<br>for Module assembly 6 months<br>total | mid 2016 |                                                                     |

| Arch 4-5                         | 3            | nov98 jan99                      | in PISA at the same<br>time DFA_HDI<br>bonding/testing and<br>Arch construction<br>(2 teams too hard!!) | module assembly in 2 places 3<br>month for DFA+HDI + 3 months<br>for Module assembly 6 months<br>total | mid 2016 |                                                                     |

| installation on<br>support cones |              | jan-march 99                     |                                                                                                         | 6 months considering L0 too                                                                            | end 2016 |                                                                     |

| installation of SVT              |              | march-june 99                    |                                                                                                         | 3                                                                                                      | Mar-17   |                                                                     |

SuperB Collab. Meeting Pisa – Sept 2012

#### **UPDATED** looking more carefully at BaBar schedule and including Layer0

| Item (months)<br>Construction for<br>Baseline (striplets<br>+SVT) | 2012<br>TDR | 2013<br>Design<br>&<br>Protot. | 2014 | 2015     | 2016 | 2017<br>Commissio<br>ning in<br>SuperB |

|-------------------------------------------------------------------|-------------|--------------------------------|------|----------|------|----------------------------------------|

| Installation (3)                                                  |             |                                |      |          |      | +                                      |

| Final Assembly (6)                                                |             |                                |      |          | ļ    |                                        |

| Module Ass. (Arch-<br>SextantStriplets)(3)                        |             |                                |      |          | +    |                                        |

| DFA+HDI Ass.(3)                                                   |             |                                |      |          | +    |                                        |

| HDI (12)                                                          |             |                                |      |          |      |                                        |

| Chip Production (6)<br>Cannot start before 2015                   |             |                                |      |          |      |                                        |

| DFA (18)                                                          |             |                                |      |          |      |                                        |

| Fanout (15)                                                       |             |                                | •    | <b>→</b> |      |                                        |

| Silicon Sensors (18)                                              |             |                                | •    |          |      |                                        |

| Off Det Electr. (24)                                              |             |                                |      |          |      |                                        |

| Transit. Cards (15)                                               |             |                                | •    |          |      |                                        |

| Mechanics<br>Support Structure (18-24)<br>Module & Jigs (18)      |             |                                | +    |          |      |                                        |

- Started to fill the Smartsheet document with previous inputs.

- Still some inputs on mechanics are needed.

- I'll discuss this schedule with the SVT group during this week.