# Silicon n-in-p Pixel Sensors for future ATLAS Upgrades

A. La Rosa<sup>1</sup>, Ch. Gallrapp <sup>2</sup>, A. Macchiolo <sup>3</sup>, R. Nisius <sup>3</sup>, H. Pernegger <sup>2</sup>, R.H. Richter <sup>4</sup>, P. Weigell <sup>3</sup>

Section de Physique (DPNC) Université de Genève, Genève, Switzerland. <sup>2</sup> CERN, Genève, Switzerland. <sup>3</sup> Max-Planck-Institut für Physik, München, Germany. <sup>4</sup> Max-Plank-Institut Halbleiterlabor, München, Germany.

#### Introduction

#### Sensor description

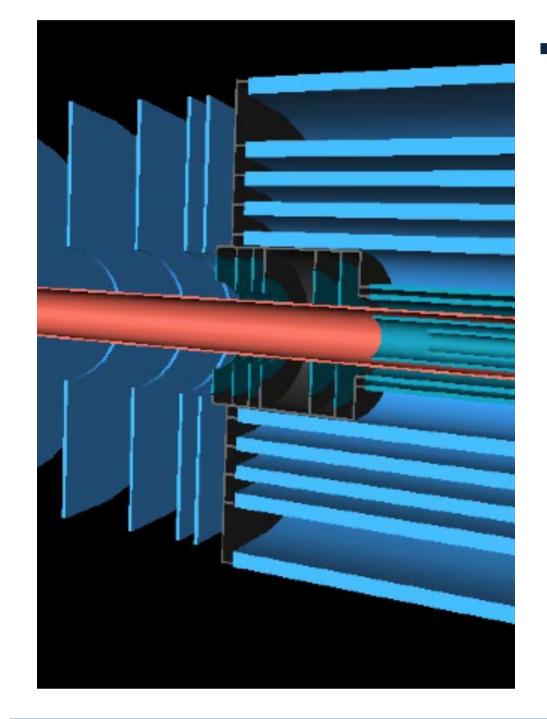

#### ATLAS Pixel Detector Upgrade:

- 2022 (Phase 2): Inner detector Tracker (ITK)

- Complete new ATLAS tracker (Pixel and Ο Strip detectors)

- Much larger Pixel surface w.r.t. current Ο Pixel Detector: ~7-10 m<sup>2</sup>

- Luminosity: 5x10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> Ο

- Radiation dose (innermost layer): Ο 2x10<sup>16</sup> 1-MeV n<sub>eq</sub> cm<sup>-2</sup>

- Planar n-in-p as future sensor technology:

- Excellent candidate for large volume Ο

- Single side processing  $\rightarrow$  reduced cost Ο

- Radiation hardness comparable to n-in-n

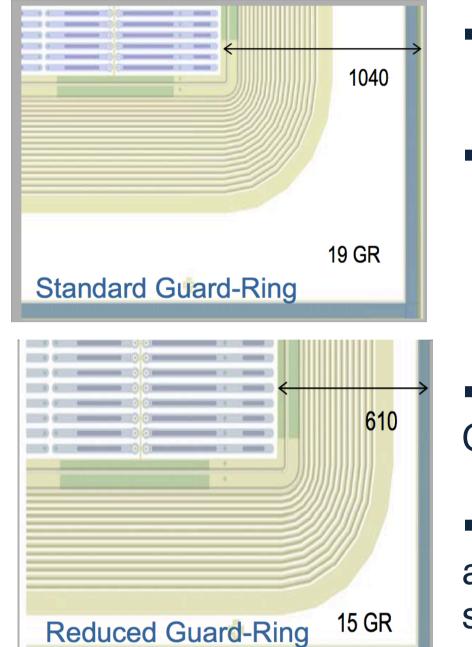

#### First CiS n-in-p Pixel production

- Production on 4" Fz p-type wafer, 285 um thick

- Inter-pixel isolation:

- Moderated p-spray

- Homogeneous p-spray

- Bump bonding to the ATLAS Pixel Front-End Chip (FE-I3) performed by IZM-Berlin

- BCB layer deposited on the sensor front side as an isolation to prevent sparks between sensor and chip

# **Test Results**

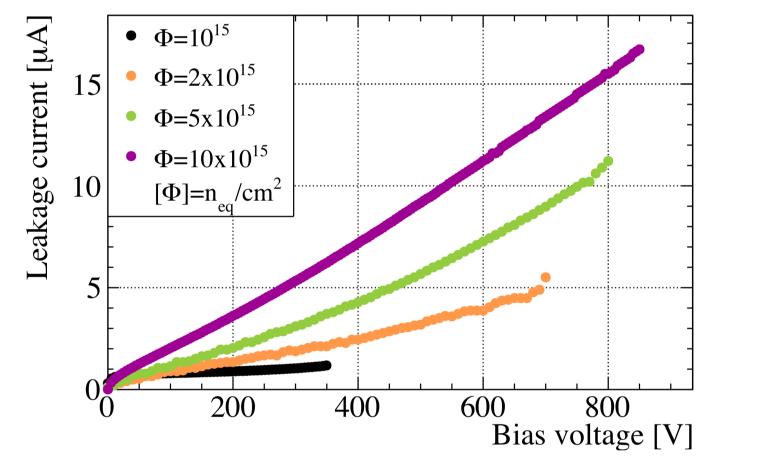

### Leakage currents (after irradiation)

Ο

**Before irradiation (at +20°C)** All modules show leakage currents below 6 uA, with a bias voltage of 150 V [1,2,3].

After irradiation (scaled at -20°C) The breakdown voltages shifted to higher values and for the highest fluence it exceeds 800 V.

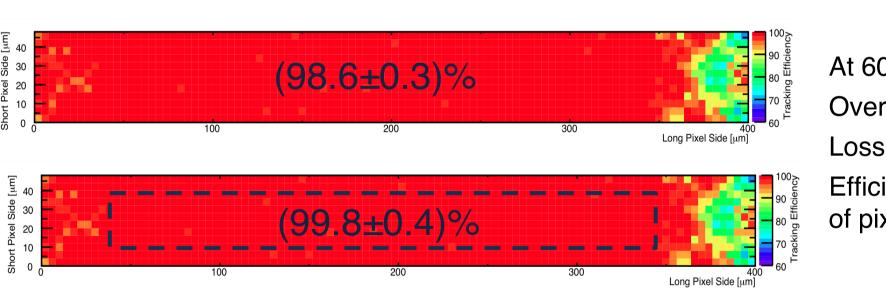

### Beam test at the CERN SPS with a 120 GeV/c π<sup>+</sup> beam

Tracking efficiency

Mean tracking efficiency as a function of the track impact point for a module irradiated up to  $5x10^{15}$  n<sub>eq</sub> cm<sup>-2</sup> and biased at 600V [2,4].

Also the leakage currents show higher values with increasing fluences.

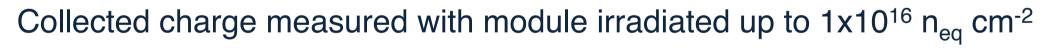

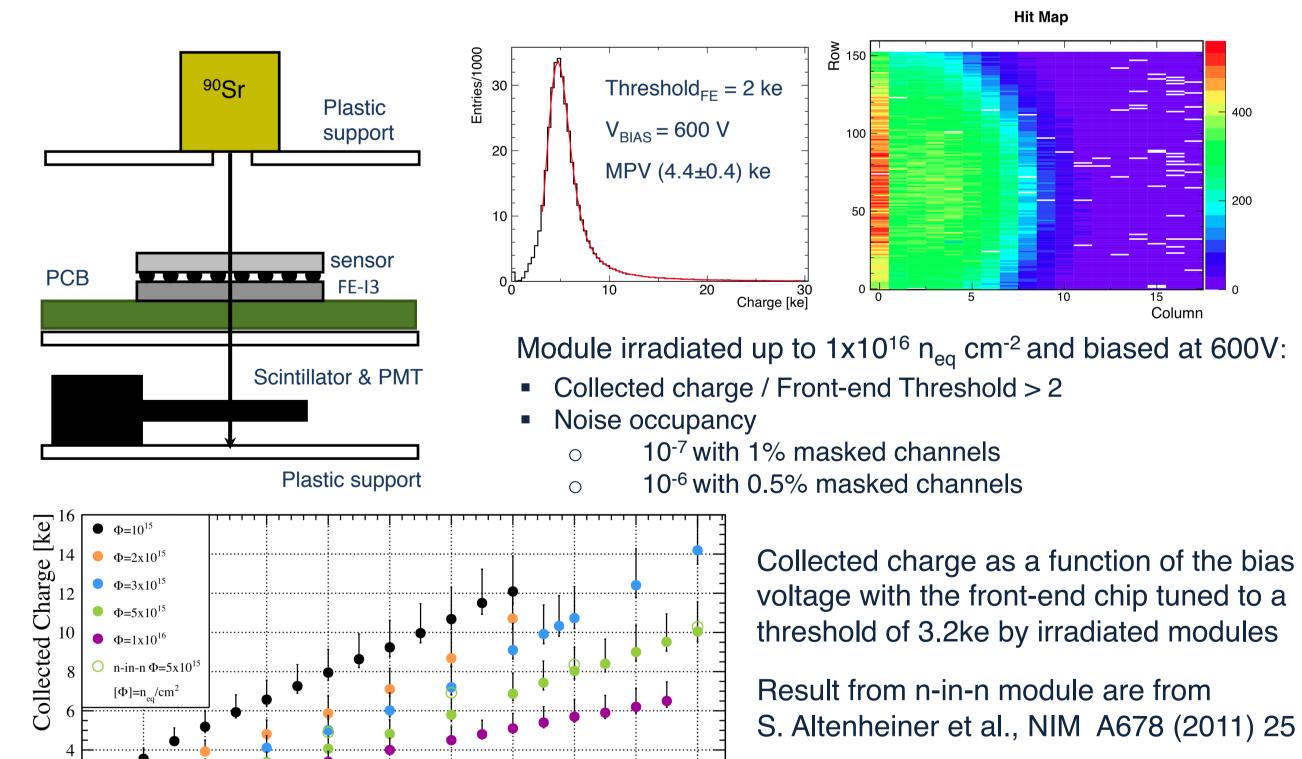

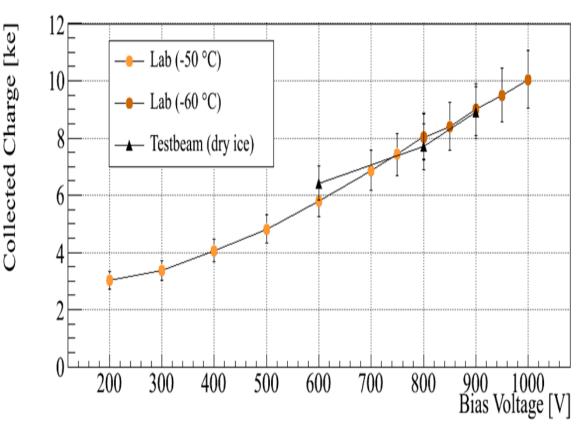

#### **External-trigger operation with <sup>90</sup>Sr source**

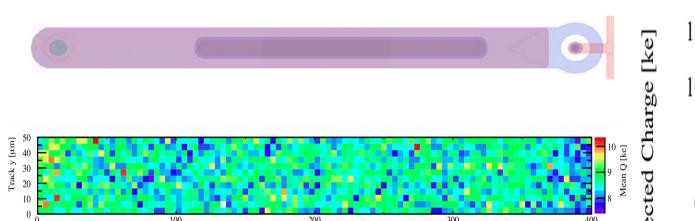

#### Charge collection

Mean collected charge as a function of the track impact point for a module irradiated up to  $5 \times 10^{15} n_{eq} \text{ cm}^{-2}$  and biased at 600 V.

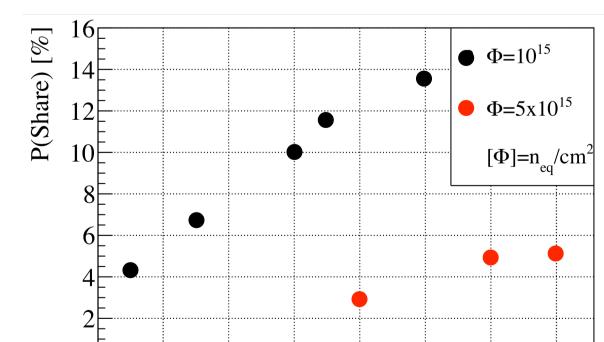

#### Charge sharing

Dependence of charge sharing P(Share) probability as a function of the bias voltage for modules irradiated up to 10<sup>15</sup> n<sub>eq</sub> cm<sup>-2</sup> and 5x10<sup>15</sup> n<sub>eq</sub> cm<sup>-2</sup>

#### At 600 V:

Overall efficiency : 98.6% Loss mostly around bias dot Efficiency of 99.8% for rest of pixel

## Summary and future plans

### References

- Excellent performance of CiS n-in-p modules irradiated up to 10<sup>16</sup> 1-MeV n<sub>eq</sub> cm<sup>-2</sup>.

- New production on 4" FZ p-type wafer of 200um and 300um thickness compatible with ATLAS IBL front-end chip (FE-I4) processed. Source, beam tests and irradiation up to HL-LHC fluences planned.

- First production of 6" wafers on high resistivity Fz p-type material, with 4-chip and 1-chip modules is foreseen.

[1] P. Weigell et al., NIM A658 (2011) 36 [2] C. Gallrapp et al., NIM A679 (2012) 29 [3] A. Macchiolo et al., arXiv:1110.4468 [4] J. Weingarten et al., arXiv:1204.1266