## **Silicon Buried Channels for Pixel Detector Cooling**

M. Boscardin<sup>a</sup>, S. Bettarini<sup>b</sup>, F. Bosi<sup>b</sup>, P. Conci<sup>a</sup>, M. Crivellari<sup>a</sup>, S. Ronchin<sup>a</sup> <sup>a</sup> FBK, Trento - Italy, <sup>b</sup> INFN sez. Pisa, Italy

## Introduction

In High Energy Physics experiments pixel detectors require a cooling system with a high heat-exchange efficiency in order to evacuate the power dissipated in the active region by the front-end electronics.

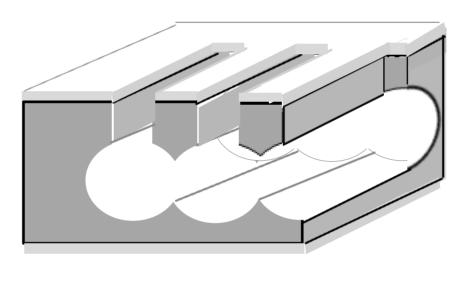

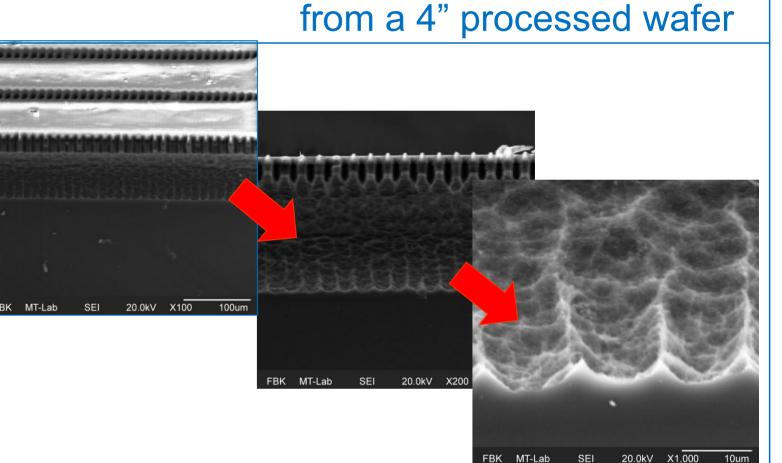

To minimize the material budget, the innovative idea is to integrate into the silicon itself a cooling system, based on microchannels made by DRIE technology. The embedded microchannels feature a peculiar geometry: in the final step a thin oxide layer is deposited to seal the channels, resulting reliable under the operating high-pressure conditions.

This technique permits the integration of the cooling system within the detector with obvious advantages on the optimization of thermal bridges and transparency to the incident particles.

| Technology |                                |                                                                                                                    |  |

|------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------|--|

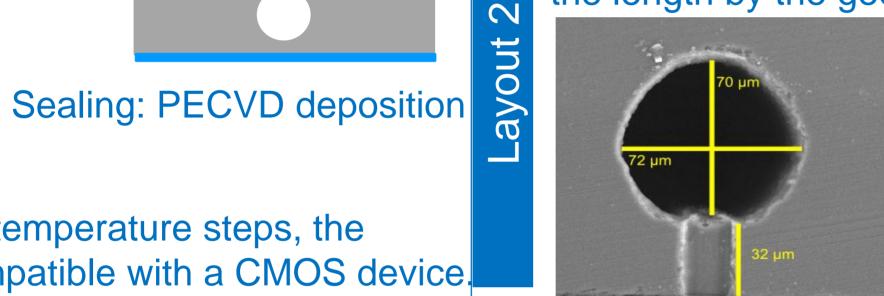

|            |                                | Channels made with individual holes:<br>The section is determined by the DRIE process,<br>the length by the layout |  |

|            | Define & etch SiO <sub>2</sub> |                                                                                                                    |  |

|            | DRIE anisotropic process       | 51 µm                                                                                                              |  |

22 µ

Channels realized as a sum of individual holes: The section is determined by the process and by layout, the length by the geometry

DRIE isotropic process

Avoiding high temperature steps, the

process is compatible with a CMOS device.

Process flow

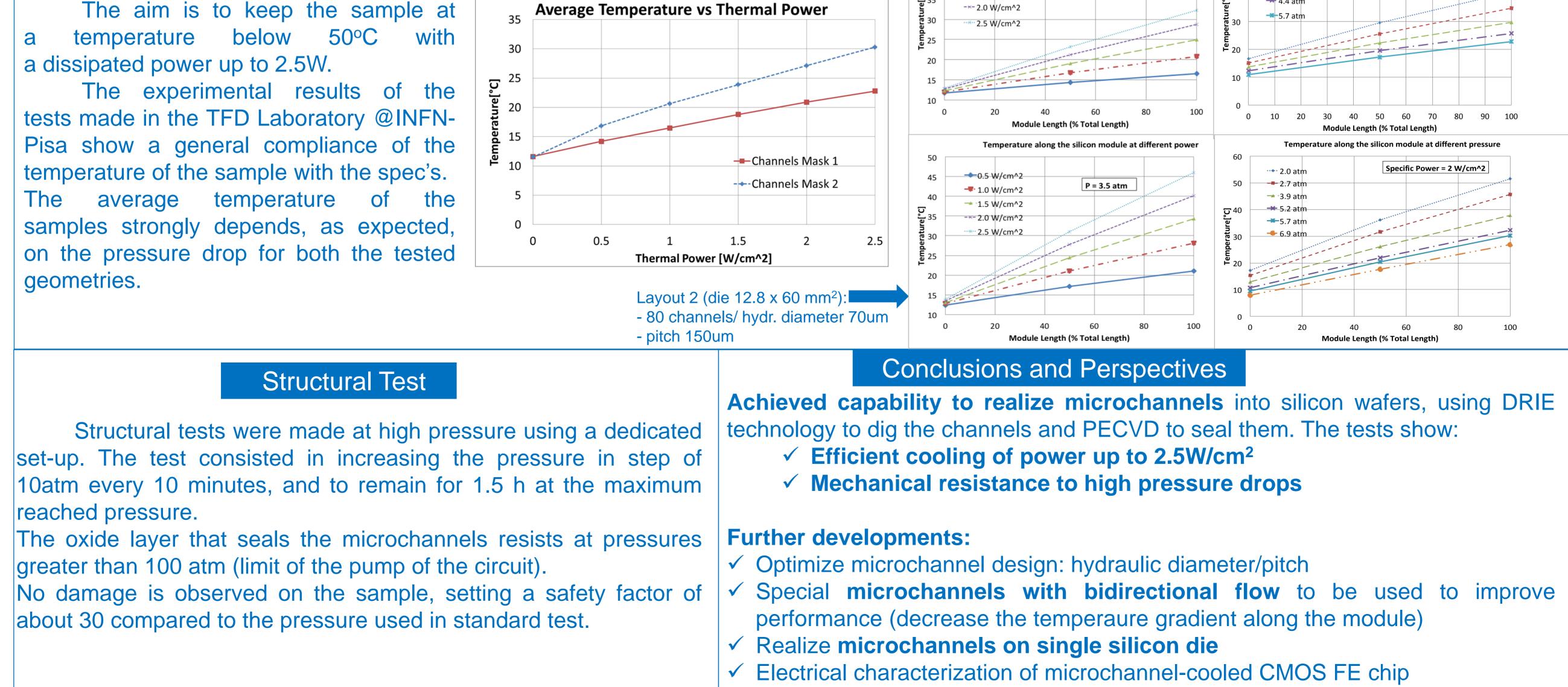

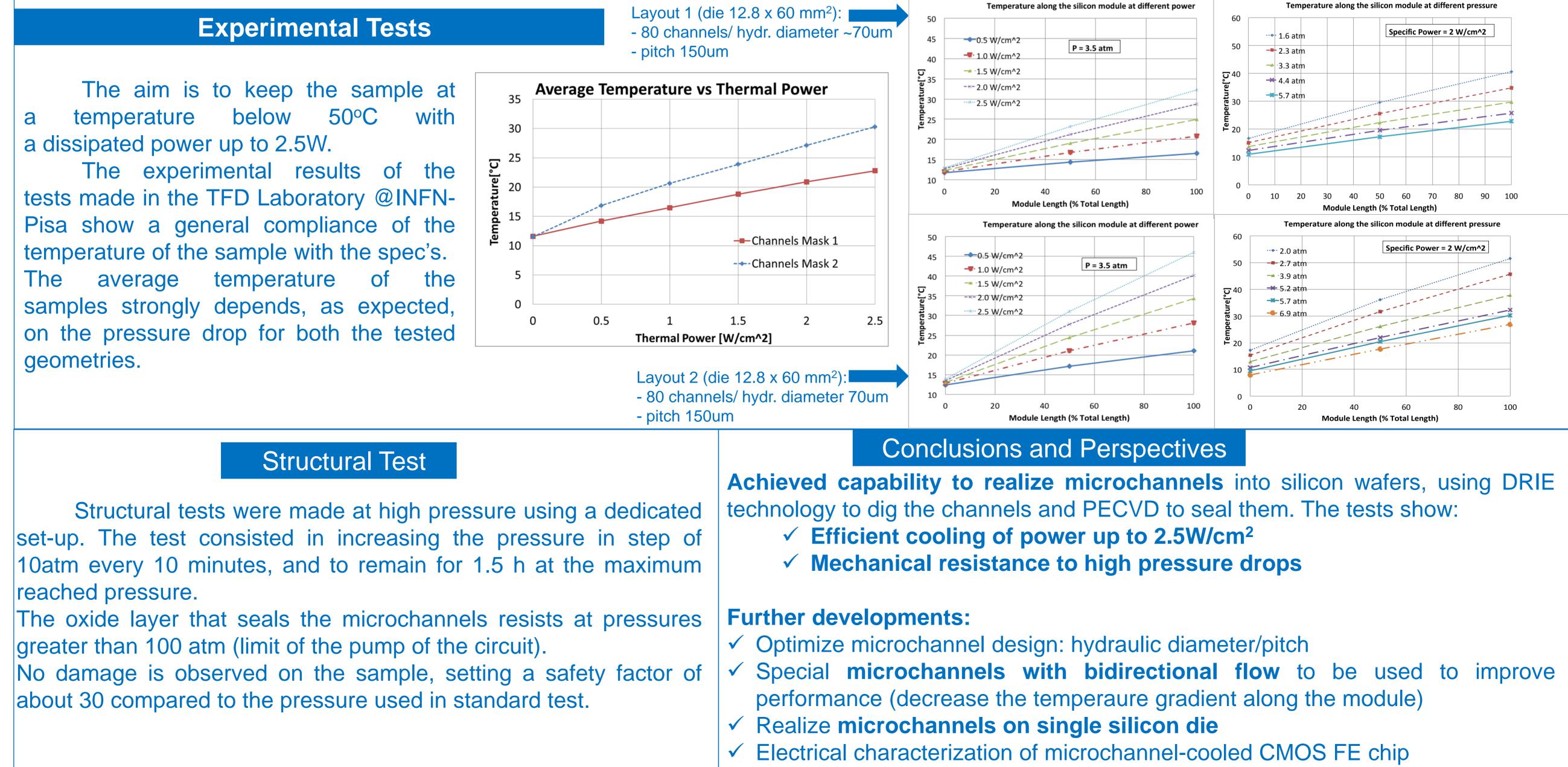

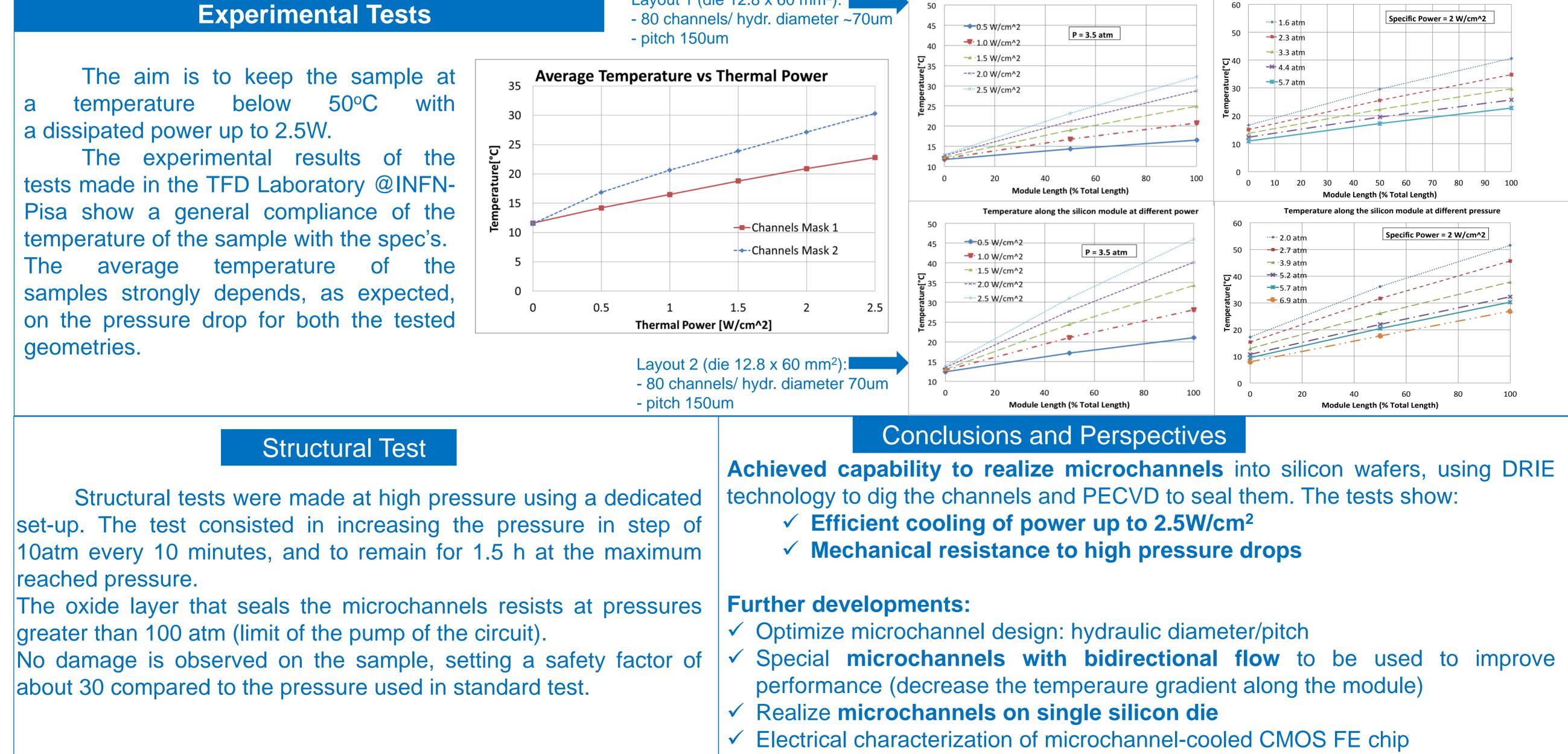

In the test-stand we used kapton/copper heather on one side of the sample and N.3 temperature probes on the opposite side. Coolant: water-glycol mix. 50% @ 10° C at the inlet.

Microchannel silicon prototype test set-up

Silicon samples obtained

temperature below 50°C with a

The experimental results

12<sup>th</sup> Pisa Meeting on Advanced Detectors, May 2012 - La Biodola, Isola d'Elba (Italy)