#### **Paul Scherrer Institute** Stefan Ritt

**Gigahertz Waveform Sampling: An Overview and Outlook**

4 channels 5 GSPS 1 GHz BW 8 bit (6-7) 15k€

4 channels 5 GSPS 1 GHz BW 11.5 bits 900€ USB Power

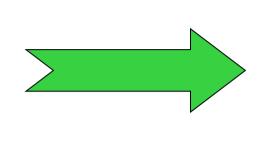

## Can it be done with FADCs?

• Overview of Chips and Applications

• Future Design Directions

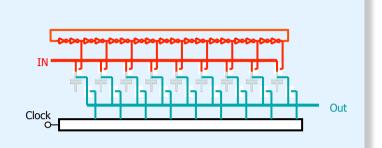

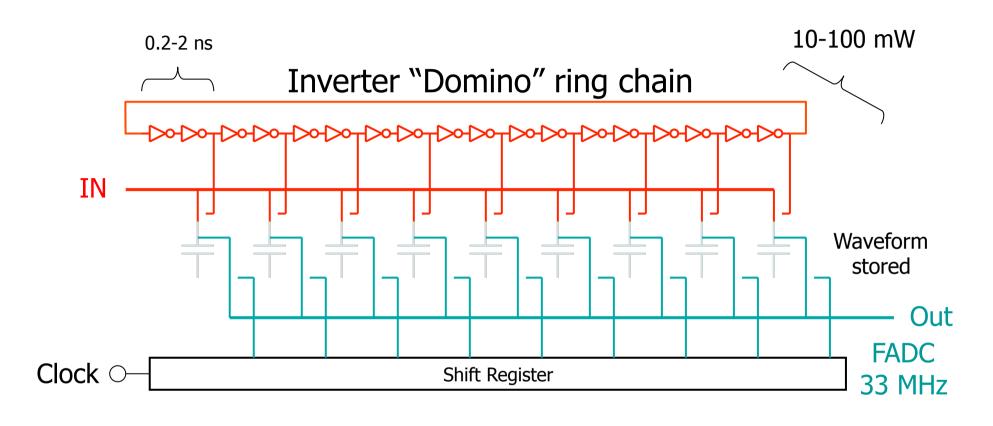

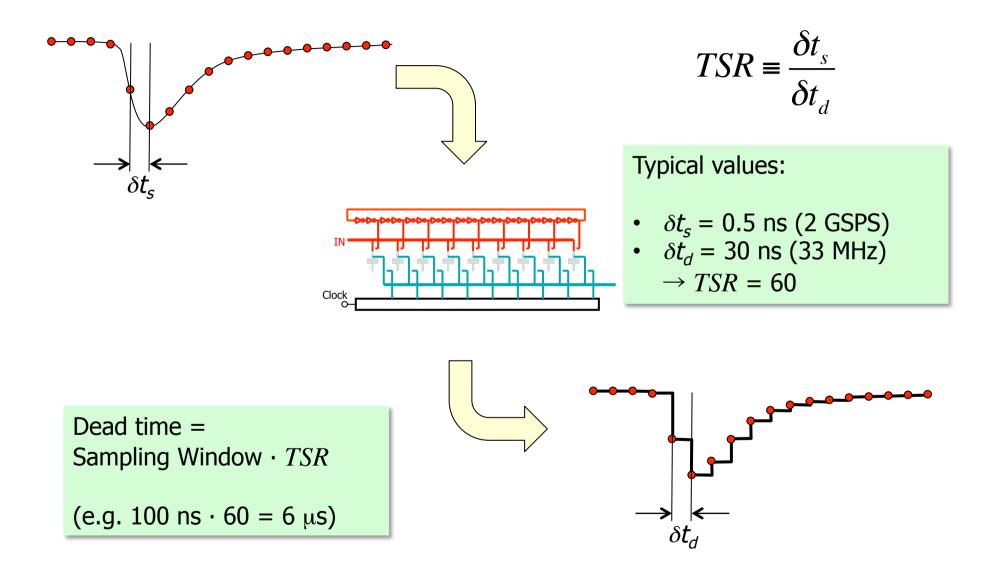

#### "Time stretcher" $GHz \rightarrow MHz$

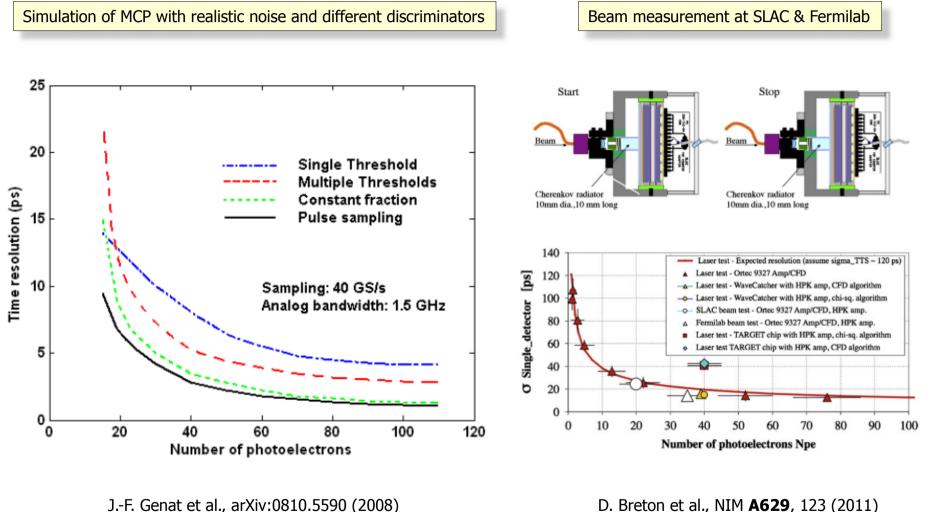

D. Breton et al., NIM A629, 123 (2011)

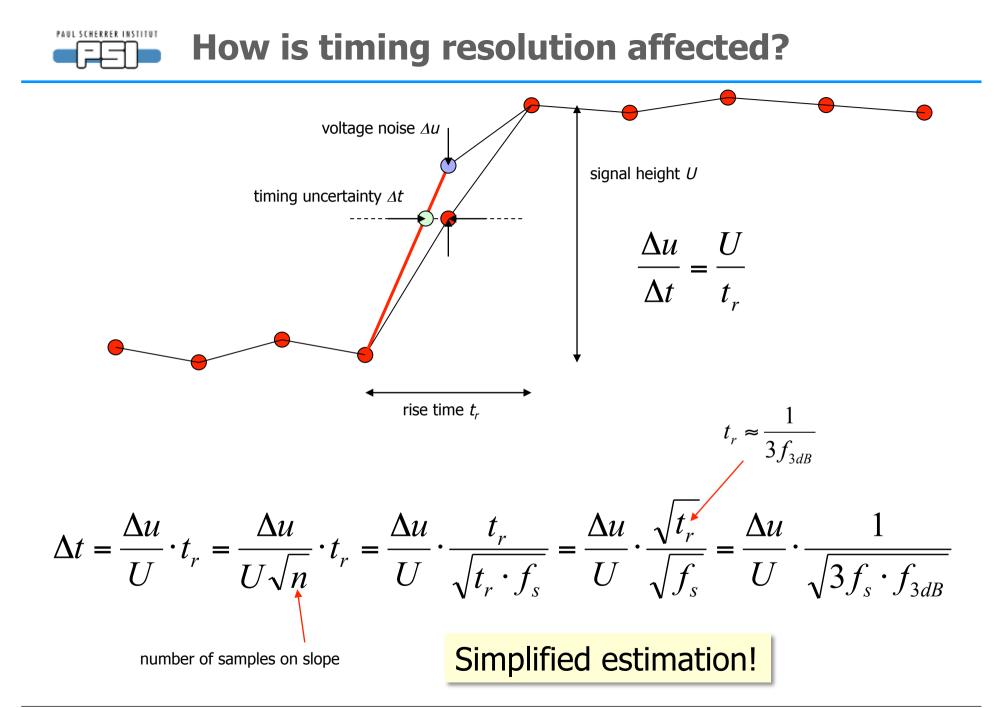

|                  | $\Delta t = \frac{\Delta u}{U} \cdot \frac{1}{\sqrt{3f_s \cdot f_{3dB}}}$ |            |         | Assumes zero<br>aperture jitter |        |

|------------------|---------------------------------------------------------------------------|------------|---------|---------------------------------|--------|

|                  | U                                                                         | $\Delta u$ | $f_s$   | f <sub>3db</sub>                | Δt     |

| today:           | 100 mV                                                                    | 1 mV       | 2 GSPS  | 300 MHz                         | ~10 ps |

| optimized SNR:   | 1 V                                                                       | 1 mV       | 2 GSPS  | 300 MHz                         | 1 ps   |

| next generation: | 1V                                                                        | 1 mV       | 10 GSPS | 3 GHz                           | 0.1 ps |

includes detector noise in the frequency region of the rise time and aperture jitter

$\sim\sim\sim\sim$

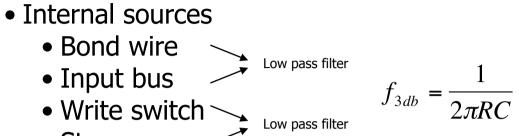

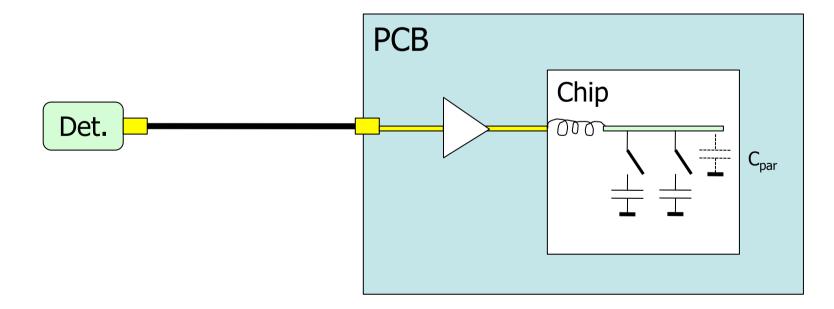

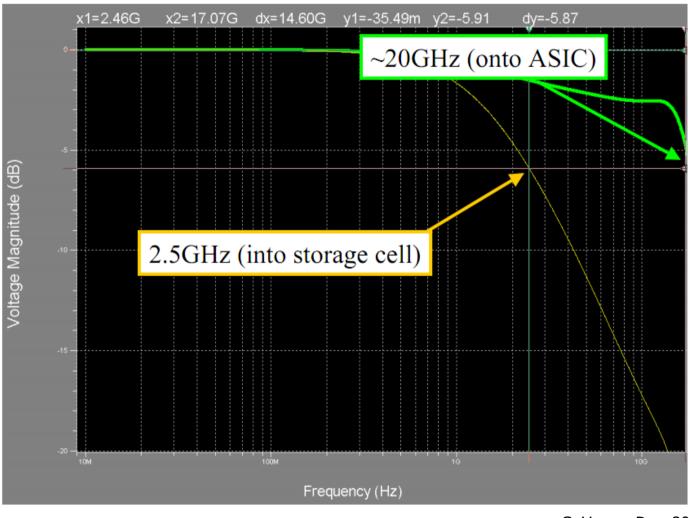

## Limits on analog bandwidth

- External sources

- Detector

- Cable

- Connectors

- PCB

- Preamplifier

• Storage cap //

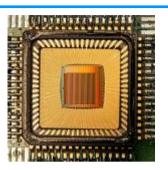

# Bump-bonding (optimized) input coupling

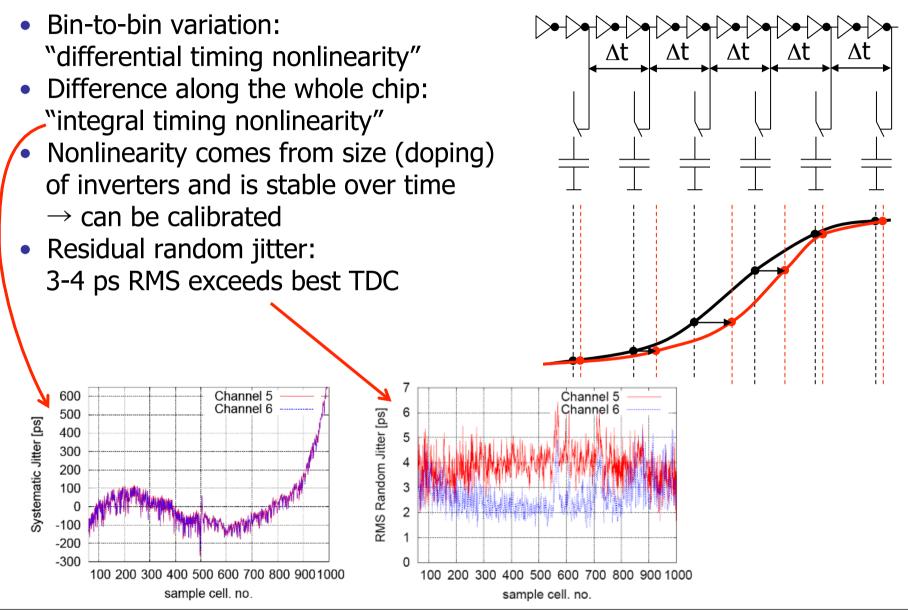

## **Timing Nonlinearity**

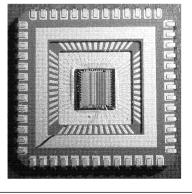

- CMOS process (typically 0.35 ... 0.13  $\mu$ m)  $\rightarrow$  sampling speed

- Number of channels, sampling depth, differential input

- PLL for frequency stabilization

- Input buffer or passive input

- Analog output or (Wilkinson) ADC

- Internal trigger

- Exact design of sampling cell

#### **Switched Capacitor Arrays for Particle Physics**

## **Some specialities**

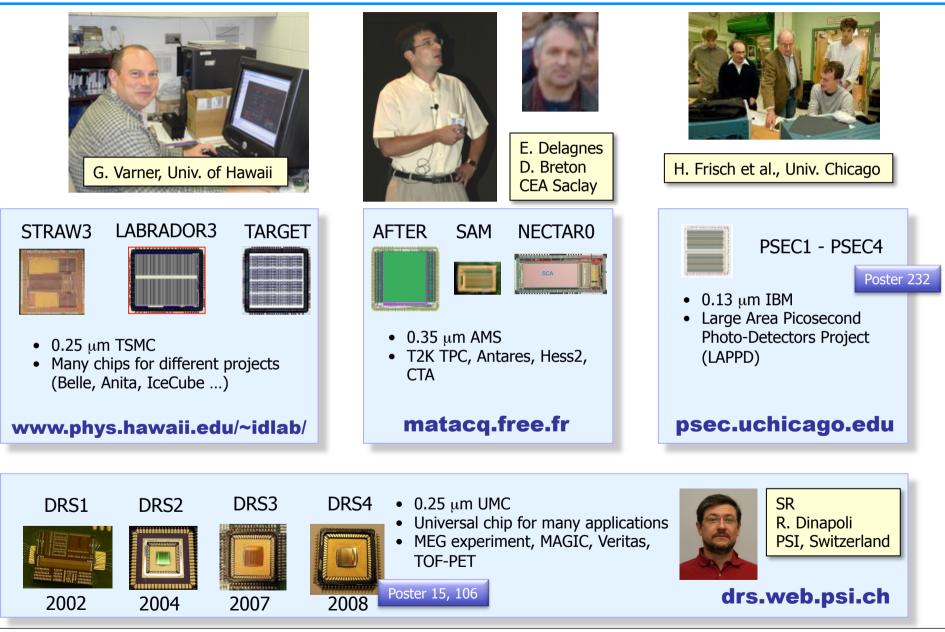

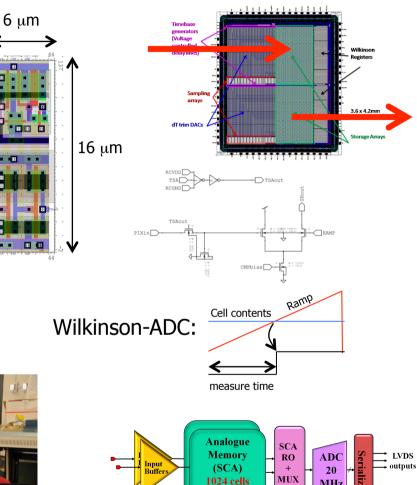

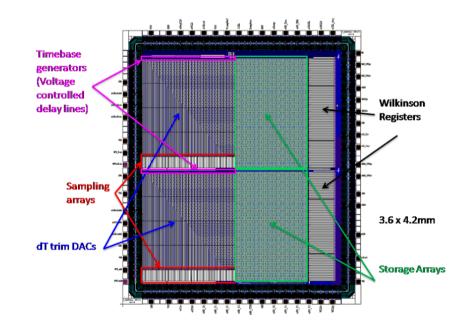

- LAB Chip Family (G. Varner)

- Deep buffer (BLAB Chip: 64k)

- Double buffer readout (LAB4)

- Wilkinson ADC

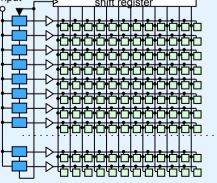

- NECTAR0 Chip (E. Delagnes)

- Matrix layout (short inverter chain)

- Input buffer (300-400 MHz)

- Large storage cell (>12 bit SNR)

- 20 MHz pipeline ADC on chip

- PSEC4 Chip (E. Oberla, H. Grabas)

- 15 GSPS •

- 1.6 GHz BW • @ 256 cells

- Wilkinson ADC

1-3.2GS/s

SCA Sequencer &

pointer manager

<u>\_</u>

Slow

Control

SPI-like

MHz

CK

generator

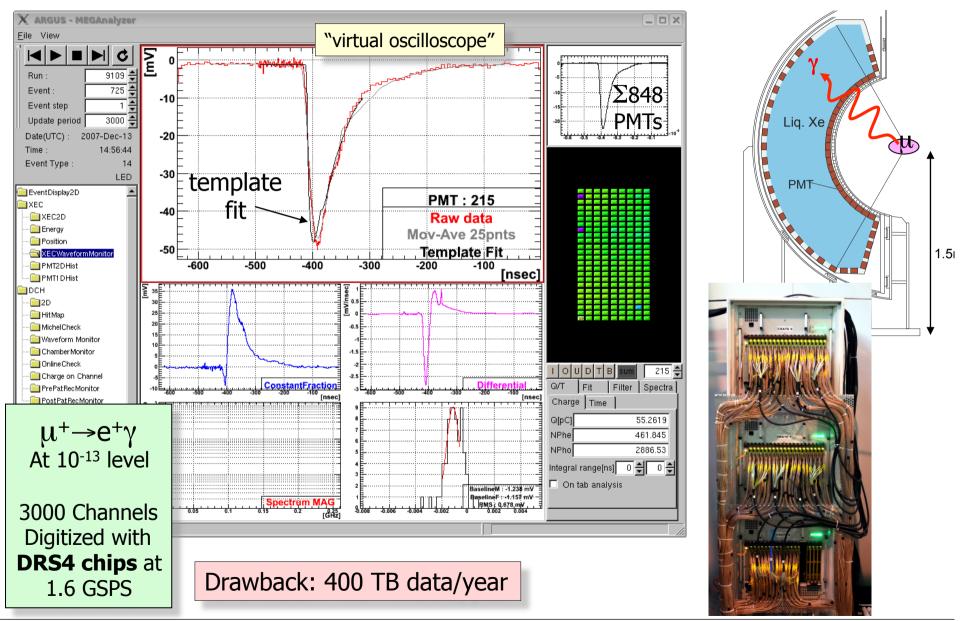

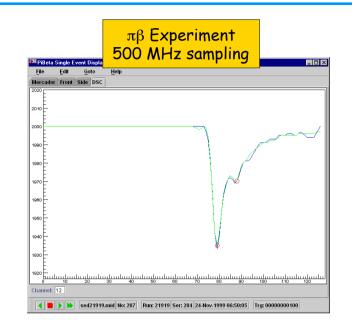

## **MEG On-line waveform display**

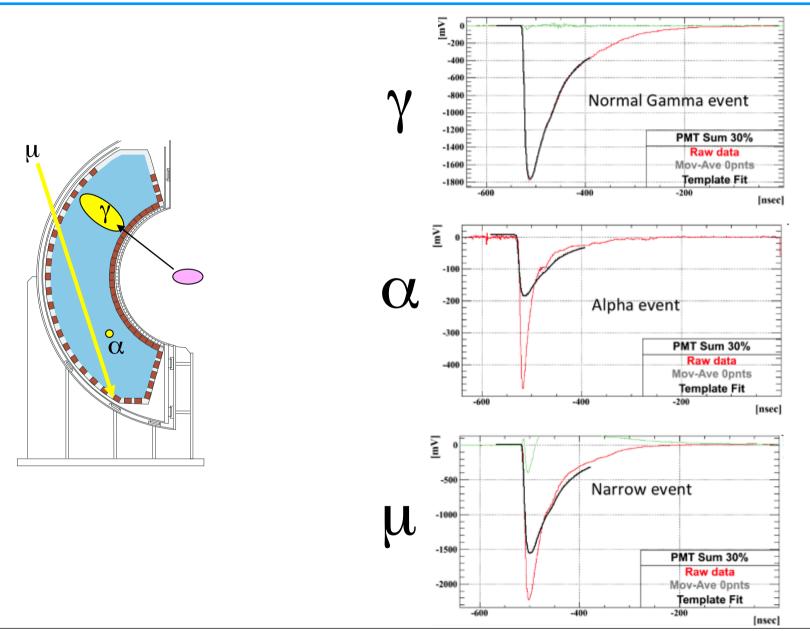

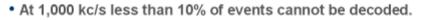

#### **Pulse shape discrimination**

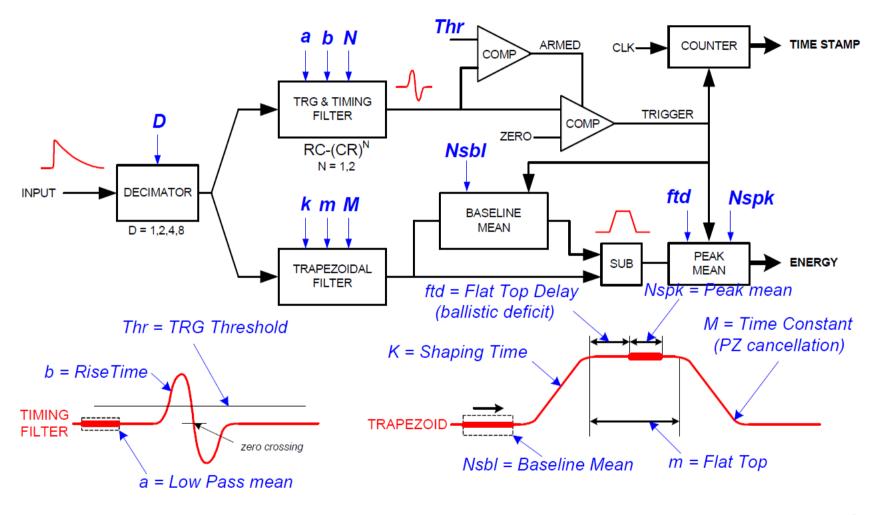

C. Tintori (CAEN) V. Jordanov *et al.*, NIM **A353**, 261 (1994)

#### **Template Fit**

- Determine "standard" PMT pulse by averaging over many events → "Template"

- Find hit in waveform

- Shift ("TDC") and scale ("ADC") template to hit

- Minimize  $\chi^2$

- Compare fit with waveform

- Repeat if above threshold

- Store ADC & TDC values

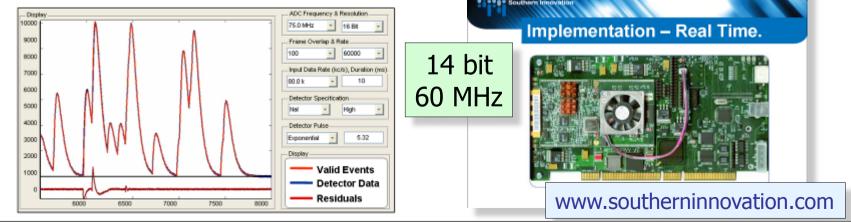

#### **Other Applications**

## Things you can buy

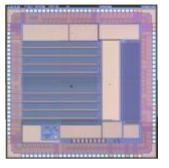

- DRS4 chip (PSI)

- 32+2 channels

- 12 bit 5 GSPS

- > 500 MHz analog BW

- 1024 sample points/chn.

- 110  $\mu s$  dead time

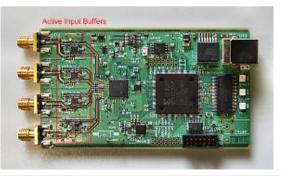

- DRS4 Evaluation Board

- 4 channels

- 12 bit 5 GSPS

- 750 MHz analog BW

- 1024 sample points/chn.

- 500 events/sec over USB 2.0

- MATACQ chip (CEA/IN2P3)

- 4 channels

- 14 bit 2 GSPS

- 300 MHz analog BW

- 2520 sample points/chn.

- 650 µs dead time

- SAM Chip (CEA/IN2PD)

- 2 channels

- 12 bit 3.2 GSPS

- 300 MHz analog BW

- 256 sample points/chn.

- On-board spectroscopy

• Future Design Directions

## How to fix timing nonlinearity?

- LAB4 Chip (G. Varner) uses "Trim bits" to equalize inverter delays to < 10 ps</li>

- Dual-buffer readout for decreased dead time

- Wilkinson ADCs on chip

| TABLE IPERFORMANCE SPECIFICATIONS FOR THE LAB4 ASIC. |                                       |  |  |  |

|------------------------------------------------------|---------------------------------------|--|--|--|

| Specification                                        | Parameter                             |  |  |  |

| 4096                                                 | samples/channel                       |  |  |  |

| 1                                                    | channel/ASIC                          |  |  |  |

| $\leq 10$                                            | ps residual timebase error            |  |  |  |

| $\sim 10$                                            | bits resolution (12-bits ADC)         |  |  |  |

| 256                                                  | samples convert window ( $\sim$ 64ns) |  |  |  |

| 4                                                    | GSa/s sampling                        |  |  |  |

| $\leq 100$                                           | $\mu$ s to read all samples           |  |  |  |

| $\geq 1k$                                            | Hz sustained readout (multibuffer)    |  |  |  |

First tests will be reported on RT12 conference June 11-15, Berkeley, CA

Short sampling depth

Deep sampling depth

- Low parasitic in capacitance

Wide input bus

Induction to combine best of both worlds?

Wide input bus

- Low R<sub>on</sub> write switches

- $\rightarrow$  High bandwidth

Faster sampling speed for a given trigger latency

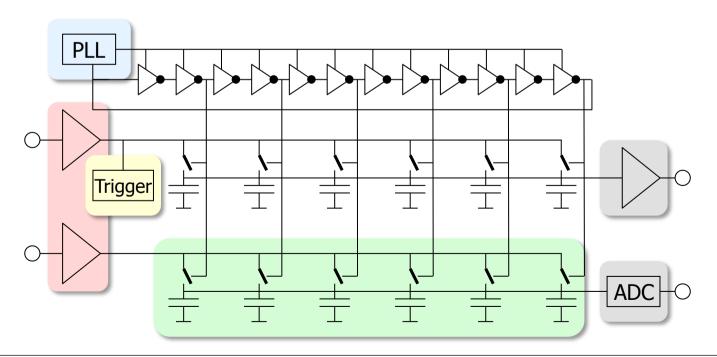

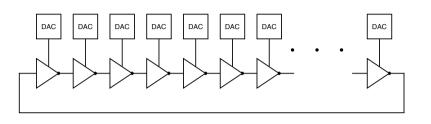

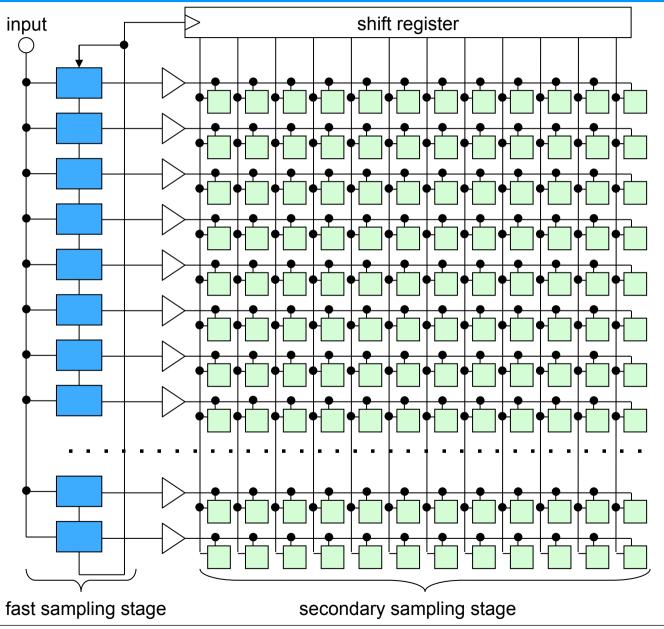

## **Cascaded Switched Capacitor Arrays**

- 32 fast sampling cells (10 GSPS)

- 100 ps sample time,

3.1 ns hold time

- Hold time long enough to transfer voltage to secondary sampling stage with moderately fast buffer (300 MHz)

- Shift register gets clocked by inverter chain from fast sampling stage

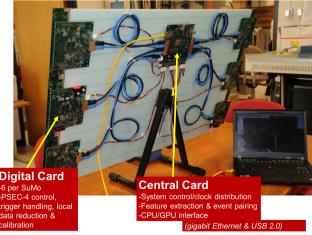

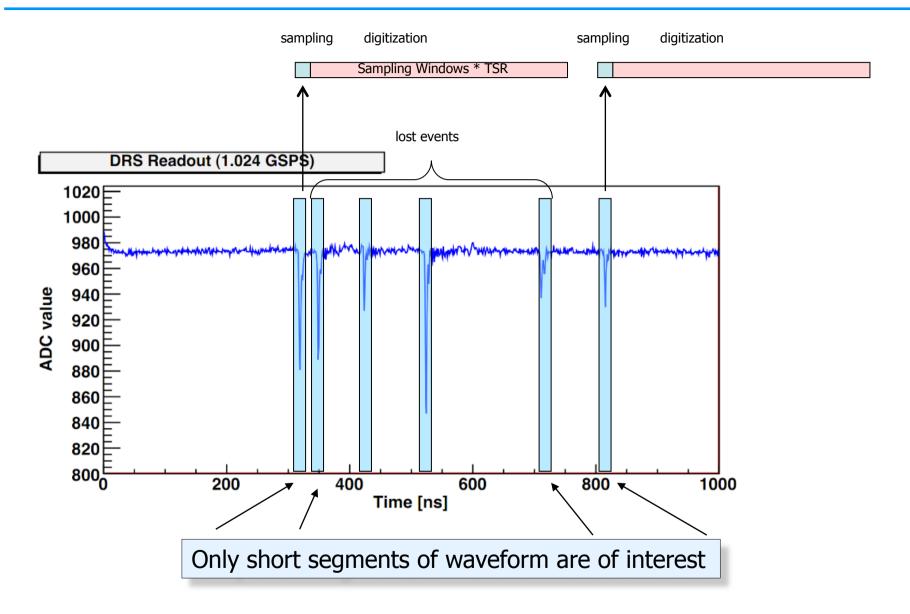

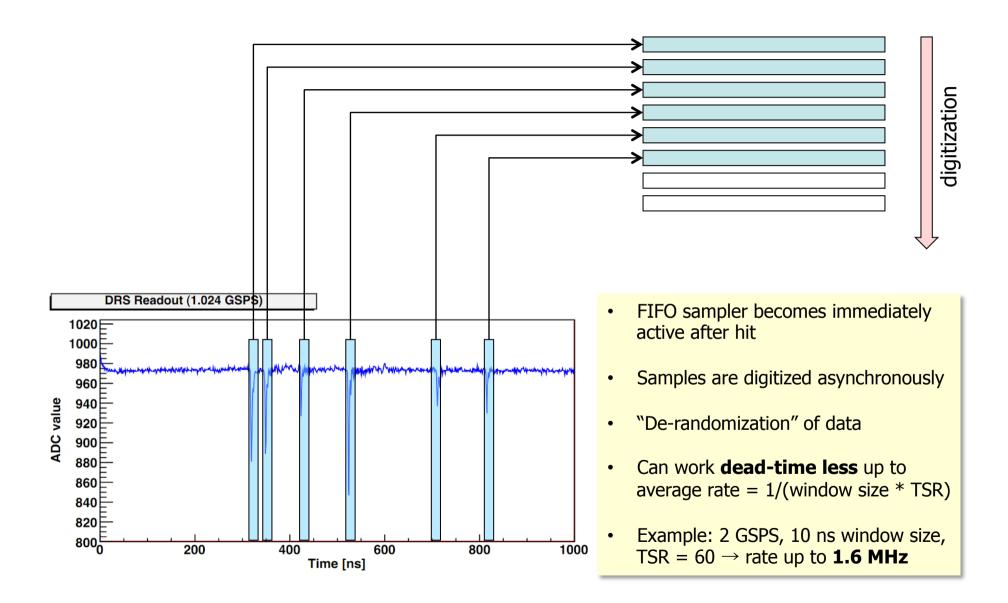

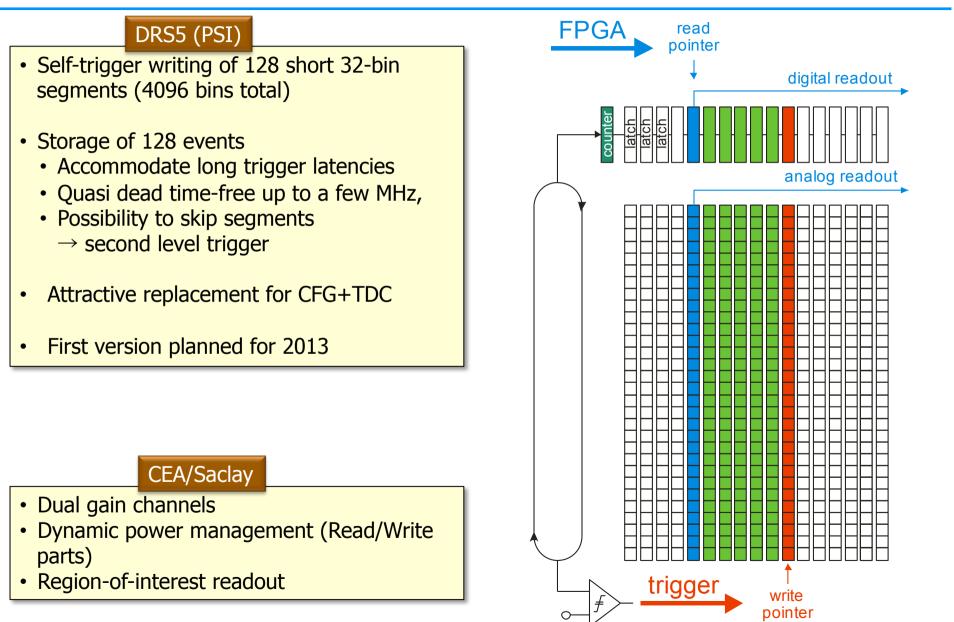

#### The dead-time problem

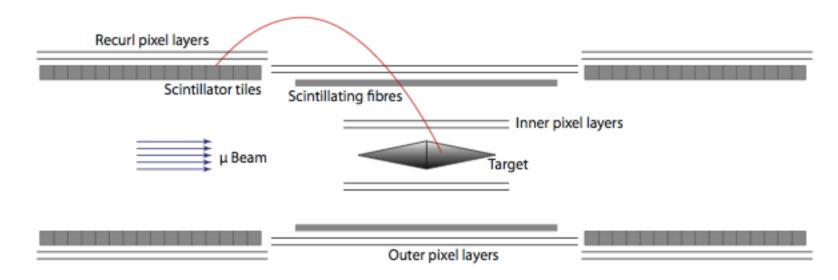

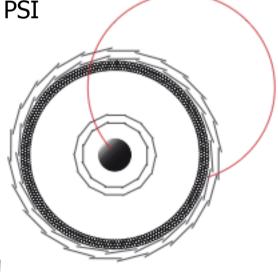

- Mu3e experiment planned at PSI with a sensitivity of 10<sup>-16</sup>

- $2*10^9 \ \mu$  stops/sec

- Scintillating fibres & tiles

- 100ps timing resolution

- 2-3 MHz hit rate

- Can only be done with DRS5!

## Conclusions

- SCA technology offers tremendous opportunities

- Several chips and boards are on the market for evaluation

- New series of chips on the horizon might change frontend electronics significantly

**Profit from the true magician!**