#### www.caen.it

Matteo M. Angarano m.angarano@caen.it

Pisa, DREB 2012 March 2012

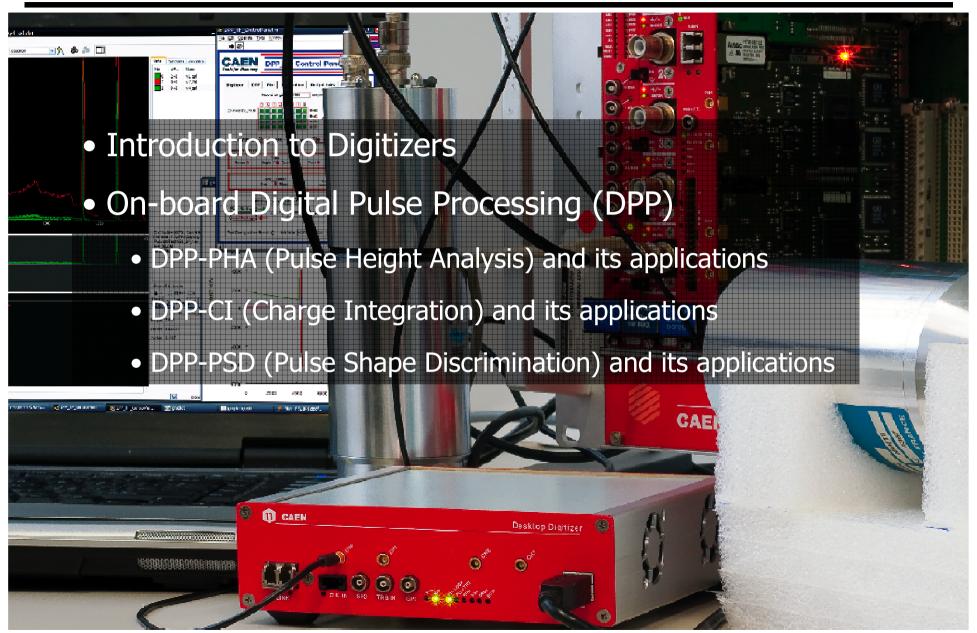

### Outline

Reproduction, transfer, distribution of part or all of the contents in this document in any form without prior written permission of CAEN S.p.A. is prohibited

### Introduction

- In recent years, CAEN developed a complete family of digitizers

- Beside the use of the digitizers as waveform recorders ("oscilloscope mode"), CAEN offers the possibility to upload special firmware that implement several algorithms for Digital Pulse Processing (DPP)

- Digitizers running DPP firmware represent a complete digital replacement of most traditional acquisition chains

- From 2 to 64 channels

- Up to 5 GS/s sampling rate Up to 14 bit

- FPGA firmware for Digital Pulse Processing

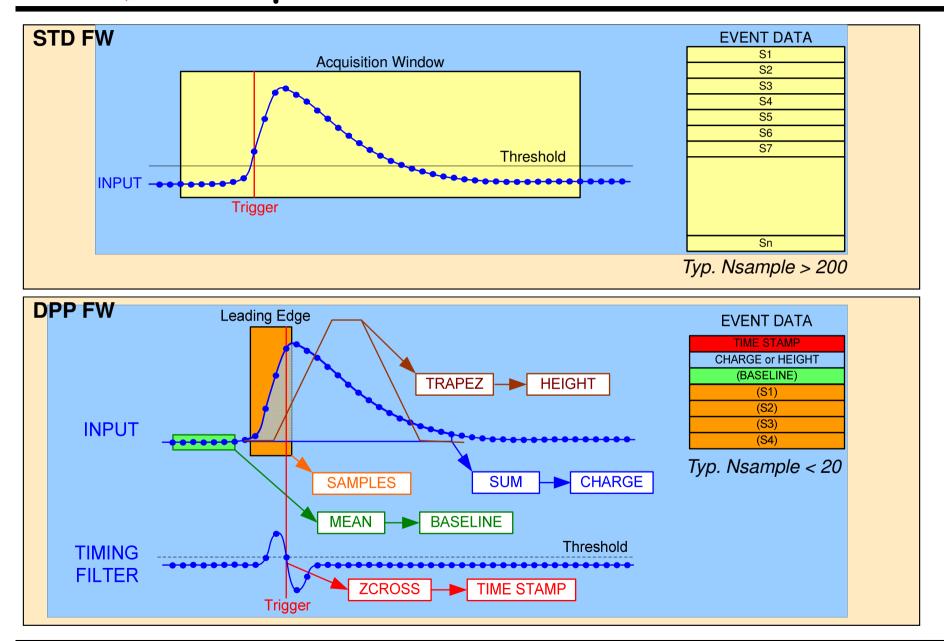

## Acquisition mode: raw waveform vs DPP

### Raw waveform mode: Limits

- Using digitizers as waveform recorders can produce a large amount of data to be transferred from the acquisition board to a mass storage device

- The data throughput can be extremely high: it may be no possible to transfer raw data to computers and make the analysis off-line!

- On-line Digital Pulse Processing is needed to extract only the information of interest reducing the data throughput

- The aim of the DPP is to provide FPGA algorithms able to make in digital the same functions of analog modules such as Shaping Amplifiers, Discriminators, QDCs, Peak Sensing ADCs, TDCs, Scalers, Coincidence Units, etc.

- Three main DPP firmware have been developed so far:

DPP-PHA (Pulse Height Analysis)

DPP-CI (Charge Integration)

DPP-PSD (Pulse Shape Discrimination)

# DPP-PHA PULSE HEIGHT ANALYSIS

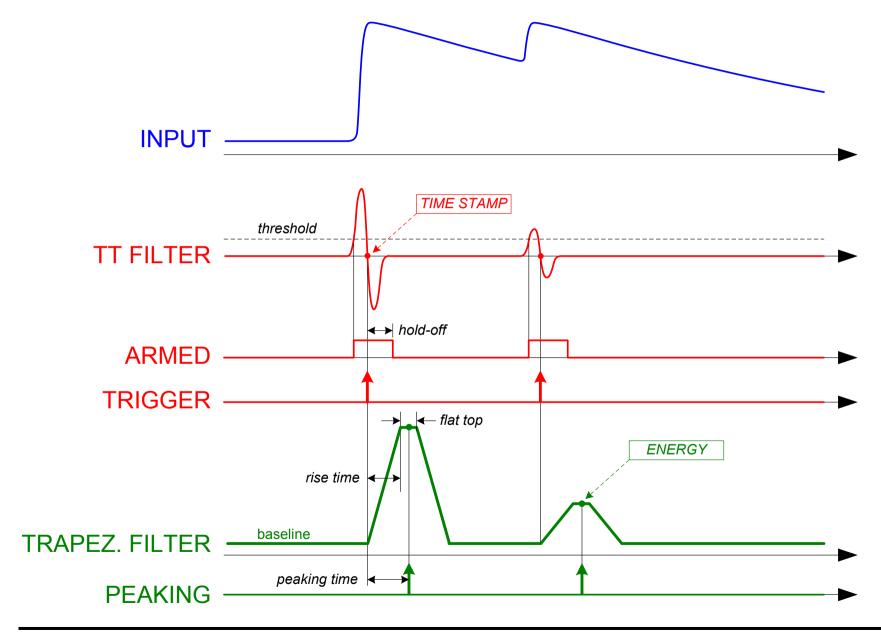

- Digital implementation of the Shaping Amplifier + Peak Sensing ADC (Multi-Channel Analyzer)

- Charge Sensitive Preamplifier directly connected to the digitizer

- Implemented in the 14 bit, 100MS/s digitizers (mod. 724)

- Provides pulse height, time stamp (10ns) and optionally raw data

- Pile-up rejection, Baseline restoration, Ballistic Deficit correction

- Low dead time => high counting rate (up to 1Mcps)

- Best suited for high resolution spectroscopy (HPGe and Si detectors)

- Also suitable for homeland security and biomedical applications

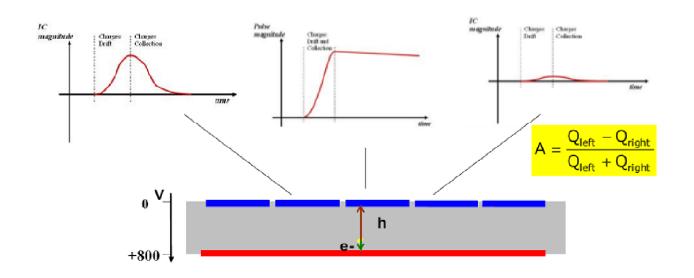

- Can work with segmented detectors (synchronizations, coincidences and neighbour triggering)

### Dead Time in the DPP-PHA

- Unlike the analog chain, in the DPP-PHA there is no conversion time

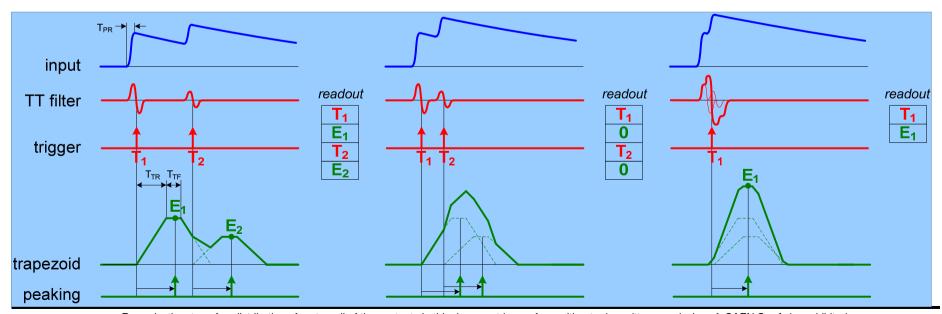

- The A/D conversion and the pulse processing is always alive; dead time in the energy filter is only given by the inability to calculate the enery due to trapezoid overlap ( $\Delta T < Trise + Tflat$ )

- Although pile-up causes the loss of energy values, the timestamps is given for almost all pulses: therefore, the true rate can be calculated

- DeadTime = RealTime \* (1 Energy Count / Time-Stamp Count)

- Double pulse resolution ≈ Rise Time (two pulses separated by at least the pulse rise time can be distinguished)

Reproduction, transfer, distribution of part or all of the contents in this document in any form without prior written permission of CAEN S.p.A. is prohibited

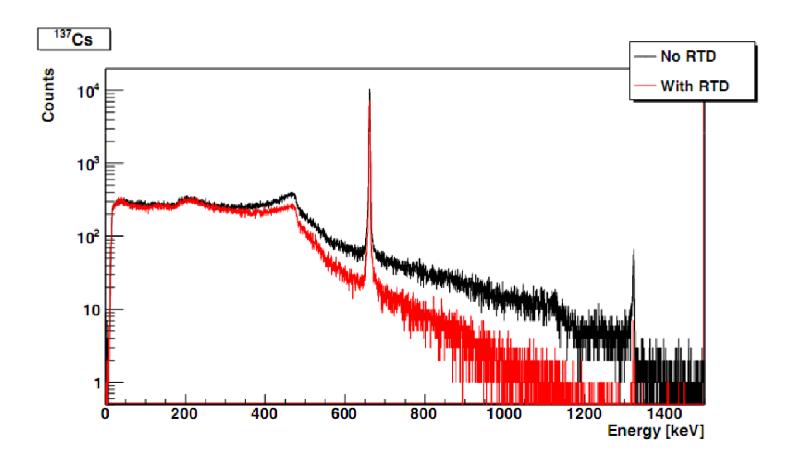

# Enhanced Pile-up rejection

- The Rise Time Discriminator allows double pulses piling up on the rising edge to be detected and counted twice (the relevant energies are discarded)

- Residual multiple pulses that cannot be distinguished (despite the RTD) can be counted on a statistical basis

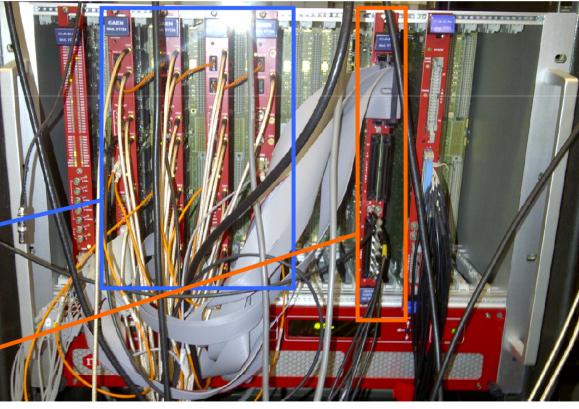

# Individual inter-channel triggering (I)

- Feature developed for the project *ProSPECTus* (Compton camera)

- Mainly needed in segmented or clove detectors

- One channel triggers itself and also neighbour channels (also from board to board)

- Individual TRG-IN and TRG-OUT lines from each channel to the Front Panel GPIO connector (8 inputs + 8 outputs)

- External trigger unit (V1495) for the coincidence matrix implementation

# Individual inter-channel triggering (II)

Segmented HPGe

V1724 digitizers with DPP-PHA

V1495 with ad hoc Trigger Logic