SuperB XVII Workshop + Kick Off Meeting La Biodola, May 2011

# CMOS pixel sensors developments in Strasbourg

#### Outline

- sensor performances assessment

- state of the art: MIMOSA-26 and its applications

- Strasbourg work plan: 0.18 μm and 3D

- sensor integration: PLUME

- tracking and alignment: AIDA

- detector geometry optimisation studies

- conclusion

Isabelle Ripp-Baudot

for the PICSEL group @ Strasbourg

http://www.iphc.cnrs.fr/-PICSEL-.html

IPHC - CNRS/IN2P3 and Université de Strasbourg

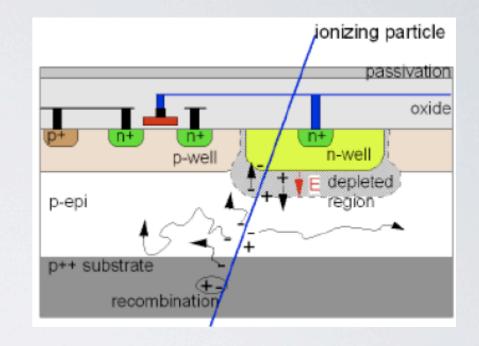

#### **CMOS** pixel sensors for vertex detectors

- Prominent advantages:

- granularity: pixels of  $\sim 10 \times 10 \mu m^2$

- → excellent spatial resolution

- monolithic: signal processing within the sensor

- → easier to integrate

- material budget: total thickness < 50 μm

- and also: room T° operation, manufacturing, cost, power consumption, ...

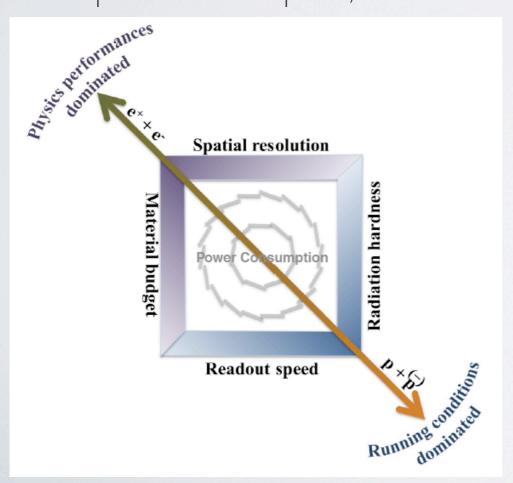

→ CMOS pixel sensors appear as an optimal solution for the next generation of vertex detectors, but developments are needed to optimise them according to different requirements.

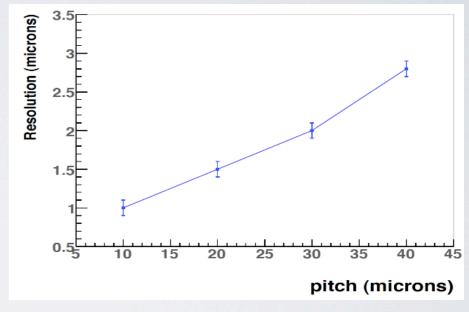

#### sensor performances assessment

#### MIMOSA sensor prototypes:

see: http://www.iphc.cnrs.fr/List-of-MIMOSA-chips.html

- various technologies:

- 2 different 0.35 µm processes

- 2 different 0.18 µm processes

- various pitches:

- $10 \times 10 \ \mu m^2 \rightarrow 40 \times 40 \ \mu m^2$ ,

- elongated pixels 16x64 μm<sup>2</sup>, 18.4x(36.8 to 73.6) μm<sup>2</sup>.

- various sensitive volumes:

- w/ and w/o epitaxial layer → various thicknesses and dopings,

- standard and high resistivities.

- $\rightarrow$  more than 10 years of **exhaustive studies** (S/N,  $\varepsilon$ ,  $\sigma_{s.p.}$ , clustering, charge sharing) under different operating conditions (T°, irradiation, read-out frequency) and **systematic beam test validations**.

- → useful data base of the charge collected per pixel for each technology & architecture.

#### MIMOSA sensors: state of the art

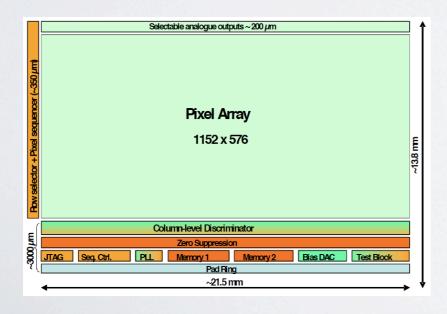

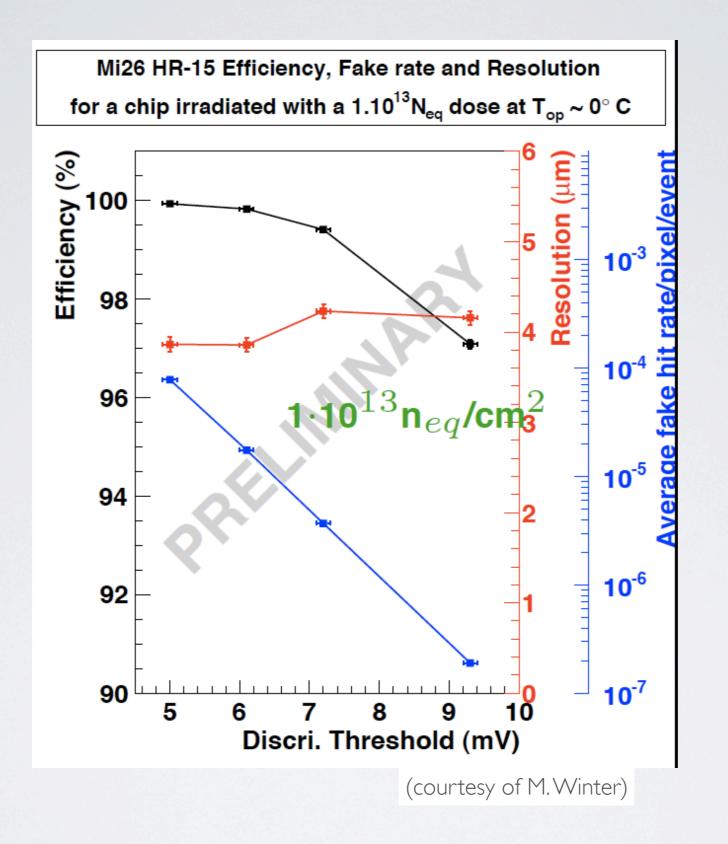

#### MIMOSA-26 prototype:

- 0.35 µm process with high resistivity epitaxy

- fabricated 2008-2010: > 90 sensors tested with different features

- active area 1152 columns of 576 pixels  $(21.2 \times 10.6 \text{ mm}^2)$

- pitch 18.4x18.4  $\mu$ m<sup>2</sup>  $\rightarrow$  660k pixels with  $\sigma_{\text{s.p.}}$ = 3.5  $\mu$ m

- detection efficiency ~ 100 % for very low fake rate (~10-4)

- in-pixel amplification and CDS

- end-of-column discrimination and 0 suppression (digital output)

- rolling shutter read-out: pixels grouped in columns, readout in //

no dead-time

• read-out time:  $10^4$  frames/s  $\rightarrow$  ~  $100 \, \mu s \rightarrow$  suited for >  $10^6$  particles/cm<sup>2</sup>/s

• power dissipation: 250 mW/cm<sup>2</sup>

#### MIMOSA-26 applications

- applications of MIMOSA-26 technology in different projects and vertex detector upgrades, requiring:

- material budget 0.15 % 0.5 %

- tolerance up to several MRad and fluences  $> 10^{13} n_{eq}/cm^2$ depending on T°, pitch, read-out time.

- ~ few µs read-out time

- Beam Telescope of the FP6 project EUDET

- STAR @ RHIC→ data taking in 2013-2014,

first vertex detector equipped with CMOS sensors

- CBM @ FAIR → data taking > 2016 (SIS-100)

Hadrontherapy: FIRST (GSI)

- other applications: ALICE @ LHC, ILD vertex @ ILC, ...

- see details in previous review on Strasbourg activities by M. Winter, October 2010 SuperB meeting @ LNF http://agenda.infn.it/conferenceDisplay.py?confld=2303

#### next steps

#### exploration of 0.18 µm technologies:

- MIMOSA-32: Ist 0.18 µm prototype will be studied in 2012 (Multi Project Wafer Run #62 24/10/11)

- MIMOSA-22THR: study of pixel architecture → 2013

- MISTRAL-like: first big prototype for ALICE and CBM, with read-out time  $\sim 20$  to  $40~\mu s$

- 2 investigate all features: 3T, 4T, all metallisation layers used, ...

- 3 study of parallel rolling-shutter read-out → read-out time < 10 µs ≥ 2016

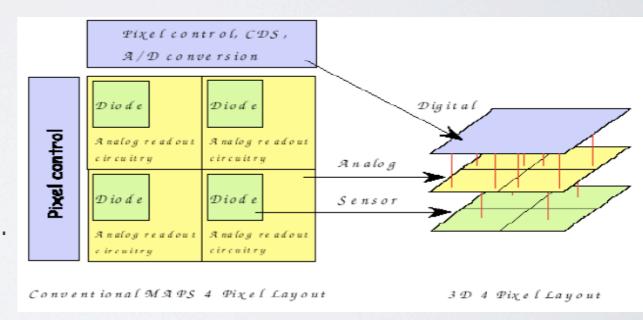

#### exploration of 3D Integration Technologies:

- participation to the 3D Integration Consortium (coordinated by FNAL): CAIRN chips (CMOS Active pixel sensors with vertically Integrated Read-out and Networking functionalities) submitted to foundry in Spring 2009.

- high expectations

- longer term program

→ Strasbourg: improve performance of the charge collection (S/N, noise reduction) and the pre-amplification.

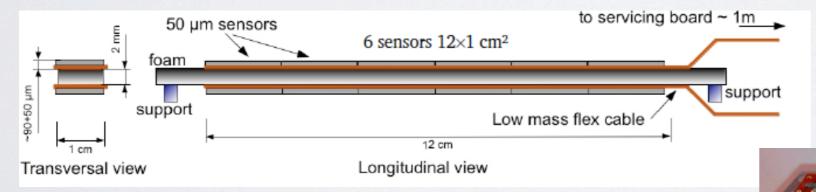

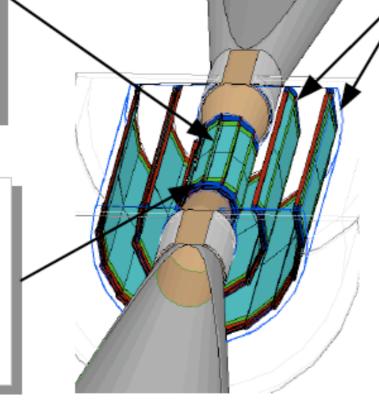

#### sensor integration

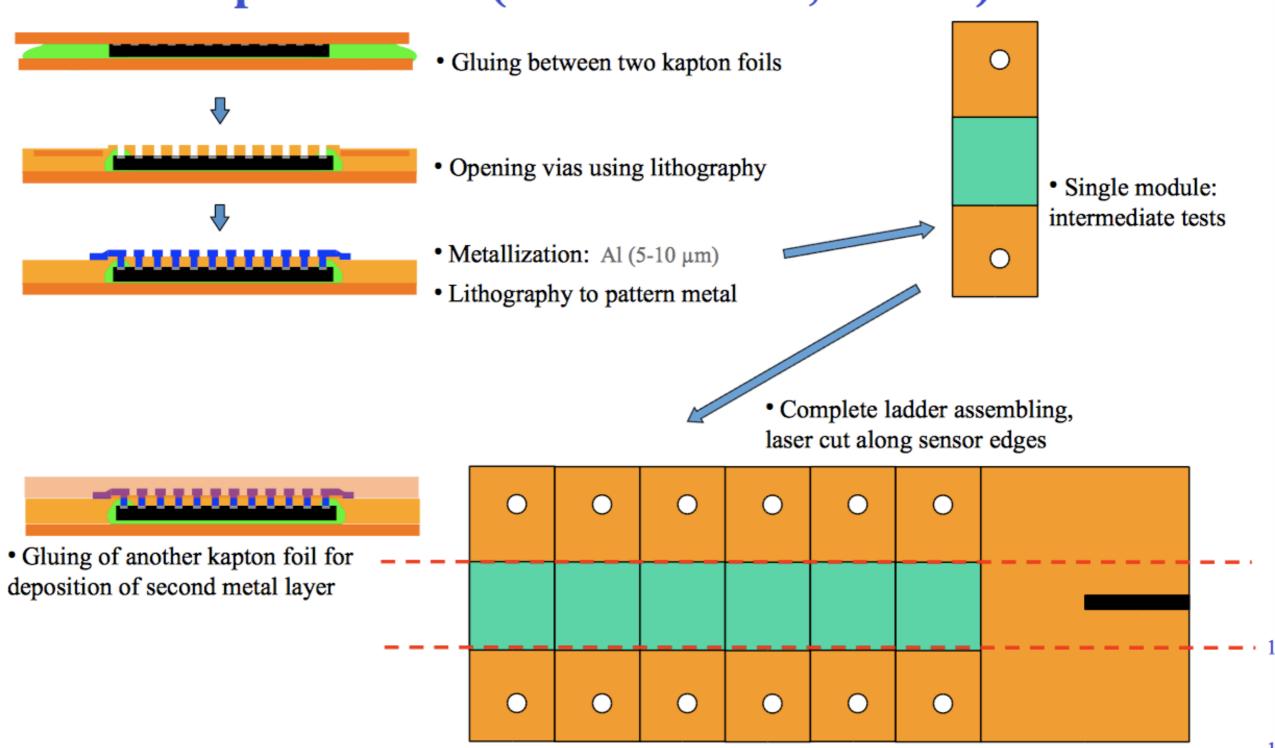

the PLUME project: Pixelated Ladder with Ultra-low Material Embedding collaboration between IPHC Strasbourg, DESY, Oxford and Bristol see: http://www.iphc.cnrs.fr/CMOSILCPLUME.html

- motivation: ILD vertex detector at the ILC

- goal: to achieve by ≥ 2012 a prototype double-layer ladder equipped with CMOS pixel sensors with material budget ≤ 0.3 % X<sub>0</sub>

- → added value of a double-sided layer w.r.t. a single-sided layer?

- design: sensitive area 2x12x1 cm<sup>2</sup>

2x6 MIMOSA-26 thinned down to 50 µm

binary read-out

air cooling

bare support (foam stiffener+flex)

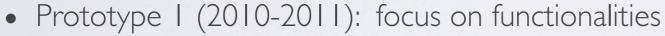

#### sensor integration (2)

- Prototype 0 (2009-2010):

- 2x2 MIMOSA-20 2x4x1 cm<sup>2</sup> sensitive area, 204k pixels

- analog readout

- material budget ~ 0.6 % X<sub>0</sub> (copper cable)

- beam test @ SPS (CERN) with 120 GeV in November 2009:

- → feasibility study and beam test procedure implementation

- 2x6 MIMOSA-26 2x12x1 cm<sup>2</sup> sensitive area, 660k pixels

- digital read-out

- material budget ~ 0.6 % X<sub>0</sub>

- already tested @ IPHC

- work plan:

- · Summer 2011: thermo-mechanical measurements,

- November 2011: beam test @ SPS.

- Prototype 3 (2011-2012): optimised for material budget

- $\sim$  the same as proto-I with material budget  $\sim$  0.3-0.4 %  $\times_0$

- new tool to glue the sensors on the flex with high precision (Fall 2011).

- first ladder ~ Fall 2011, beam test ~ Summer 2012.

STREET, SALE

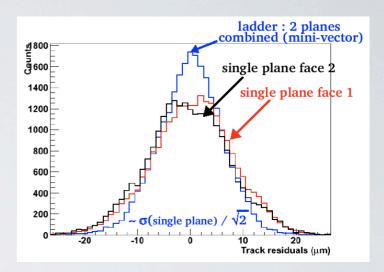

#### alignement and tracking

the AIDA project: Advanced European Infrastructures for Detectors and Accelerators collaboration between IPHC Strasbourg, IRFU Saclay + PLUME see: http://www.iphc.cnrs.fr/AIDA-Project.html

- On-beam test infrastructure:

- Large Area Beam Telescope (LAT, now Single Arm LAT):

EUDET-like Beam Telescope

aim at providing impact positions on DUT with 2 µm resolution

- Alignment Investigation Device (AID): PLUME → 2012-2013

- very thin removable target

- SALAT demonstrator with current sensors (MIMOSA-28 from STAR-PXL)

- → commissioning 2012

Final chips: large active area 5x5 cm<sup>2</sup>, 2500 x2500 pixels with 20x20 μm<sup>2</sup> pitch, based on multi-reticule sensors: **stitching process to be investigated** (advantage of 0.18 μm)

→ expected Summer 2014

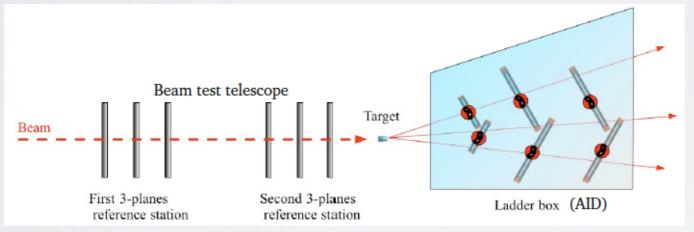

#### detector geometry optimisation

- Estimation of the added value from double-sided layers:

- better pointing accuracy,

- mini-vector could help working under unfavourable conditions (high occupancy rate w.r.t. read-out time),

- combination of time resolution on one side and time resolution on the other side,

- · improved neighbouring hit separation,

- may also help for the alignment.

- especially interesting in high density conditions.

- Importance of the quality from the extrapolated track on the Layer-0, reconstructed with the other layers from the tracker.

- Twofold investigation:

- beam tests with PLUME and AIDA,

- simulations: "super-fastsim", and in the future, physics benchmarks studied within the *a la* SuperB fastsim.

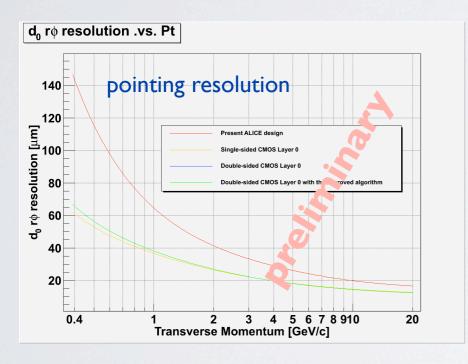

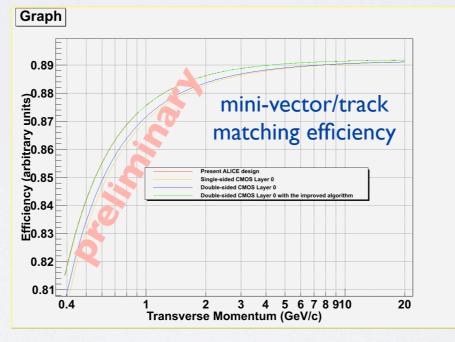

#### detector geometry optimisation (2)

#### fast-estimation tool of a tracker system performances:

tool inherited from STAR (J.Thomas) via our ALICE colleagues.

- Principle:

- easy to calculate  $\sigma_{\mathbb{P}}$  for a track reconstructed with 2 layers:

$$\sigma_{IP}^{2} = \frac{\sigma_{1}^{2} r_{2}^{2} + \sigma_{2}^{2} r_{1}^{2}}{(r_{2} - r_{1})^{2}} + \frac{\theta_{MCS}^{2} r_{1}^{2}}{\sin^{2}\theta}$$

- more complicated with more than 2 measurements

- → P. Billoir method (NIM 225 (1984) 352) based on an outside-in Kalman filter: matrix method [Mult. Cb Scatt.] [Drift] [Measur.] [MCS] [D]

- Given the detector parameters  $(r, x/X_0, \sigma_{s.p.}, t_{r.o.})$  and the collider quantities (background and physics cross-sections, luminosity), we are able to study:

- pointing resolution at collision point,

- transverse momentum resolution,

- efficiency to match a measured point on a given layer to a reconstructed track: to ensure that the hit finding can be done efficiently at each layer in a high hit density environment,

- global vertex detector geometry optimisation: interplay between all layers.

#### detector geometry optimisation (3)

- Example of study (S. Senyukov and J. Baudot, PICSEL group, IPHC Strasbourg):

- study for the ALICE vertex detector upgrade,

- mini-vector with the hits from the double-sided CMOS layers are matched to the reconstructed track rather than only using the 2 measured points separately.

- further investigation varying detector parameters: position of layers, material budget, ....

→ double-sided layer + mini-vector approach interesting for the tracking efficiency.

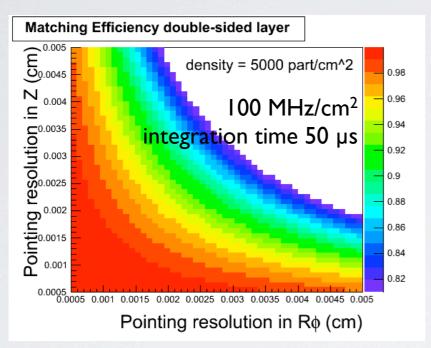

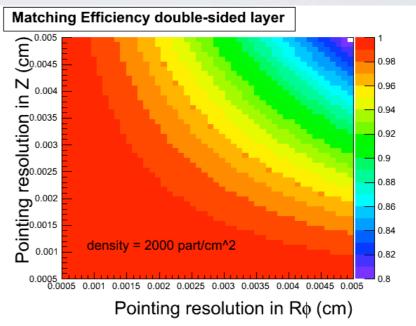

#### detector geometry optimisation (4)

• Added value of mini-vectors from a double-sided layer of CMOS pixel sensors in SuperB: measured-point/extrapolated-track matching efficiency as a function of the total resolution on the extrapolated track, in both directions, for different particle densities.

for instance:  $\sigma_{\text{eff}} \sim 15 \mu \text{m}$  needed in both directions

for instance:  $\sigma_{\text{eff}} \sim 25 \mu \text{m}$  needed in both directions

with

$$\sigma_{\text{eff}} = \sqrt{(\sigma_{\text{extrapolation}}^2 + \sigma_{\text{detector}}^2)}$$

, for instance  $15 = \sqrt{(11^2 + 10^2)} = \sqrt{(14^2 + 5^2)}$

$25 = \sqrt{(23^2 + 10^2)} = \sqrt{(24^2 + 5^2)}$

→ need more investigation but a moderate read-out time may do the work, especially during the first years.

(ALICE note in preparation by J. Baudot and S. Senyukov: "Comparison of hit-track matching efficiency with single-sided and double-sided layers")

#### conclusion

- Strasbourg expresses interest in joining the SuperB collaboration with a twofold contribution:

- hardware developments focused on a vertex detector equipped with CMOS pixel sensors:

- explore 0.18 μm and 3D technologies, focusing on charge collection and pre-amplification, in synergy with INFN,

- → design of the low mass flex cable,

- → architecture of the ladder.

- physics analyses, beginning with studies in relation with the tracking system performances:

- → investigate the asset of a double-sided layer of CMOS pixel sensors,

- → global optimisation of the whole vertex detector (which layer 1?),

- > study the mandatory read-out time in parallel rolling shutter read-out mode.

- Synergy between all developments performed in Strasbourg in the PICSEL group (which is involved in several projects) and SuperB vertex detector developments.

# more information 15

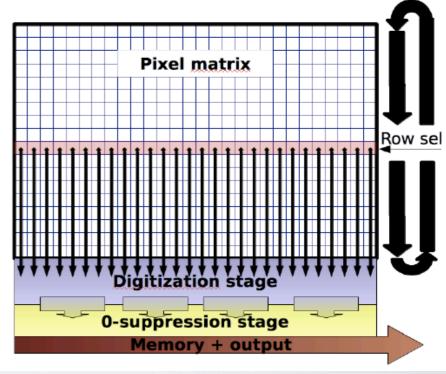

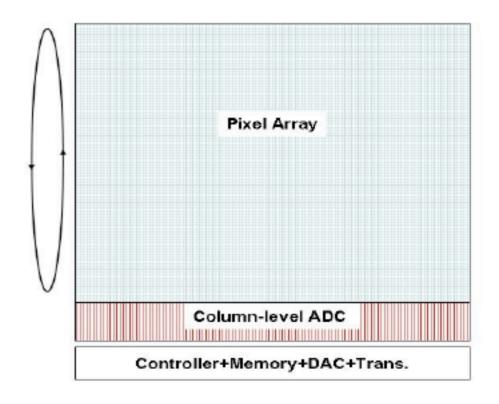

#### **Overview of Rolling Shutter Architecture**

#### Sensor organisation:

- Signal sensing and analog processing in pixel array

- \* Mixed and Digital circuitry integrated in chip periphery

- \* Read-out in rolling shutter mode (pixels grouped in columns read-out in //)

#### Main consequences:

#### \* Read-out speed:

- ≡ integration time

- $\equiv$  nb of pixels  $\times$  pixel read-out time (O(100 ns))

#### \* Power consumption :

limited inside the pixel array to the row being read out

#### \* Material budget:

peripheral band(s) for mixed+digital circuitry, insensitive to impinging particles ( $\sim$  10 % of chip surface)

#### \* Time stamp:

each row corresponds to a specific time intervalle ⇒ adapt track reconstruction code

(courtesy of M. Winter)

#### The CMOS sensor-based VXD

#### Inner layer - internal side

- X Optimized for resolution

- x 16 x 16 μm<sup>2</sup>

- X Q encoding: binary

- x t<sub>Integration</sub> ~40 μs

- ✗ Sensitive area ~ 2 cm²

### Outer layer x Optimize

- Optimized for low power

- x 35 x 35 μm<sup>2</sup>

- x Q encoding: 4-bits

- x  $t_{Integration} \sim 100 \mu s$

- ✗ Sensitive area ~ 4 cm²

#### Inner layer – external side

- X Optimized for r.o. speed

- x 16 x 64 μm<sup>2</sup>

- x Q encoding: binary

- x  $t_{Integration} \sim 10 \ \mu s$

- x Sensitive area ~ 2 cm<sup>2</sup>

| layer | ra dius (mm) | length (mm) | # ladders | # sensors* | #.10 <sup>6</sup> pixels | t <sub>int</sub> (µs) | σ <sub>s.p.</sub> (μm) |

|-------|--------------|-------------|-----------|------------|--------------------------|-----------------------|------------------------|

| 1     | 16/18        | 125         | 14        | 168        | 66 + 16                  | 40 / 10               | < 3                    |

| 2     | 37/39        | 250         | 26        | 312        | 2x112                    | 100                   | < 4                    |

| 3     | 58/60        | 250         | 40        | 480        | 2x173                    | 100                   | < 4                    |

| total |              |             | 80        | 960        | 652                      |                       |                        |

<sup>\*</sup> Numbers corresponding to current CMOS technology (0.35 µm) prototypes

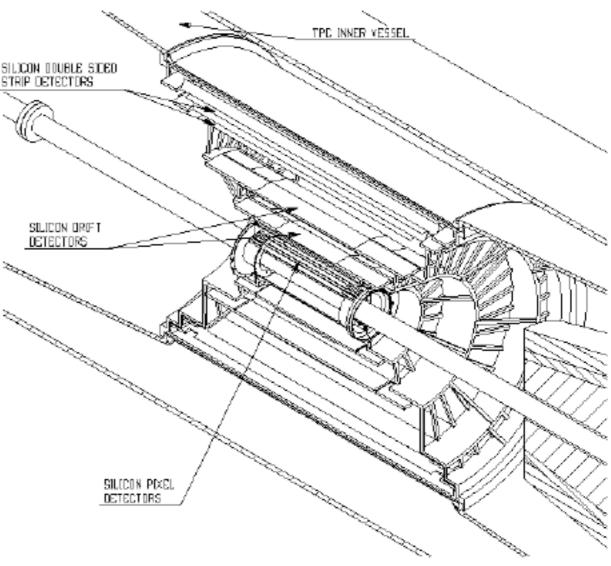

#### **Upgrade of ALICE-ITS**

#### ITS upgrade :

- \* envisionned for "2016" LHC long shutdown

- \* exploits space left by replacement of beam pipe with small radius (19 mm) section

- \* consists (at least) in introducing L0

- $\equiv$  additionnal layer at  $\lesssim$  25 mm radius (potentially : replace part of the ITS)

- \* 2 pixel otions considered :

- Hybrid pixels with reduced material budget & pitch

- CMOS pixel sensors derived from STAR-PXL (ULTIMATE)

- \* main characteristics of CMOS option :

- ♦ double-sided ladder derived from PLUME (< 0.5 % X<sub>0</sub>)

- $\diamond \lesssim$  50  $\mu s$  read-out time

- $\diamond \sim$  4  $\mu m$  spatial resolution

- $\diamond~>$  1 MRad & 10  $^{13} \rm n_{\it eq} / cm^2$  at T = 30  $^{\circ} \rm C$  (target values)

- $\hookrightarrow$  move to 0.18  $\mu m$  technology

## "standard" PCB process for chip embedding in plastic foils (R. de Oliveira, CERN)